Chapter 6

- 摘要:主要涉及了触发器相关设计及其运用、状态的概念以及触发器电路的设计,时钟(CLK)的控制、同步时序逻辑电路设计、大量的verilog设计代码与电路实现。

- 重点:逻辑抽象,如何建立状态表和化简,根据状态表如何选择电路元件类型,如何得到次态方程,激励方程和输出方程,如何画出电路图。

- 答案更正:6-5:少了一个编码为(11)的情况;6-6:C如果输入1,状态还是(111)不改变

-

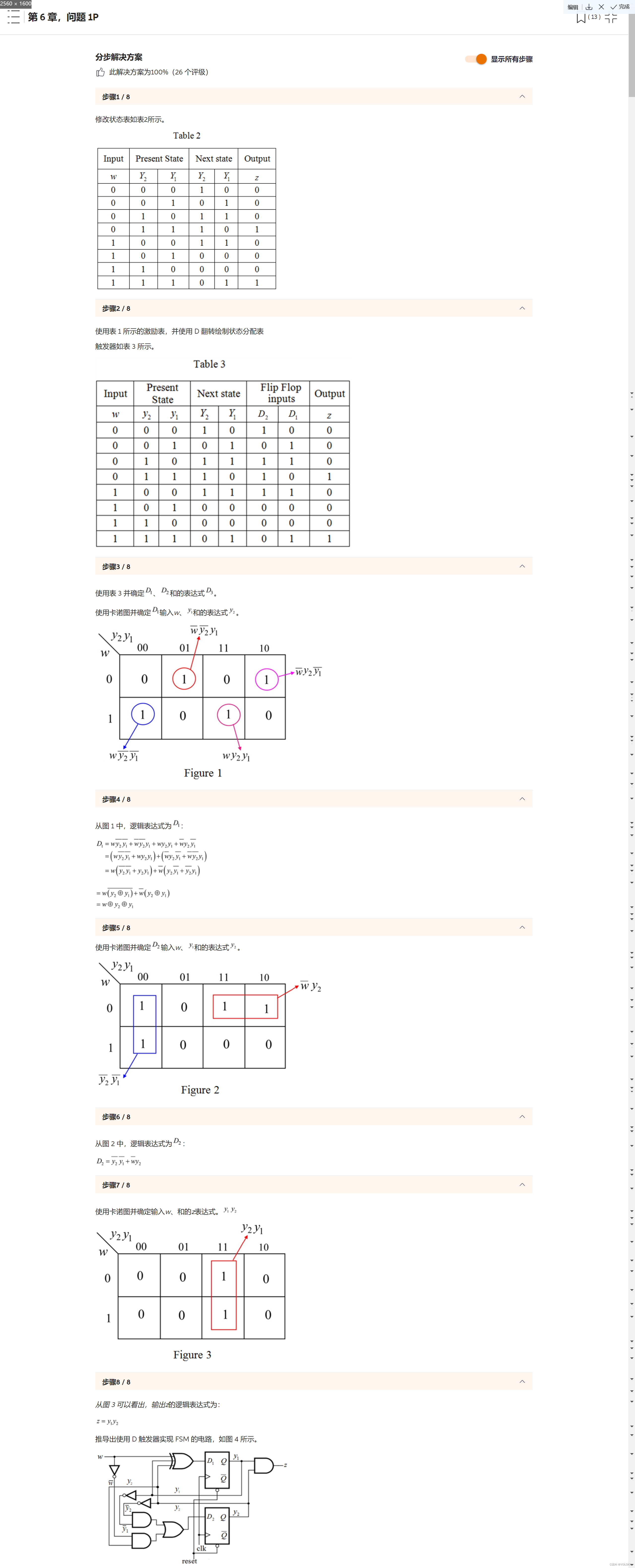

Chapter 6, Problem 1P

-

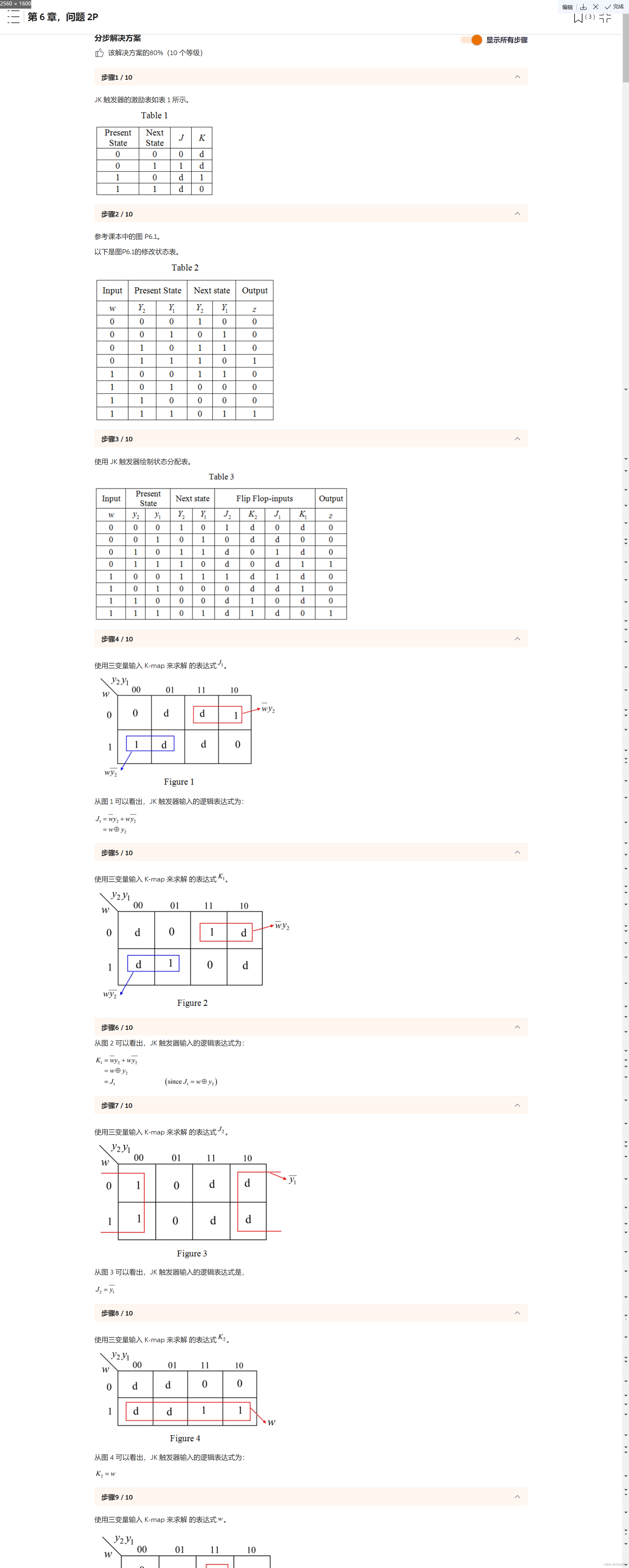

Chapter 6, Problem 2P

-

Chapter 6, Probl

本章深入探讨了触发器设计、状态机构建和同步时序逻辑电路。主要内容包括逻辑抽象、状态表简化、时钟控制、次态方程和电路实现。还指出了Chapter 6部分习题的解答错误,并提供了多个问题的解决方案。

本章深入探讨了触发器设计、状态机构建和同步时序逻辑电路。主要内容包括逻辑抽象、状态表简化、时钟控制、次态方程和电路实现。还指出了Chapter 6部分习题的解答错误,并提供了多个问题的解决方案。

订阅专栏 解锁全文

订阅专栏 解锁全文

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?