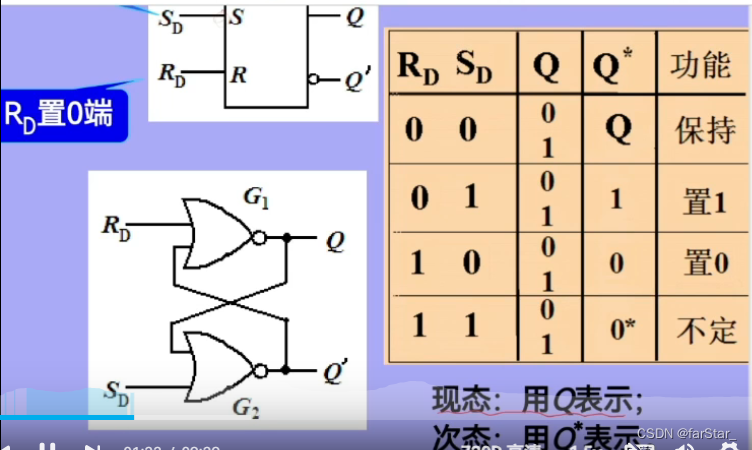

〇、RS锁存器

看图,无圈,高电平有效。

看图,无圈,高电平有效。

S:置一,R:置零。如果都为1,就不定(实际Q和Q'通通规定为1);都为0,就保持。

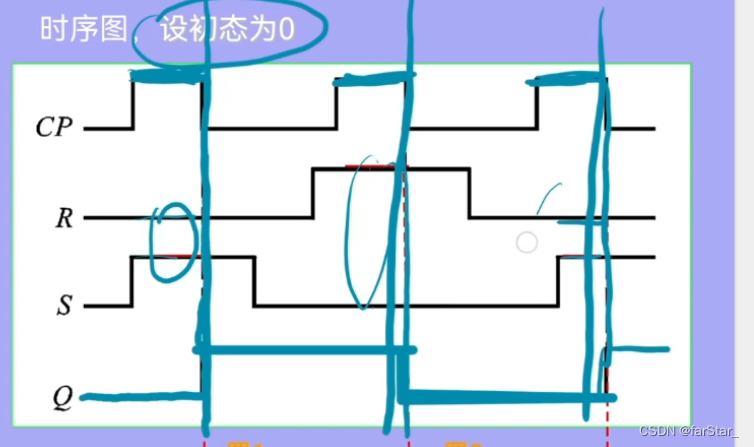

很简单吧。现在打起精神来!!看看这个倒霉的图,我们的目标就是看懂右边是怎么画出来的!

揭秘:RD'和SD'是输入条件,正下边的Q和Q’就是由RS所影响产生0和1

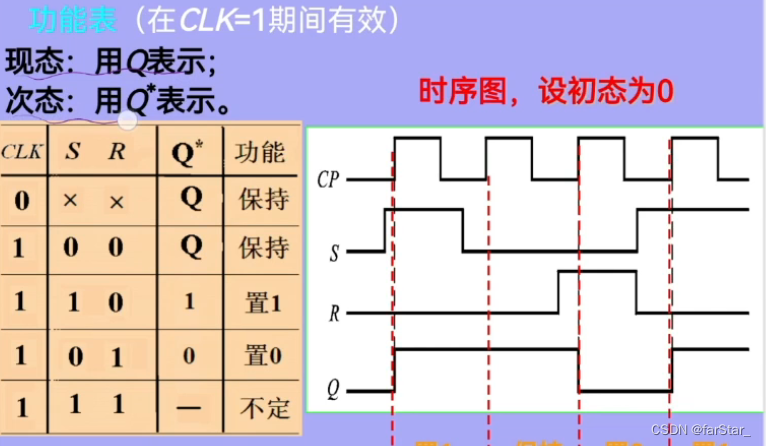

一、电平触发的触发器

1.RS

说白了就是多了个CLK(也写作CP)

这个错位是怎么回事捏?哦!原来是因为S到1时CP还没有到1,所以Q不变。

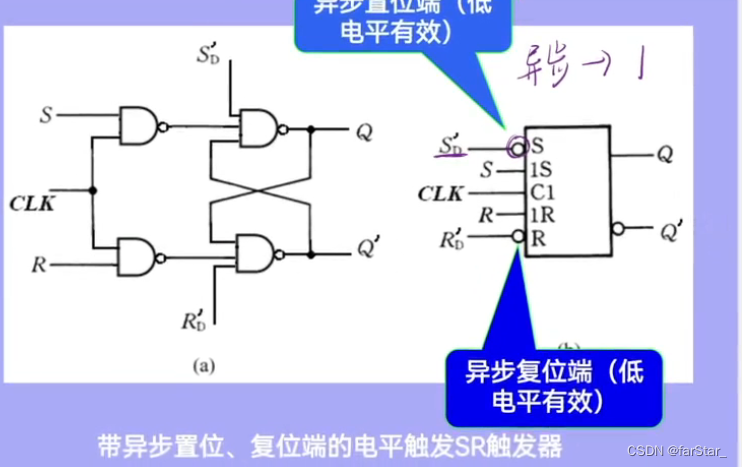

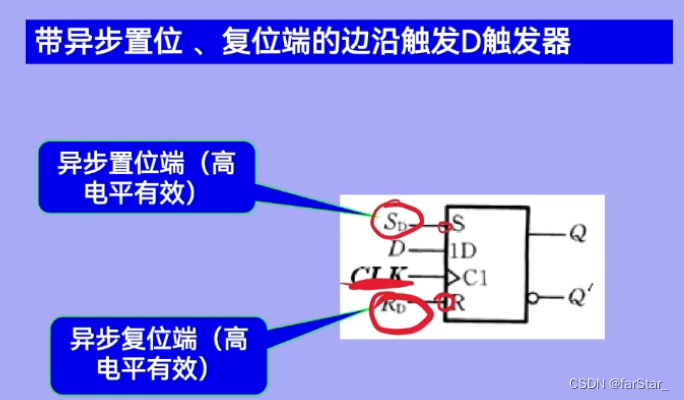

我们再加两个输入,分别是异步置位(置一)端和异步复位(置零)端(都是低电平有效)

好,那么问题来了,什么是异步?以及,加这两个输入端有什么作用?

异步复位不依赖于时钟(不受CLK控制)

这两个输入可以摆布Q

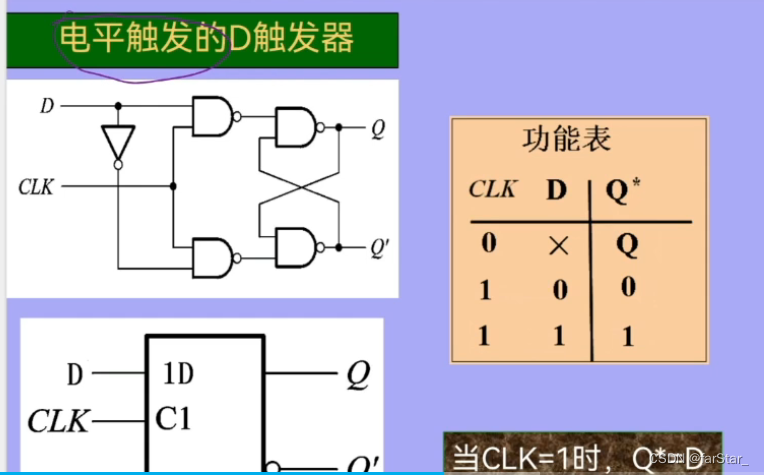

2.电平触发的D触发器

CLK=1时,Q*就等于D

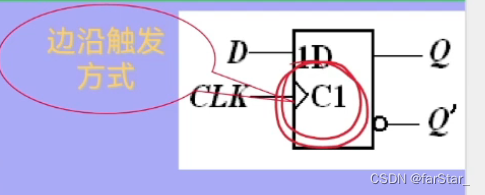

二、边沿触发的触发器:靠脉冲上升沿/下降沿触发

1.D触发器

C1旁边的小三角表明是边沿触发。

没有圈圈代表是上升沿触发。

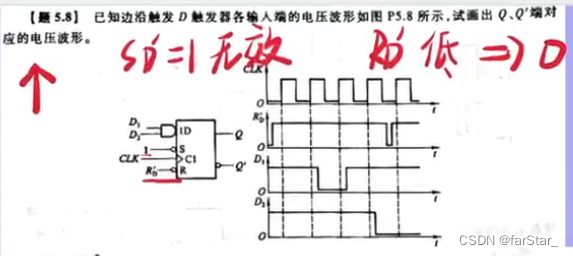

例如这道题,要考虑异步复位端(RD’)不受时钟控制,变0时候(有效了)Q也变0(被置零)。

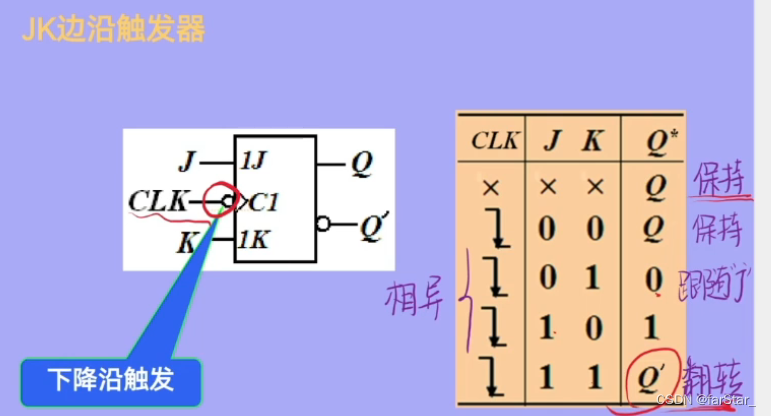

2.边沿JK触发器

和D/RS相比,JK算是复杂的了。如何记住呢?

J和K不一样的时候,Q和J一样;

JK同为0,保持,JK同为1,反转。

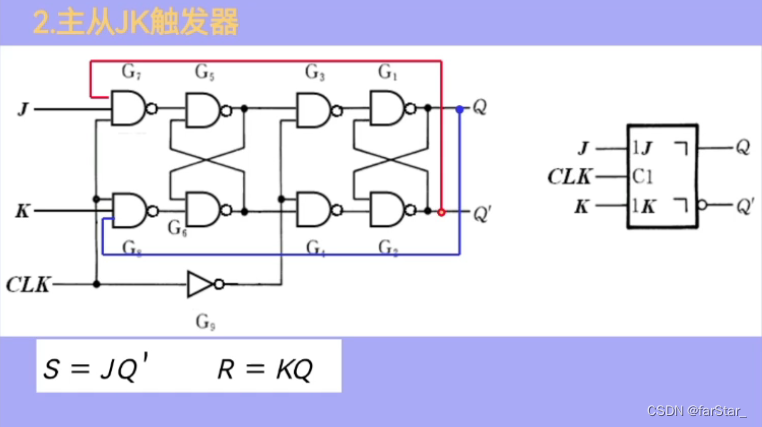

三、脉冲触发的触发器

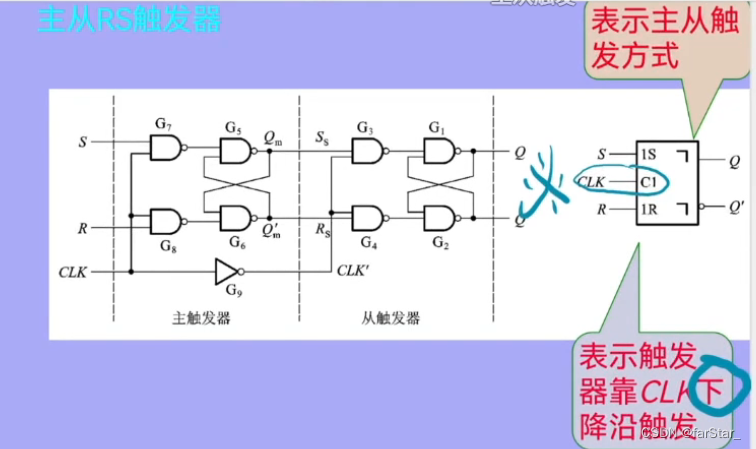

1.主从RS触发器

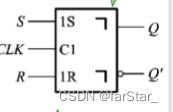

图上有两个:“7”代表脉冲触发

图上有两个:“7”代表脉冲触发

脉冲触发是把电平触发和边沿触发的特点综合在一起了

脉冲触发和电平/边沿相反!有圈是高电平触发,没有圈是低电平触发。

下面这个图比较复杂,不要慌!待我细细讲来

(除了有7,和电平触发很像哈(

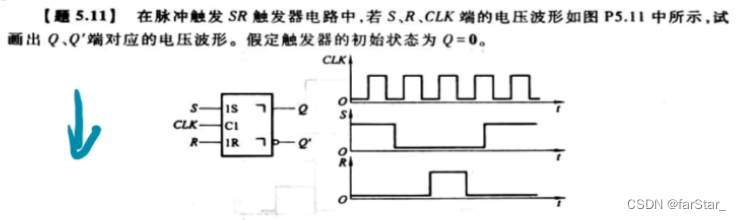

这道题,没有圈,下降沿触发,Q的状态取决于,CL K等于1期间R和S的状态。

来个例题:

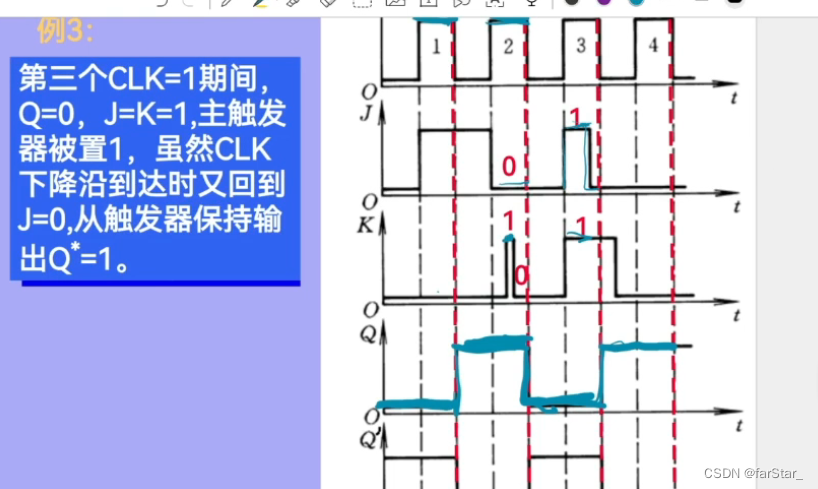

2.脉冲触发的JK触发器

一样的,就记一下JK,00时候保持,不同时候和J一样,都是1翻转

注意,有尖峰脉冲的,就看尖尖是几就好

例如这个,第一个1那里,CLK等于1这一段,只看尖尖是1、1,所以在下降沿那里翻转

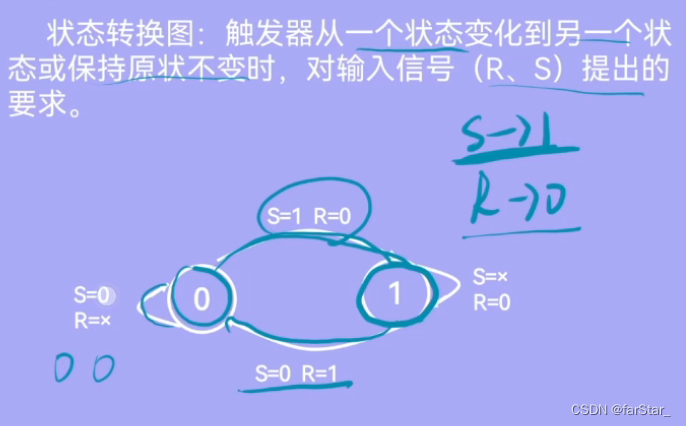

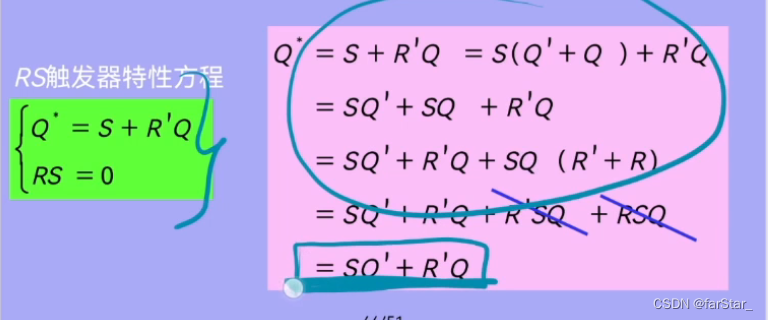

四、触发器的特性方程(需要记忆)

1.RS触发器

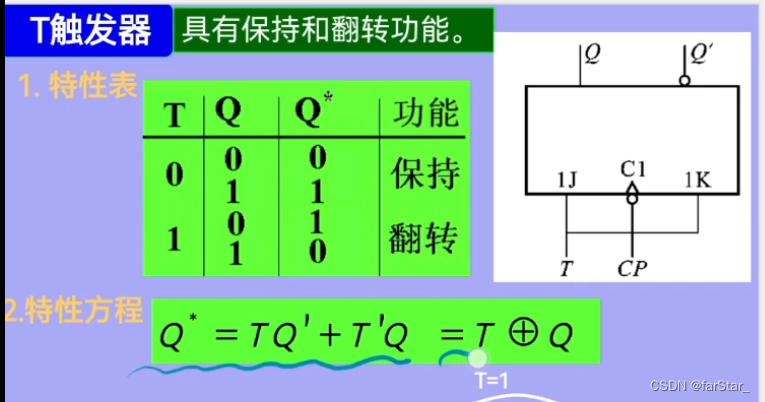

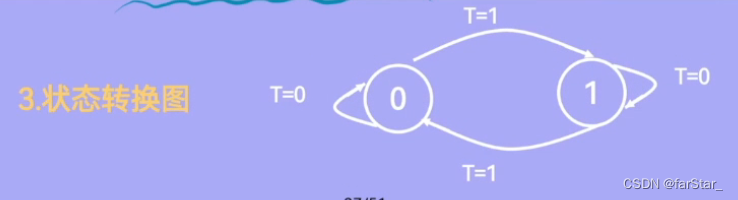

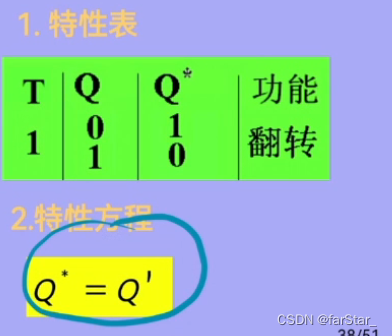

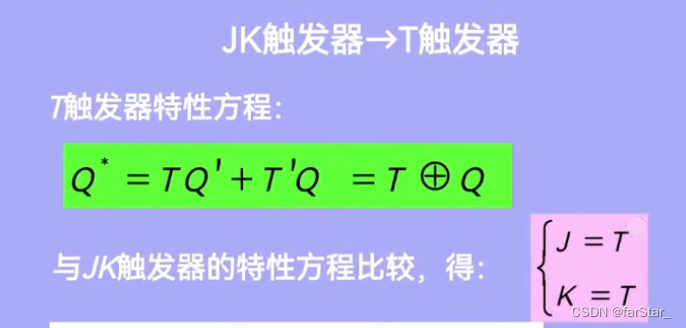

2.T触发器,0保持,1翻转

T'触发器:T=1时候的触发器(又叫做计数型触发器,每来一个时钟脉冲,T'就翻转一次,显然能实现计数功能

3.D触发器

Q*=D

4.JK触发器

Q*=JQ'+K'Q

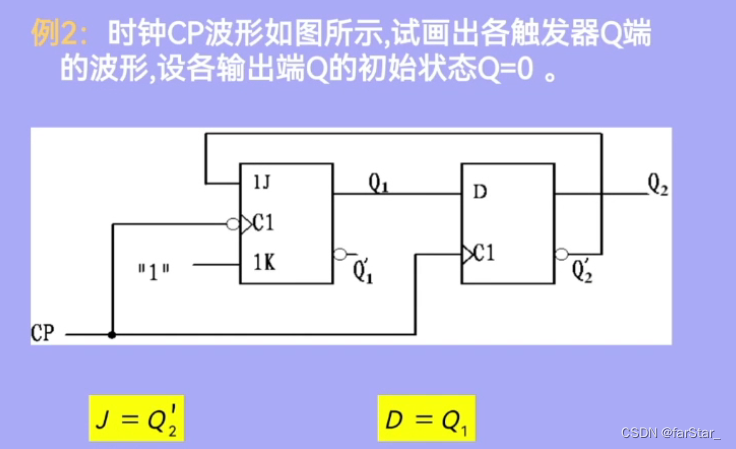

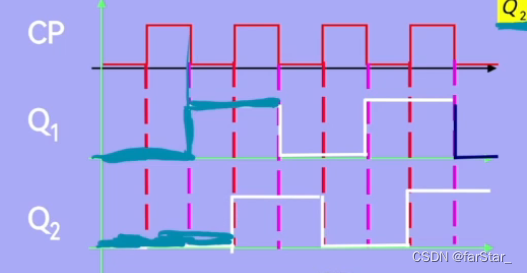

例题:

这题一开始没做出来,原因:写完Q1*和Q2*的方程都是Q1'Q2',不知道从哪里入手了

原因:Q2*不是Q2'Q1',也就是说不是Q1*,而是Q1

Q1Q2要同时分析

五、触发器之间的转换

1.JK->RS

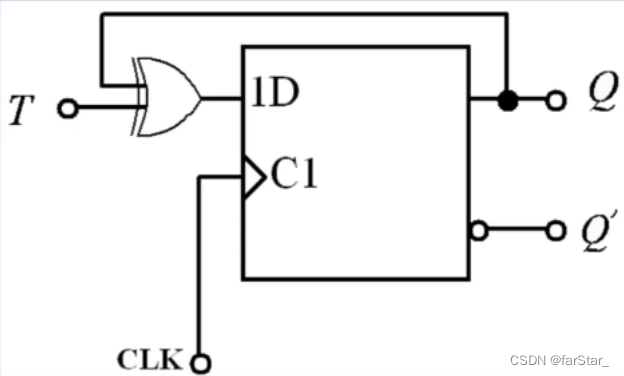

2.JK->T

3.D->T

4.D->T'

总结:

小三角:边沿触发

两个7:脉冲触发(高低有效是反的)

一般情况下,加小圆圈:低电平有效触发或者下降沿有效触发

RS锁存器,直接电平触发,没有CLK

同步触发:CLK的高低电平期间触发

边沿触发(CLK的上或者下边沿)

主从触发:CLK等于1期间,受RS或者JK控制

上面四个加粗的标题是按照结构分类的四种触发器。而按照逻辑可分为:SR/JK/D/T和T'

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?