在微控制器系统中,时钟信号发挥着核心作用,它驱动着芯片内部各功能模块按照预定时序执行指令操作,其重要性可类比为生物体的心脏搏动。作为一款高性能微控制器,STM32系列芯片集成了丰富的外设资源,其架构设计具有显著的复杂性。需要特别指出的是,所有外设模块的正常运作都必须依赖时钟信号的驱动,然而不同外设对时钟频率的需求存在显著差异。若统一采用高速时钟驱动所有外设,不仅会导致能源效率低下,还会引发一系列问题。

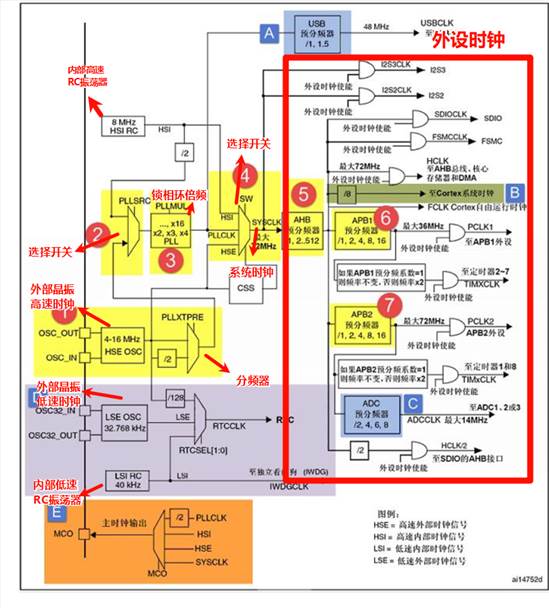

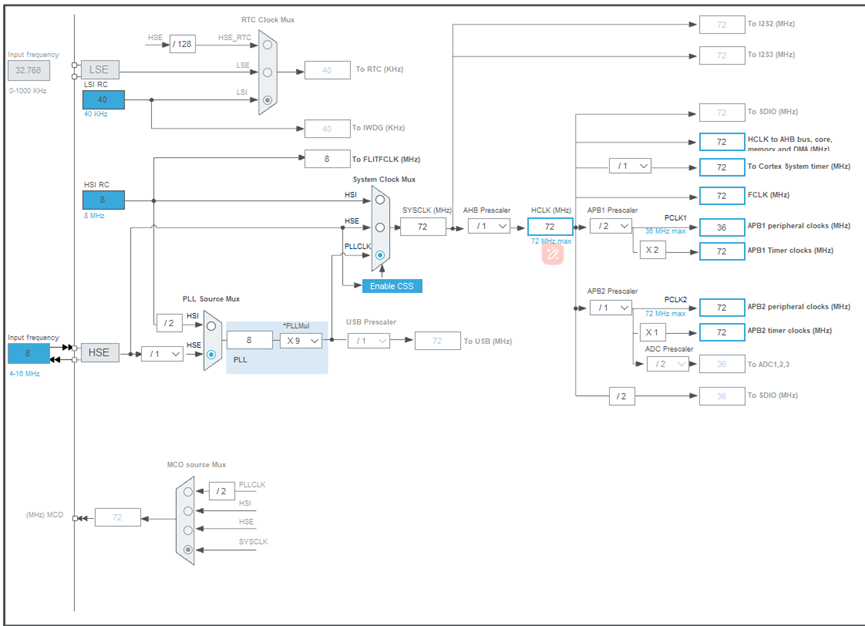

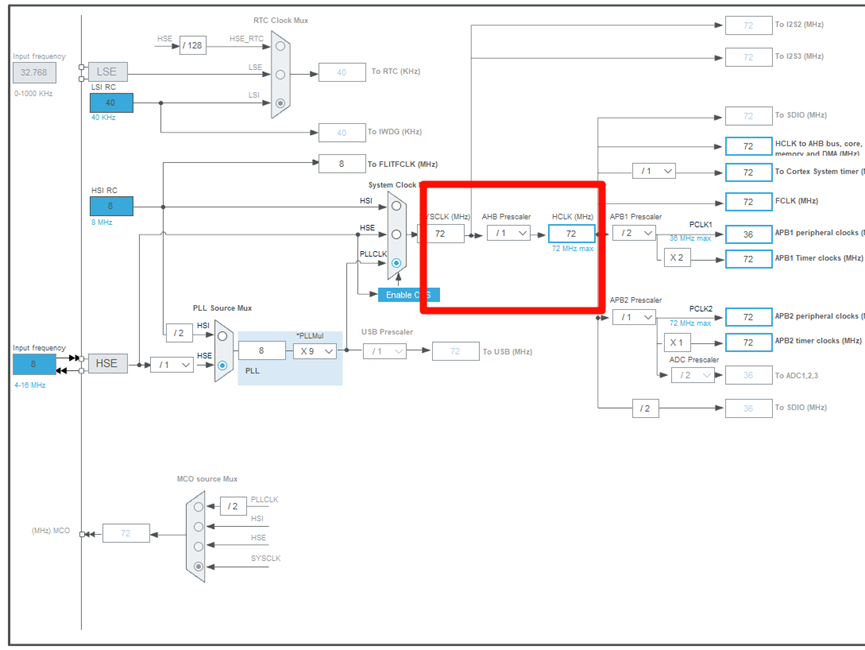

从电路特性角度分析,时钟频率的提升会带来三个主要影响:首先,系统功耗将呈指数级增长;其次,电路的电磁兼容性能会明显下降;此外,信号完整性也面临更大挑战。为有效应对这些技术难题,现代复杂微控制器普遍采用多时钟源架构设计方案。这种设计通过为不同功能模块提供差异化的时钟频率,实现了性能与能效的最佳平衡。附图展示了STM32芯片时钟系统的结构框图,清晰地呈现了这一设计理念的具体实现方式。

如上图左边的部分,看到STM32有4个独立时钟源,HSI、HSE、LSI、LSE。

HSI是高速内部时钟,RC振荡器,频率为8MHz,精度不高。

HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

LSI是低速内部时钟,RC振荡器,频率为40kHz,提供低功耗时钟。

LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

时钟树的右边红色框中,则是系统时钟通过AHB预分频器,给相对应的外设设置相对应的时钟频率。

其中LSI、LSE是作为IWDGCLK(独立看门狗)时钟源和RTC时钟源使用。而HSI、HSE以及PLLCLK经过分频或者倍频作为系统时钟SYSCLK来使用。

PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。通过倍频之后作为系统时钟的时钟源。

配置时钟

默认时钟

Keil编写程序是默认的时钟为72Mhz,其实是这么来的:

外部高速晶振HSE提供的8MHz(大小与电路板上的晶振相关)通过PLLXTPRE分频器后,进入PLLSRC选择开关,进而通过PLLMUL锁相环进行倍频(x9)后,为系统提供72MHz的系统时钟SYSCLK。之后是AHB预分频器对时钟信号进行分频,然后为低速外设提供时钟。

内部RC振荡器HSI为8MHz,2分频后是4MHz,进入PLLSRC选择开关,通过PLLMUL锁相环进行倍频(最大x16)后为64MHz。

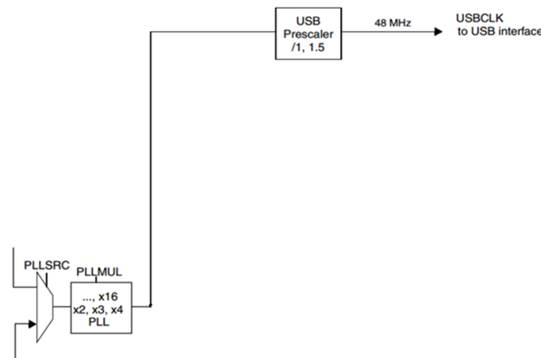

USB时钟

如上图,STM32的USB时钟不能超过48MHz,因此如果时钟源为72MHz,就需要进行1.5分频。

如果时钟源为48MHZ,则进行1分频即可。

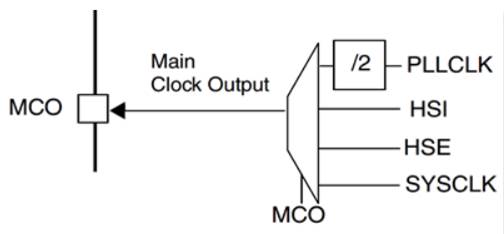

把时钟信号输出到外部

STM32可以选择一个时钟信号输出到MCO脚(PA8)上,可以选择为PLL输出的2分频、HSI、HSE、或者系统时钟,可以把时钟信号输出供外部使用。

AHB分频器

如时钟树图右边的部分,系统时钟通过AHB分频器给外设提供时钟。从左到右可以简单理解为:

系统时钟->AHB分频器->各个外设分频倍频器->外设时钟的设置。

右边部分为:系统时钟SYSCLK通过AHB分频器分频后送给各模块使用,AHB分频器可选择1、2、4、8、16、64、128、256、512分频。其中AHB分频器输出的时钟送给5大模块使用:

内核总线:送给AHB总线、内核、内存和DMA使用的HCLK时钟。

Tick定时器:通过8分频后送给Cortex的系统定时器时钟。

I2S总线:直接送给Cortex的空闲运行时钟FCLK。

APB1外设:送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出一路供APB1外设使用(PCLK1,最大频率36MHz),另一路送给通用定时器使用。该倍频器可选择1或者2倍频,时钟输出供定时器2-7使用。

APB2外设:送给APB2分频器。APB2分频器可选择1、2、4、8、16分频,其输出一路供APB2外设使用(PCLK2,最大频率72MHz),另一路送给高级定时器。该倍频器可选择1或者2倍频,时钟输出供定时器1和定时器8使用。另外,APB2分频器还有一路输出供ADC分频器使用,分频后送给ADC模块使用。ADC分频器可选择为2、4、6、8分频。需要注意的是,如果APB预分频器分频系数是1,则定时器时钟频率(TIMxCLK)为PCLKx。否则,定时器时钟频率将为 APB 域的频率的两倍:TIMxCLK = 2xPCLKx。

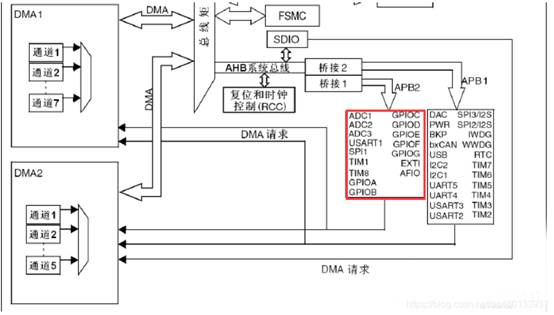

APB1和APB2的对应外设

F1系列中,APB1上面连接的是低速外设,包括电源接口、备份接口、CAN、USB、I2C1、I2C2、USART2、USART3、UART4、UART5、SPI2、SP3等。

APB2上面连接的是高速外设,包括UART1、SPI1、Timer1、ADC1、ADC2、ADC3、所有的普通I/O口(PA-PE)、第二功能I/O(AFIO)口等。

具体可以在stm32f10x_rcc.h中查看外设挂在哪个时钟下。

时钟监视系统(CSS)

另外,STM32还提供了一个时钟监视系统(CSS),用于监视高速外部时钟(HSE)的工作状态。倘若HSE失效,会自动切换(高速内部时钟)HSI作为系统时钟的输入,保证系统的正常运行。

二、如何STM32CubeMX配置时钟树

我们配置步骤如下

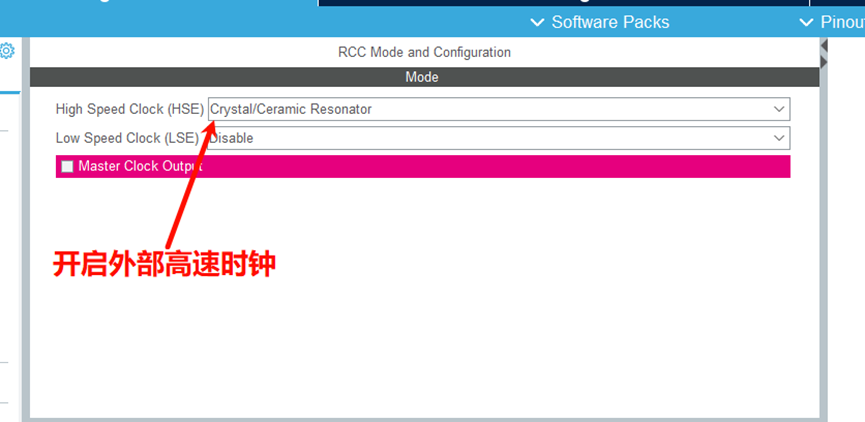

1. 选择和配置时钟源

确定使用内部(HSI)还是外部(HSE)高速时钟源。通常,HSE提供更精确的时钟频率。

如果使用HSE,确保外部晶振已正确连接并工作。

在STM32CubeMX中,选择“Clock Configuration”选项卡,设置HSE为ON,并选择合适的启动时钟源。

2. 配置PLL(锁相环)

根据系统需求配置PLL的倍频和分频参数,以生成所需的系统时钟频率(SYSCLK)。

在STM32CubeMX中,设置PLL的输入源(HSE或HSI)、倍频因子和分频因子。

3. 设置系统时钟(SYSCLK)

选择PLL作为系统时钟源,并设置PLL输出作为SYSCLK。

在STM32CubeMX中,确保“System Clock Switch”设置为“PLL”

4. 设置AHB分频因子(HCLK)

AHB总线时钟(HCLK)通常等于或小于SYSCLK。设置AHB分频因子以确定HCLK的频率。

在STM32CubeMX中,设置“AHB Prescaler”以调整HCLK相对于SYSCLK的比例。

5. 设置APB2分频因子(PCLK2)

APB2总线时钟(PCLK2)可以是HCLK的1倍或2倍。设置APB2分频因子以确定PCLK2的频率。

在STM32CubeMX中,设置“APB2 Prescaler”以调整PCLK2相对于HCLK的比例。

6. 设置APB1分频因子(PCLK1)

APB1总线时钟(PCLK1)可以是HCLK的1倍、2倍或4倍。设置APB1分频因子以确定PCLK1的频率。

在STM32CubeMX中,设置“APB1 Prescaler”以调整PCLK1相对于HCLK的比例。

7. 配置外设时钟

根据外设需求配置其时钟源和分频因子。例如,USART、ADC、TIM等外设可能需要特定的时钟设置。

在STM32CubeMX中,可以在“Pinout & Configuration”选项卡中配置外设的时钟源和分频因子。

三、时钟树的组成

1.时钟源

STM32F1系列微控制器的输入时钟源包含HSI、HSE、LSI和LSE。外部时钟源通过连接外部晶振来获取,而内部时钟源则在芯片上电后自动产生,无需外部电路辅助。

高速外部振荡器 HSE (High Speed External Clock signal)

该时钟信号由外部高频振荡电路产生,支持有源晶体和无源晶体两种连接方式,工作频率范围为4MHz至16MHz。有源晶体方案仅需连接OSC_IN引脚,而无源方案需要同时连接OSC_IN和OSC_OUT引脚,并配置适当的匹配电容。工程实践中,8MHz无源晶体是最常用的配置方案。

低速外部振荡器 LSE (Low Speed External Clock signal)

该模块通常外接32.768kHz石英晶体,主要为实时时钟(RTC)模块提供基准时钟。值得注意的是,RTC时钟也可选择由高速外部时钟128分频或低速内部时钟提供。

高速内部振荡器 HSI(High Speed Internal Clock signal)

采用片内RC振荡电路实现,标称频率为8MHz。由于RC振荡器的固有特性,其频率稳定性受温度变化影响显著,因此通常不作为锁相环的参考时钟输入。

低速内部振荡器 LSI(Low Speed Internal Clock signal)

同样基于内部RC振荡器实现,工作频率为40kHz,主要应用于独立看门狗定时器的时钟需求。

2.锁相环模块

STM32的锁相环电路具备双重功能:时钟信号调理和频率合成。前者通过闭环反馈机制实现时钟净化,后者则用于生成稳定的高频时钟信号。该模块支持两个参考时钟输入源:高速外部时钟或高速内部时钟的二分频信号。考虑到频率稳定性要求,工程实践中通常选择高速外部时钟作为参考源。

3. 核心时钟系统

作为微控制器的时序基准,系统时钟可为芯片各功能模块提供同步信号。其时钟源可选自高速内部时钟、锁相环输出或高速外部时钟。通过合理配置锁相环参数,系统时钟最高可设置为72MHz。需要说明的是,虽然采用高速内部时钟方案理论上可获得64MHz主频(8MHz/2×16),但为充分发挥STM32F103C6T6芯片性能,建议采用锁相环方案实现72MHz标称工作频率。从数字电路特性来看,提高时钟频率能显著提升指令吞吐量,但需综合考虑功耗和电磁兼容性等因素。

4. 时钟监测与输出

微控制器时钟输出(MCO)功能可将内部时钟信号引至特定引脚,实现外部时钟监测或为其他器件提供参考时钟。该功能支持四种时钟源选择:系统时钟、高速内部时钟、高速外部时钟以及锁相环二分频输出。除作为辅助时钟源外,该功能还可用于系统时钟配置的验证工作,通过示波器观测输出波形即可确认时钟配置的正确性。

简单创建一个CubeMX工程(STMF103常用)

CubeMX配置:

- 开启外部高速时钟

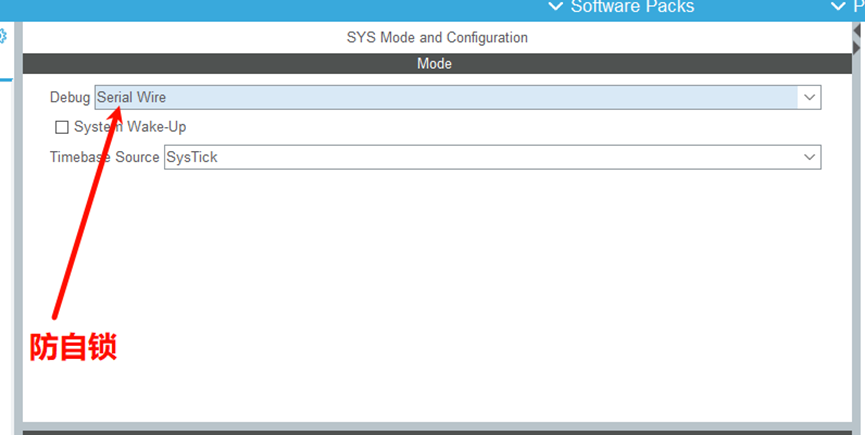

- 设置SYS的Debug为Serial Wire

- 配置时钟树(荐最高主频72Mhz)

④工程相关配置

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?