DVP(Digital Video Port)接口详解

DVP(Digital Video Port)是一种并行数字视频接口,常用于摄像头(CMOS Sensor)与主控(SOC/FPGA)之间的数据传输。其特点是接口简单、带宽较低,适用于中低分辨率图像传输(如720p以下)。

1. DVP 信号组成及作用

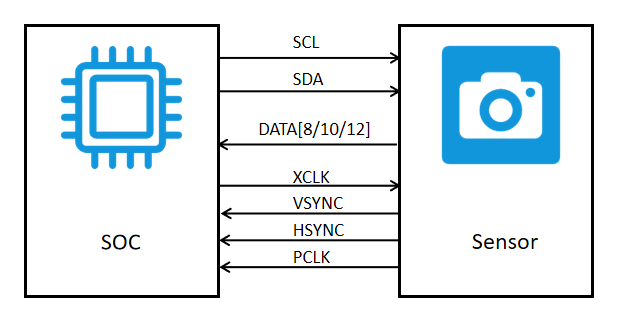

DVP 接口通常包含以下信号:

| 信号 | 方向 | 作用 |

|---|---|---|

| PCLK | 输出 | 像素时钟,每个上升/下降沿对应一个像素数据(如48MHz)。 |

| MCLK/XCLK | 输入 | 传感器外部时钟输入(如24MHz),由主控或晶振提供。 作用:为 Sensor 提供基准时钟,用于内部 PLL 分频生成 PCLK、HSYNC、VSYNC 等信号。 |

| VSYNC | 输出 | 帧同步信号,每帧开始时产生一个脉冲(如30Hz)。 |

| HSYNC | 输出 | 行同步信号,每行开始时产生一个脉冲(如15KHz)。 |

| D[0:11] | 输出 | 并行数据线(8/10/12bit),每个PCLK周期传输一个像素数据。 |

图1 sensor接线图(SCL和SAD是IIC通信线)

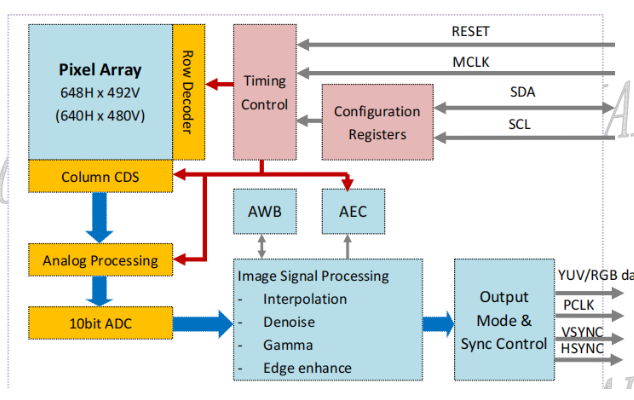

图2 sensor模块图

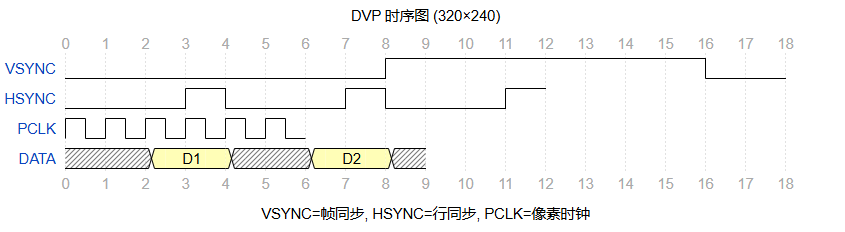

2. DVP 数据传输时序

以 320×240 分辨率 为例:

-

帧开始(VSYNC):

• VSYNC 脉冲(低/高电平)表示新一帧开始。• 主控检测到 VSYNC 后,准备接收新帧数据。

-

行传输(HSYNC + PCLK):

• 每行开始时,HSYNC 脉冲(低/高电平)表示新行开始。• 每行包含 320 个 PCLK 周期,每个 PCLK 对应一个像素数据(D[0:11])。

• 行结束后,HSYNC 再次触发,进入下一行。

-

帧结束(VSYNC):

• 传输完 240 行 后,VSYNC 再次触发,表示帧结束,重新开始下一帧。

时序示例(低电平有效):

VCLK:帧同步信号,低电平有效,每帧触发一次

HCLK:行同步信号,低电平有效,每行触发一次

PCLK:像素时钟,上升沿采样数据

3. DVP 关键配置

(1) PCLK(像素时钟)

• 由 Sensor 输出,SOC 无需设置频率,只需适配其速率(如48MHz)。

• PCB 设计优化:

• 包地处理:减少 PCLK 对其他信号的干扰。

• 源端端接(串联电阻 + 电容):减少信号过冲和振铃。

(2) MCLK/XCLK(外部时钟输入)

• 由主控或晶振提供(如24MHz),需符合 Sensor 规格书要求。

• 常见频率:24MHz、48MHz(取决于 Sensor 型号)。

(3) HSYNC/VSYNC 极性

• 由 Sensor 决定,SOC 需匹配其极性(低电平有效 / 高电平有效)。

• 如何确定极性?

• 查阅 Sensor 手册(如 OV5640 的 HSYNC_POL / VSYNC_POL 寄存器)或iic读取

• 用示波器测量实际信号。

(4) 数据位宽(D[0:11])

• 可以是 8/10/12bit,需与 Sensor 输出格式匹配(如 RGB565、YUV422)。

• SOC 端需配置相同位宽,否则会导致数据错位。

4. DVP 带宽计算

DVP 的传输带宽取决于:

• 分辨率(如 320×240)

• 帧率(如 30fps)

• 数据位宽(如 8bit)

计算公式:带宽 (bps)=水平像素×垂直像素×帧率×数据位宽

示例:

• 320×240 @ 30fps,8bit 数据 →

320×240×30×8=18.432Mbps

• 实际带宽更高(需考虑消隐区,通常增加 20%~30%)。

DVP 适用场景:

• 低分辨率(如 VGA 640×480)

• 低帧率(≤ 60fps)

• 对带宽要求不高的嵌入式设备

5. 常见问题及调试

(1) 图像错位 / 撕裂

• 可能原因:

• HSYNC/VSYNC 极性配置错误。

• PCLK 采样边沿不匹配(上升沿 vs 下降沿)。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?