移位寄存器是一种数字电路,用于将输入数据按照特定的规则进行移位操作。它通常由触发器(Flip-Flop)组成,并通过时钟信号来控制数据的移位操作。

基本的移位寄存器有三种类型:串行入串行出(SISO)、并行入串行出(PISO)和并行入并行出(PIPO)。下面我将详细介绍这些类型的工作原理:

-

串行入串行出(SISO)移位寄存器:

SISO移位寄存器有一个输入端和一个输出端,数据按顺序从输入端进入,然后根据时钟信号,逐位地移至输出端。每个时钟脉冲都会使得数据往下一个位置移动一位。 -

并行入串行出(PISO)移位寄存器:

PISO移位寄存器具有多个输入端和一个输出端。输入端的数据通过并行方式同时进入移位寄存器的各个存储单元中,然后根据时钟信号,逐个存储单元将数据移至输出端。每个时钟脉冲都会使得数据往下一个位置移动一位。 -

并行入并行出(PIPO)移位寄存器:

PIPO移位寄存器具有多个输入端和多个输出端,输入端的数据通过并行方式同时进入移位寄存器的各个存储单元中,并且输出端的数据也可以同时从各个存储单元中读出。时钟信号控制着数据的移位和读取。

移位寄存器在数字电路中有广泛的应用,例如数据序列操作、数据传输、时序分析等。它们能够以高速、高效的方式进行数据的移位和存储,对于很多数字系统来说是非常重要的组件之一。

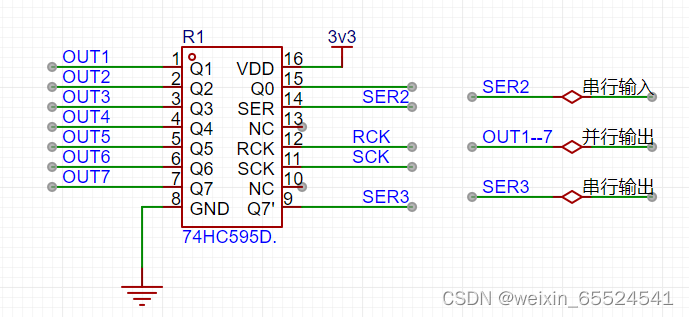

注:移位寄存器的SCK和RCK该怎么接?

SCK和RCK分别是移位寄存器中的时钟信号输入端和控制信号输入端,它们的具体接法取决于具体的应用场景和移位寄存器类型。

对于串行入串行出(SISO)移位寄存器,SCK和RCK通常被连接到同一个时钟源上。每当时钟信号SCK发生一个上升沿时,数据就会从输入端进入移位寄存器,并且在下一个上升沿时向左移动一位。RCK控制着数据从移位寄存器输出端取出的时间,当RCK发生上升沿时,数据就可以从输出端读取。

对于并行入串行出(PISO)移位寄存器,SCK仍然被用来控制数据移位,但是RCK则用来选择要从哪个存储单元中读取数据。因此,RCK通常需要连接到一个多路选择器(MUX)的控制端上。

对于并行入并行出(PIPO)移位寄存器,SCK和RCK都需要用来控制数据的移位和读取。因此,它们通常需要连接到不同的时钟源上,或者使用一个复合时钟信号来控制。

总之,SCK和RCK的具体接法需要根据移位寄存器的类型和具体的应用场景来确定,需要仔细阅读相关的数据手册和应用指南,并进行正确的接线以确保移位寄存器的正常工作。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?