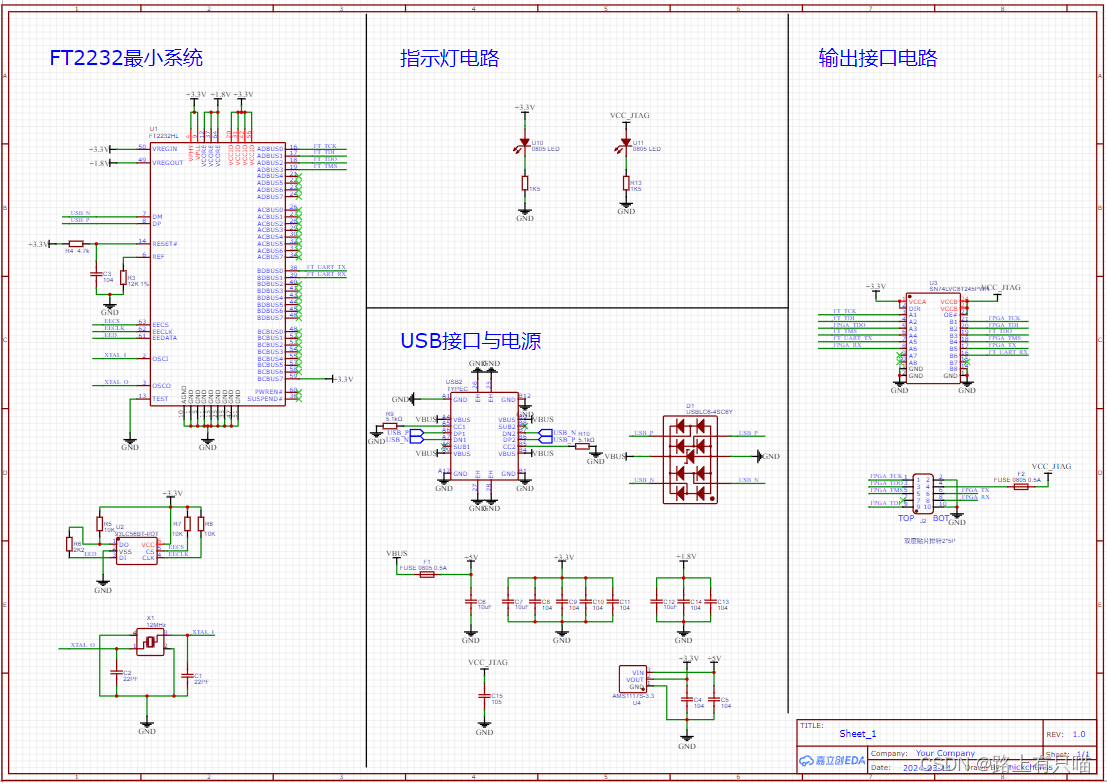

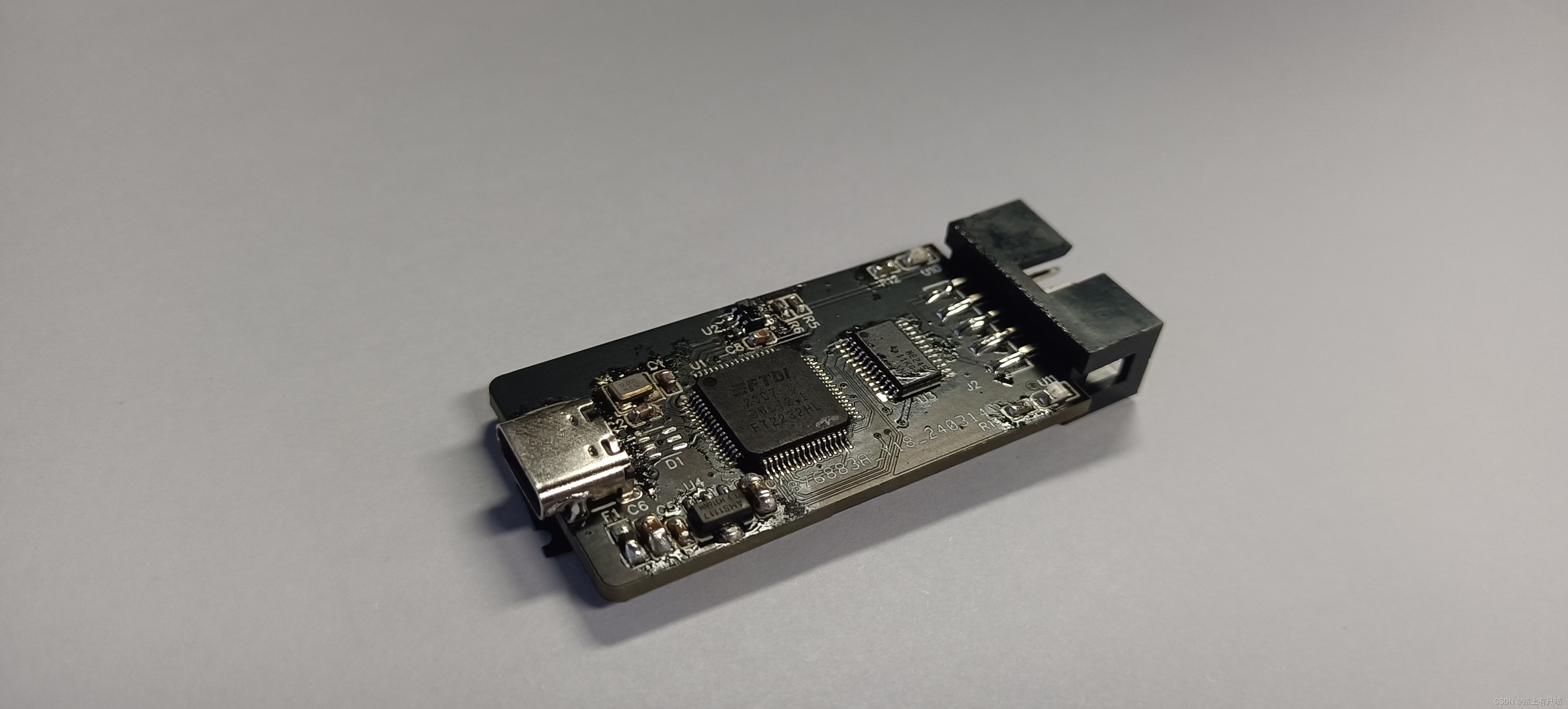

简介:自制Xilinx JTAG下载器,主要芯片为FT2232HL,Typec供电与通信,10PIN 2.54接口输出,转出1路JTAG信号,1路UART信号。

前言

Xilinx的调试器,轻微魔改了xilinx标准线序,jtag线序兼容xilinx原厂接口。 支持30M的速度与最高2000000波特率的串口。

一、原理图

二、PCB实物

烧录参考下面链接:

基于FT2232集成USB直接实现XilinxJTAG和UART串口_program_ftdi-CSDN博客

三、测试视频

xilinx FPGA开发使用本产品下载LED流水灯视频

总结

自制Xilinx JTAG下载器,主要芯片为FT2232HL,Typec供电与通信,10PIN 2.54接口输出,转出1路JTAG信号,1路UART信号。支持30M的速度与最高2000000波特率的串口。

原工程见:基于FT2232H的XilinxFPGA - 硬创社

或者关注公众号路上有只喵 回复 基于FT2232H的XilinxFPGA 获取

1334

1334

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?