8位二进制加法器构成的以时序方式设计的乘法器

通过逐项移位相加原理来实现。用乘数的各位数码,从低位开始依次与被乘数相乘,每相乘一次得到的积称为部分积,将第一次(由乘数最低位与被乘数相乘)得到的部分积右移一位并与第二次得到的部分积相加,将加得的和右移一位再与第三次得到的部分积相加,再将相加的结果右移一位与第四次得到的部分积相加。直到所有的部分积都被加过一次即可得到相应的乘积。

设计原理如图所示

仿真软件使用的是Quartus II和Modelsim的联合仿真功能,语言用的是VHDL语言描述电路单元

软件下载在b站上找,直接搜Quartus II联合仿真就行,对着视频安装

以下是控制器代码部分

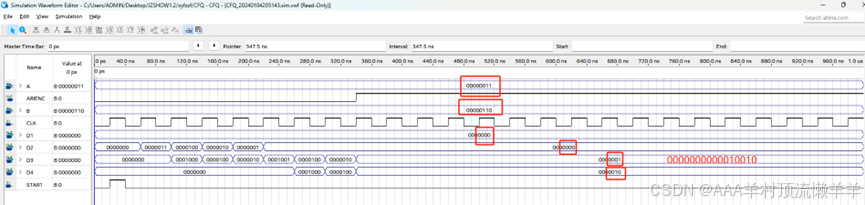

结果仿真

整个文件包含论文,每个模块解析,还有代码及仿真文件,把他资源放在本站下载

571

571

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?