一、实验目的

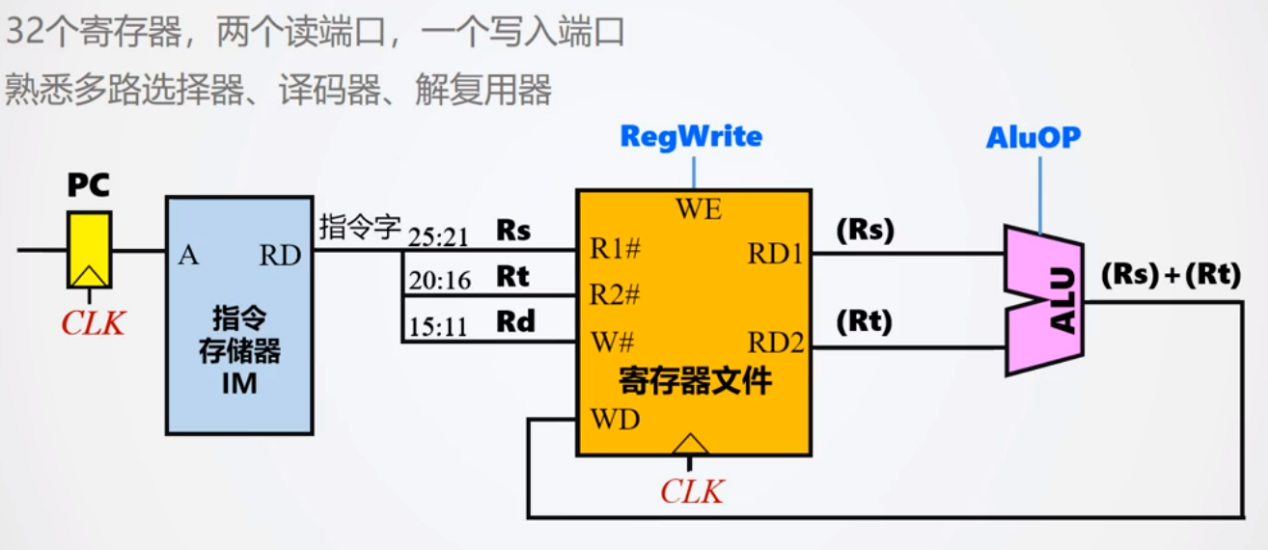

1.了解寄 MIPS 寄存器文件基本概念,进一步熟悉多路选择器、译码器、解复用器等 Logisim 组件的使用,并利用相关组件在Logisim平台中设计实现 MIPS 寄存器文件。

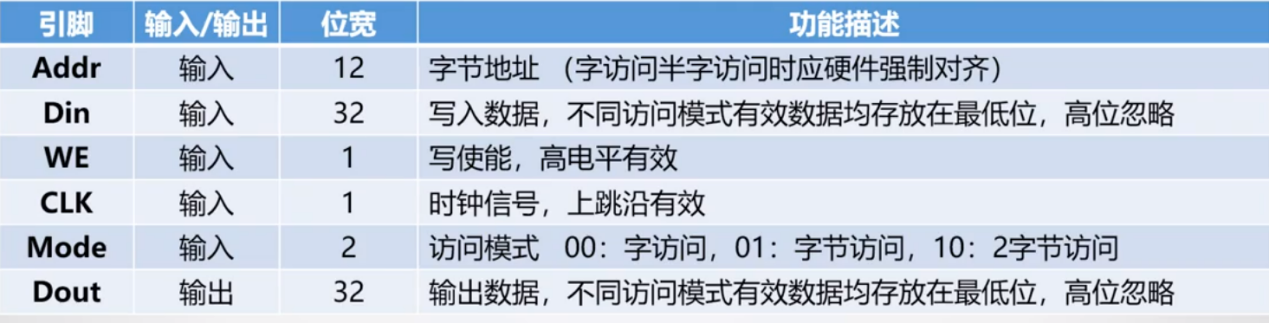

2.理解主存地址基本概念,理解存储位扩展基本思想,并能利用相关原理在Logisim平台中设计实现 MIPS RAM文件。

3.掌握硬布线控制器设计的基本原理,能利用硬布线控制器的设计原理在Logisim平台中设计实现MIPS单周期CPU。

二、实验内容

1.实现MIPS寄存器文件设计

2.实现MIPS RAM设计

3.绘制MIPS CPU数据通路

4.实现单周期硬布线控制器

三、实验原理

MIPS,全称为Microprocessor Without Interlocked Pipeline Stages,是一种基于RISC(Reduced Instruction Set Computing)体系结构的处理器架构。它最早由斯坦福大学的John Hennessy和他的团队开发,最初用于设计高性能的工作站和服务器的中央处理单元(CPU)。

MIPS架构强调指令集精简、流水线执行,尽可能减少指令的长度和种类,从而提高处理器执行指令的效率。MIPS指令集的设计着重于让处理器更高效地执行大量简单指令,而不是复杂的指令。MIPS指令集的设计也非常清晰简单,方便了处理器的实现和软件的开发。

MIPS处理器具有良好的性能、可靠性和可伸缩性,已经被广泛应用于嵌入式系统、网络设备和消费电子等领域。MIPS处理器性能优异、功耗低、体积小,是物联网智能设备和人工智能等领域的重要技术支持。

MIPS处理器中有32个通用寄存器,其中每个寄存器的宽度为32位。这些寄存器是用来存储程序中的数据和地址的,可以用来存储整数型数据、指针型数据和内存地址等等。这32个寄存器使用的命名方式为$0 - $31,$0寄存器特殊一些,不能被写入。

MIPS寄存器提供了一个写端口和多个读端口。通常情况下,MIPS寄存器中有一个写端口和两个读端口,分别用于读取寄存器中的两个不同的数据。但是,一些MIPS处理器可能会提供更多的读端口。 值得注意的是,当多条指令同时需要从同一个寄存器中读取数据时,这些指令必须按照特定的顺序来执行,以确保每个指令都能够得到正确的寄存器值。否则,如果执行顺序不当,则可能会导致程序出现错误。

MIPS RAM指的是MIPS处理器可寻址的随机存储器(Random Access Memory),也就是处理器中用于存储数据和指令的主内存。MIPS处理器通过RAM来实现数据和指令的读写,并且RAM中的数据可以被CPU随机访问。

MIPS RAM通常由多个存储单元组成,每个存储单元可以存储一定大小的数据,通常是8位或16位或32位。MIPS处理器使用地址总线向RAM传递地址信息,再使用数据总线向RAM传送数据,以实现数据的读取和写入。

MIPS RAM是非常重要的内存组件,因为它直接影响着MIPS处理器的性能和速度。高速、高效的RAM能够提高CPU读写数据的速度,从而加快程序的运行速度。同时,在MIPS处理器的设计中,还需要考虑RAM容量和数据带宽等因素,以保证CPU能够快速读取和处理复杂的程序。

单周期CPU指的是计算机处理器的一种执行模型,其中每个指令都会在一个时钟周期内完成执行。因此,每条指令被分成几个固定的阶段,每个阶段只需一个时钟周期。当一条指令的每个阶段都完成后,CPU才会转移到下一条指令。单周期CPU的执行过程通常包括以下几个阶段:

1. 指令读取:从指令存储器中读取指令,并将其存储在指令寄存器中。

2. 指令解码:对指令进行解码,以确定指令类型、操作数和操作类型。

3. 操作数读取:从寄存器文件或者内存中读取操作数,存储在指定的寄存器中。

4. 操作执行:根据指令类型和操作数,执行具体的操作,例如算术运算和逻辑运算。

5. 结果存储:将操作的结果存储在寄存器文件或者内存中,以备之后的使用。

单周期CPU的实现相对简单,易于理解和实现。但是,它的性能受到许多因素的限制,例如在单条指令中必须等待所有阶段完成才能转移到下一条指令,不能同时执行多条指令,效率较低,不适合处理具有复杂数据依赖性的程序。因此,现代CPU通常采用更高效的多周期CPU或流水线CPU来提高处理器性能。

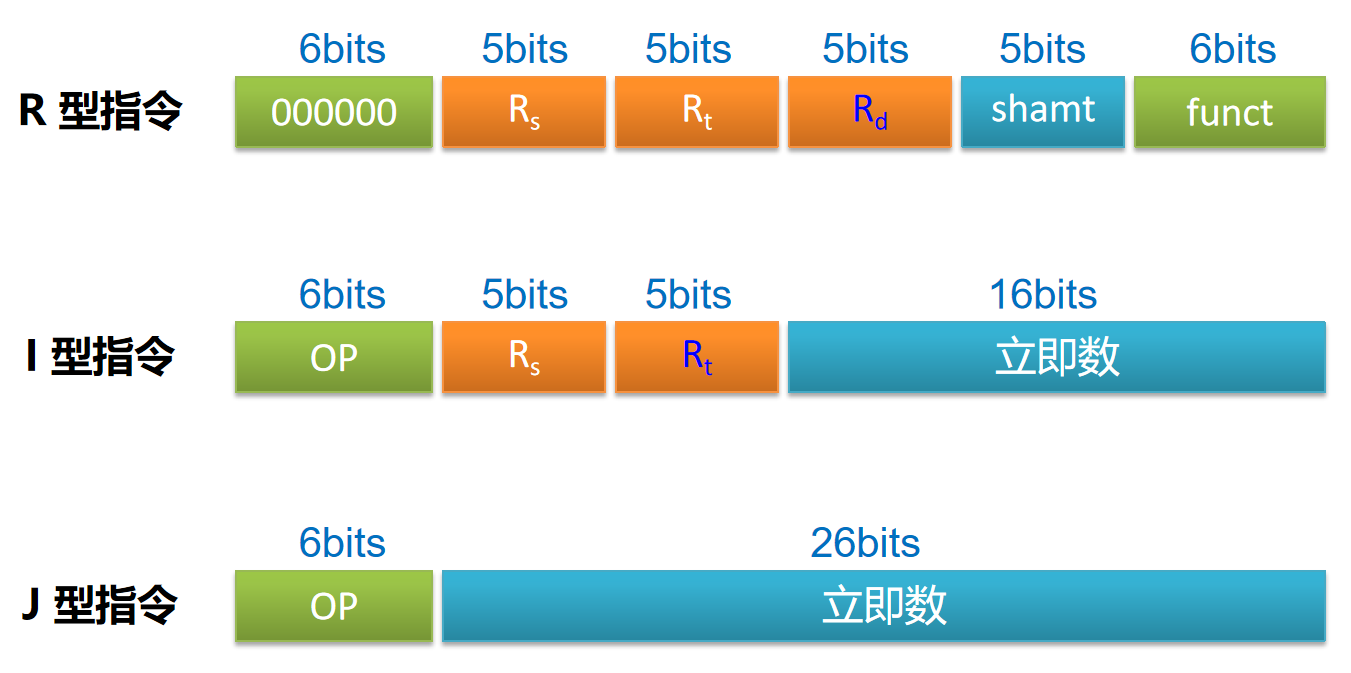

MIPS指令分为R型,I型和J型指令:

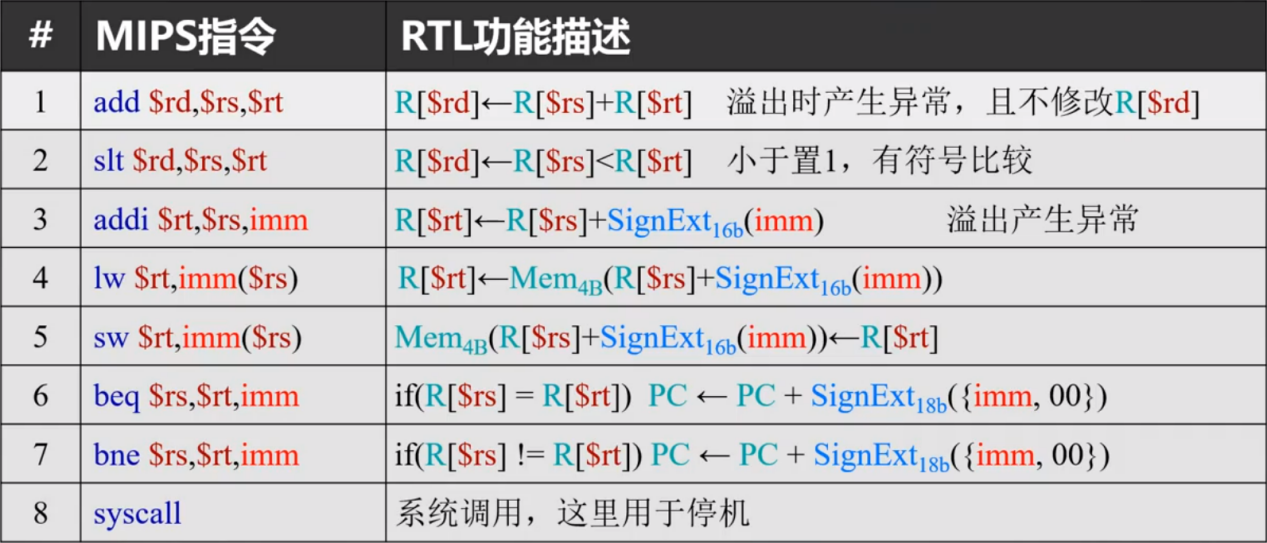

MIPS指令集如下:

四、实验过程

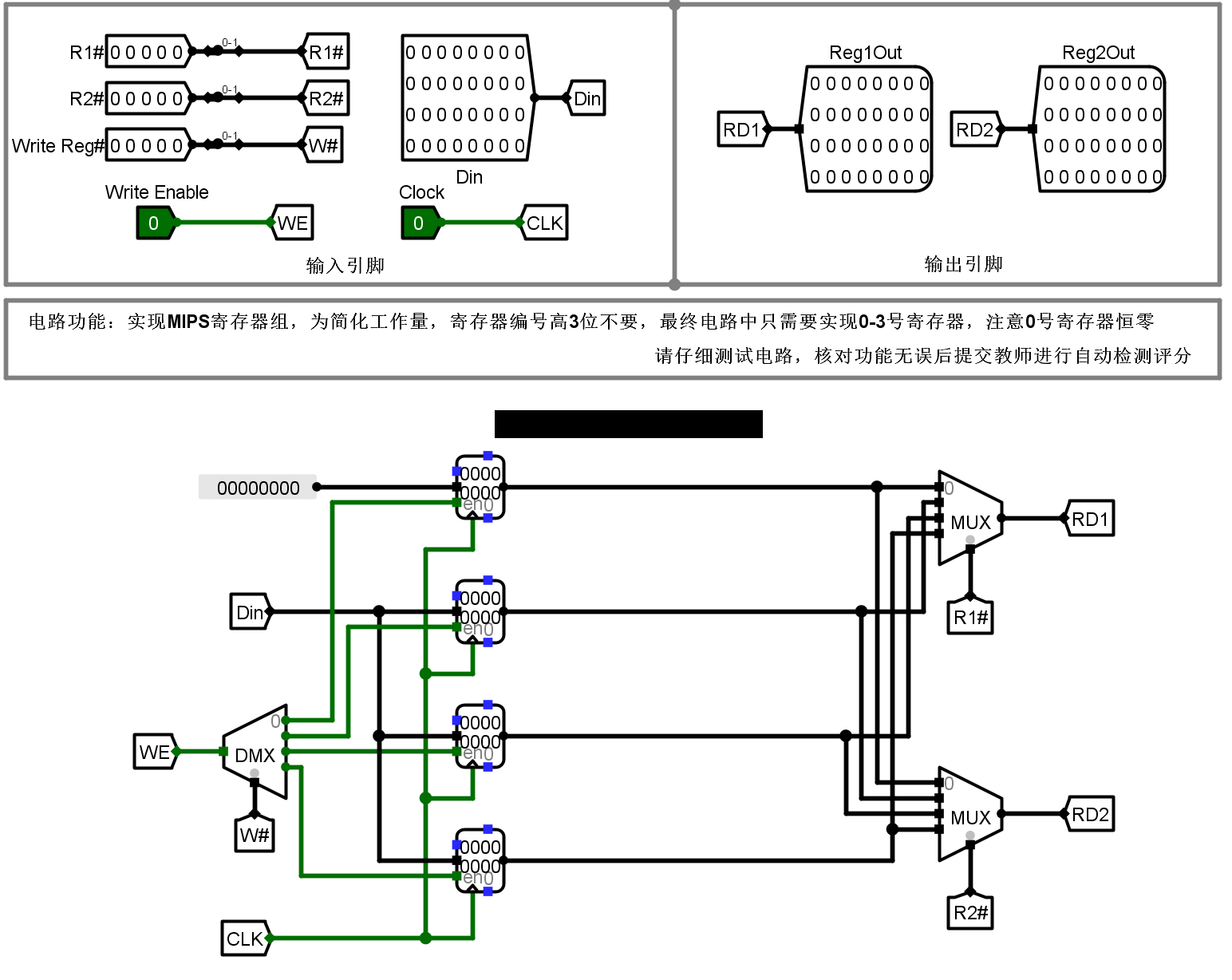

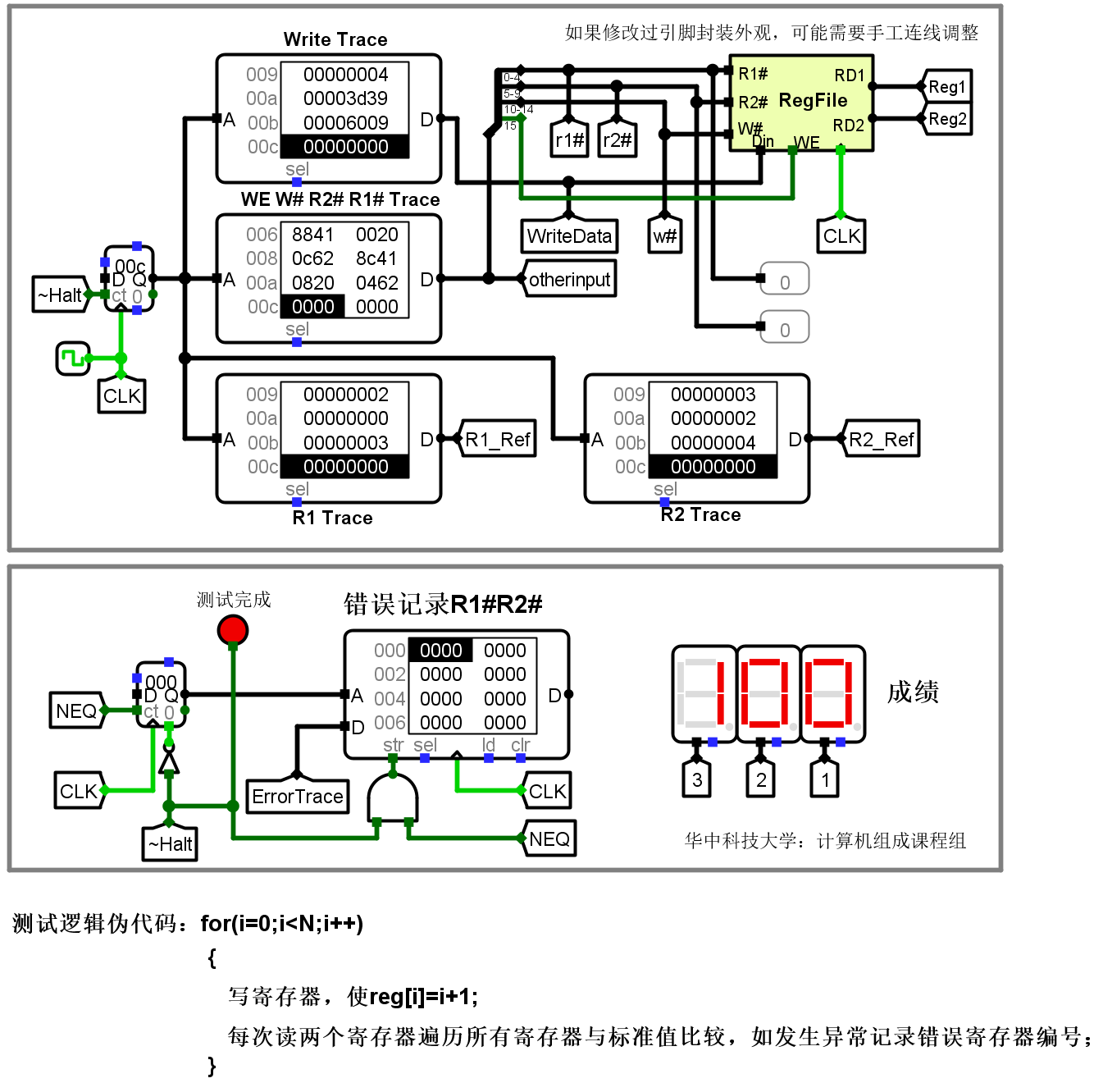

1. 实现MIPS寄存器文件设计

MIPS Regfile

MIPS Regfile测试结果为100分

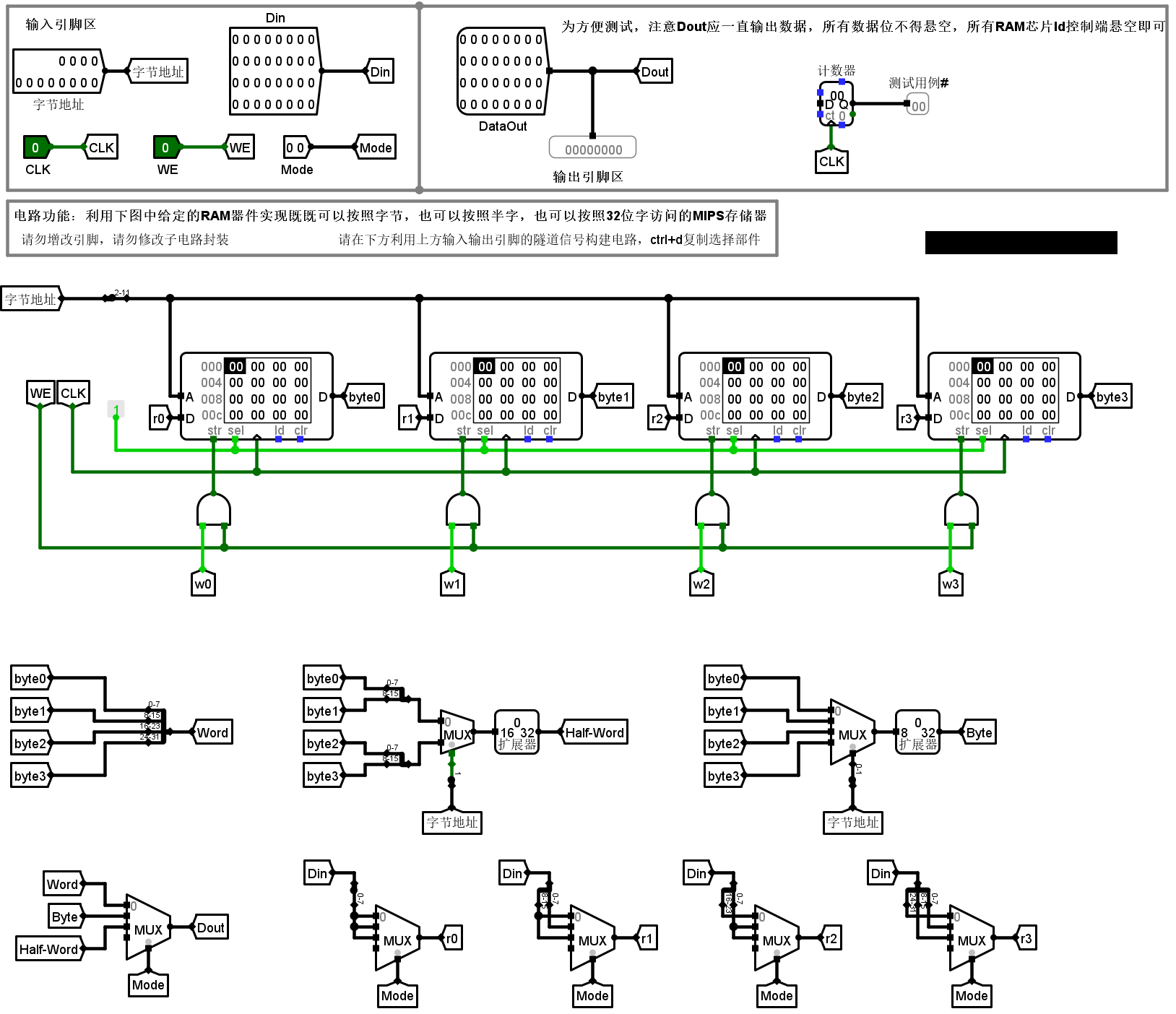

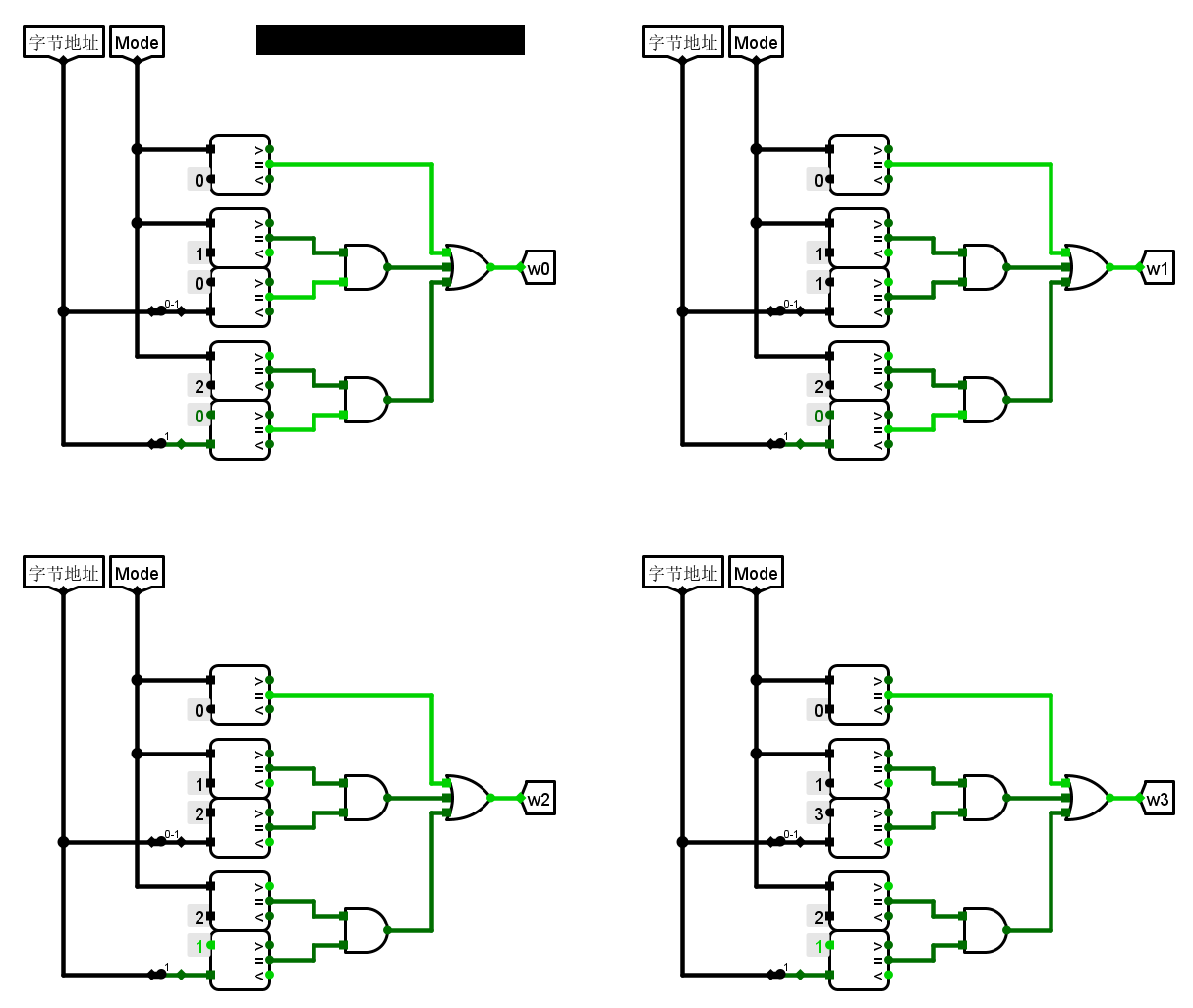

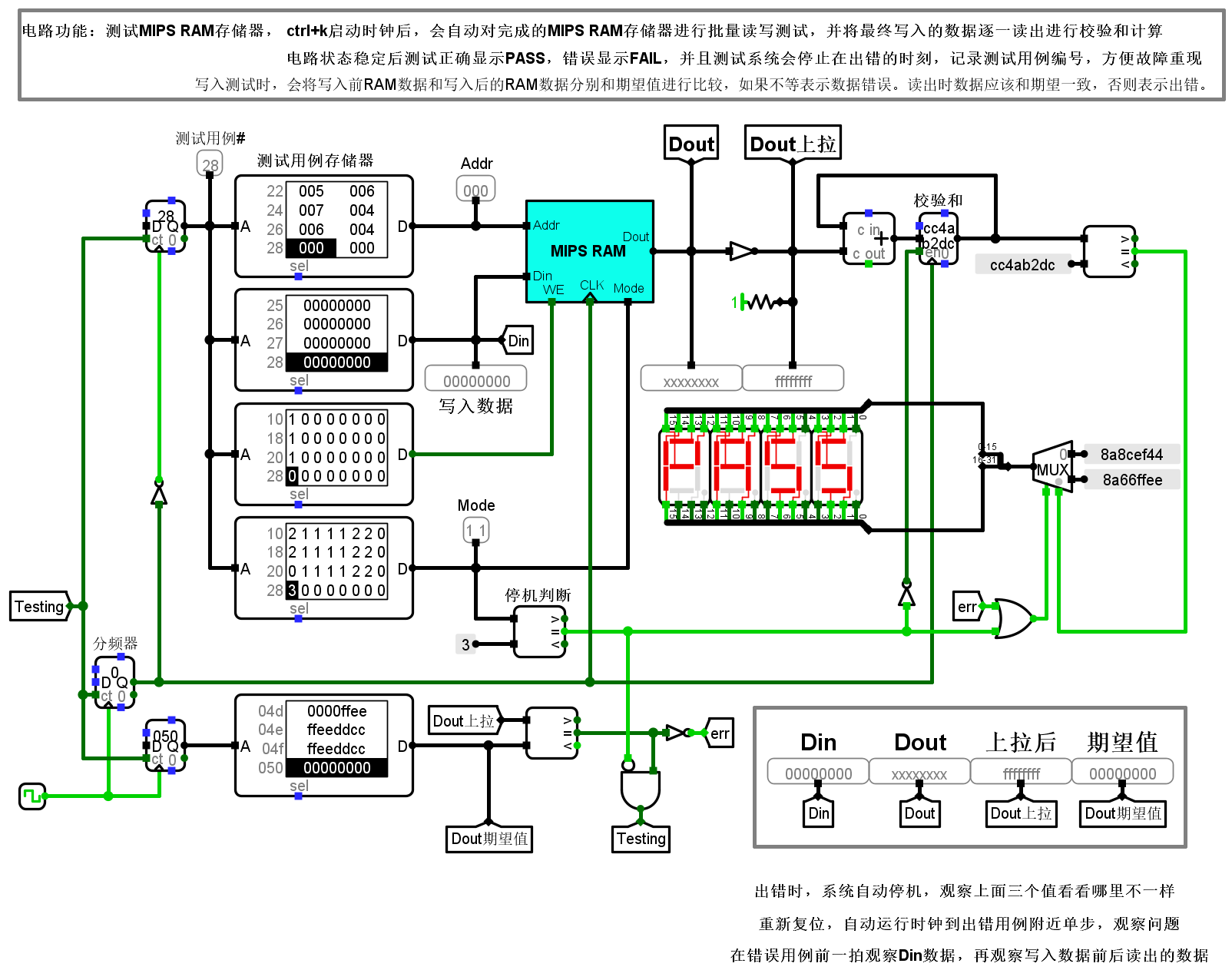

2. 实现MIPS RAM设计

MIPS RAM

MIPS RAM测试结果为PASS

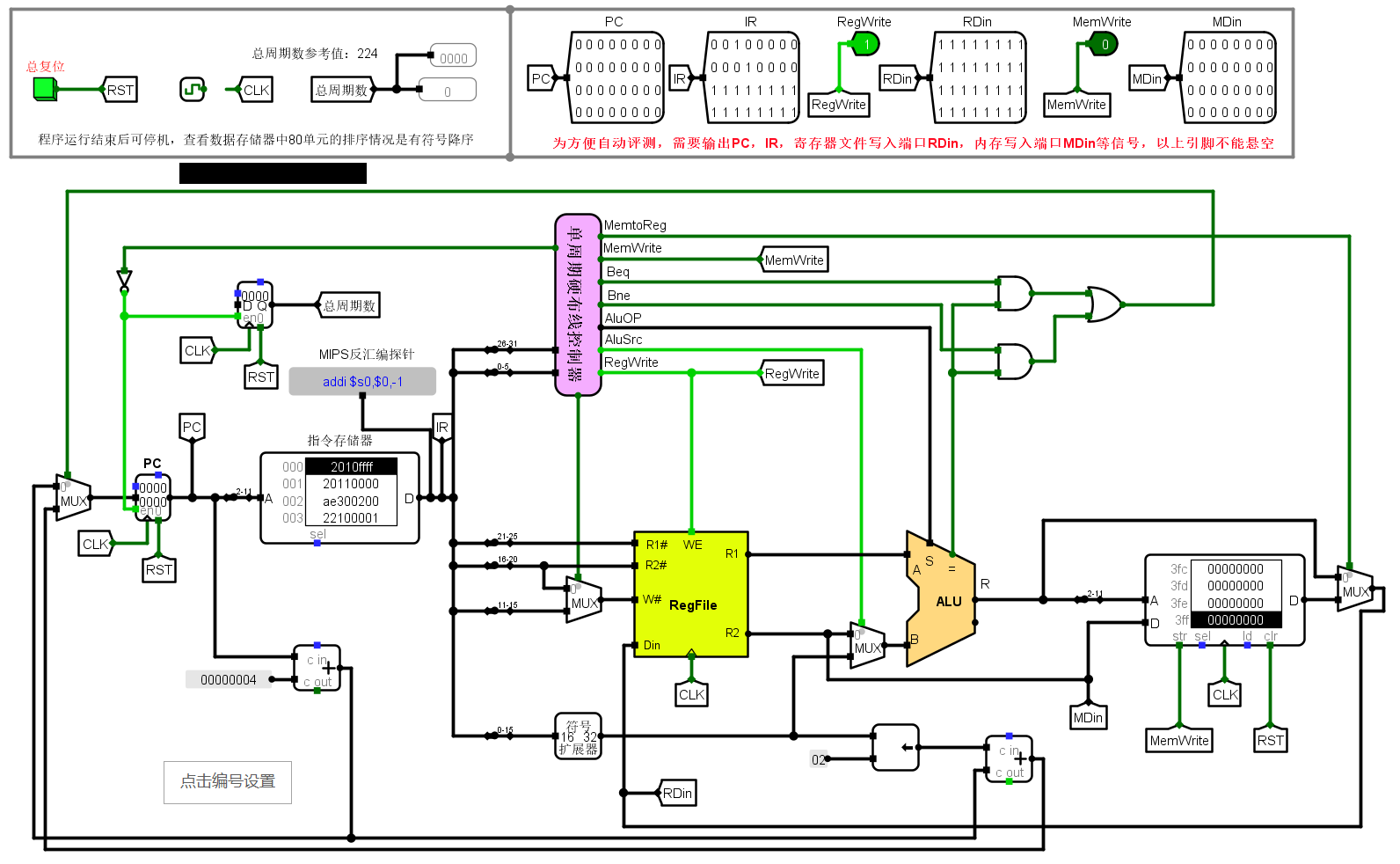

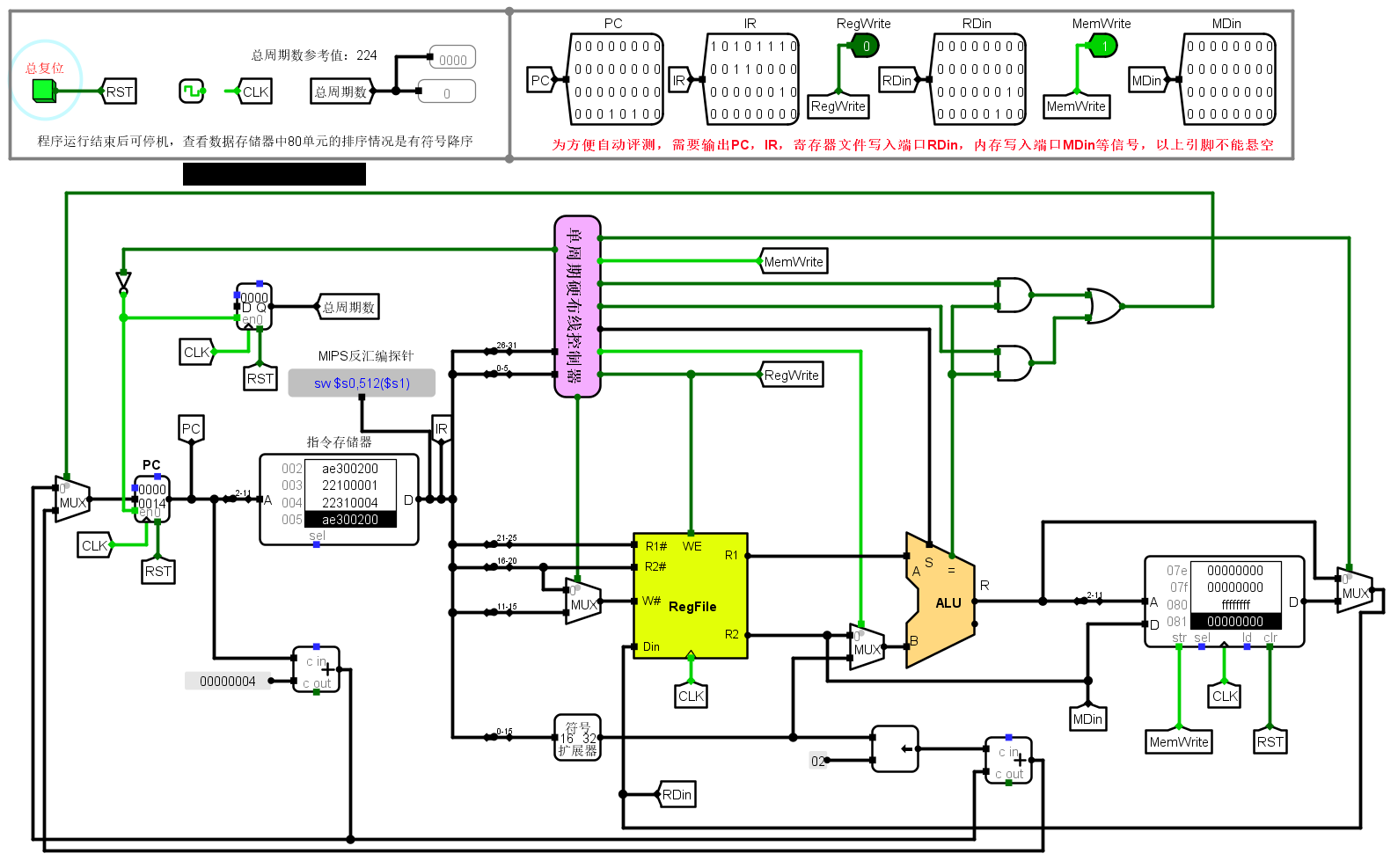

3. 绘制MIPS CPU数据通路

在MIPS单周期CPU子电路中,利用各个组件构建MIPS单周期CPU数据通路。

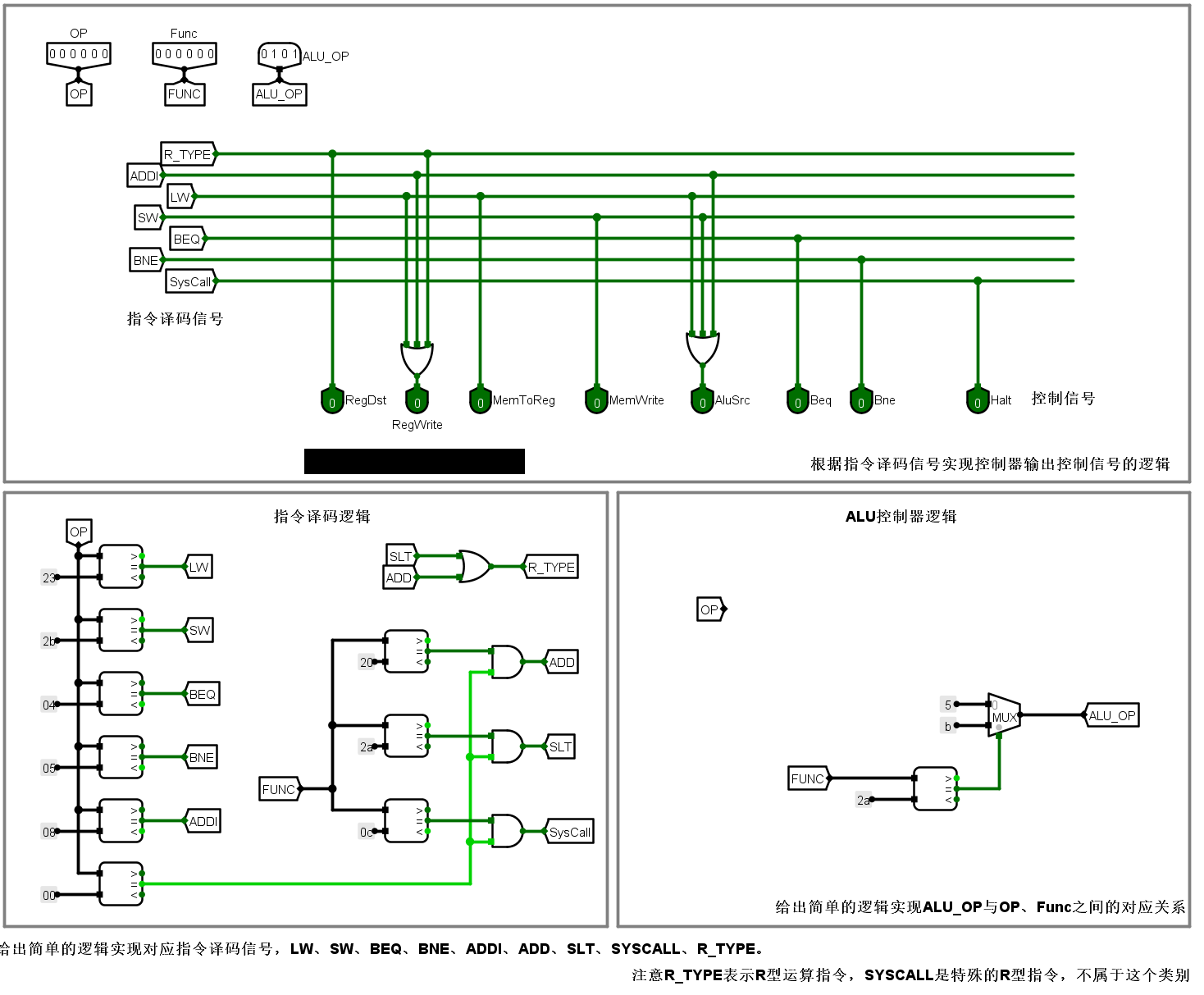

4. 实现单周期硬布线控制器

5. 测试CPU

在指令存储器中载入程序sort.hex,按下CTRL+K时钟自动仿真,程序停机后,查看数据存储器中排序情况。

测试结果:

五、遇到问题

在实验过程中,因为对CPU的组成缺乏一定的认识,导致不能正确设计实验电路。通过观看华中科技大学的计算机硬件系统设计公开慕课,解决了遇到的问题并成功完成单周期MIPS CPU设计。

六、实验心得

通过这次单周期MIPS CPU设计的实验,让我从理论到实践深入地学习了计算机体系结构和数字电路设计。这是对我能力的进一步锻炼,也是一种考验。从中获得的诸多收获,也是很可贵的,是十分有意义的。经过这次实验,我收获了很多,一方面学习到了许多以前没学过的知识与知识的应用,另一方面还提高了自我动手实验的本事,并且培养了我的独立思考的能力。在实验中我学到了许多新的知识,这是一个让我把书本上的理论知识运用于实践中的好机会,原先,学的时候感叹计算机组成的资料太难懂,此刻想来,有些其实并不难,关键在于理解。在这次实验的过程中,我也面临着许多困难,而我也在不断克服这些困难的过程中丰富了我的知识储备水平。真正的勇士敢于直面惨淡的人生,敢于正视淋漓的鲜血。人需要经历过困难,然后你才能慢慢学会成长,然后渐渐学会了如何去面对困难。正是因为这些困难,我深刻地体会到了计算机体系结构的实际应用和设计过程的复杂性。通过这个实验,我对计算机体系结构有了更深入的理解,对CPU的工作原理和指令执行过程有了更清晰的认识。总的来说,通过自己上手设计一个单周期MIPS CPU,我获得了宝贵的经验和技能,这对于我未来的学习和职业发展有着十分重大的作用。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?