中央处理器(CPU)=运算器+控制器

主机=中央处理器+主存储器

外部设备:除去主机以外的硬件装置(如输入设备、输出设备、辅助存储器等)

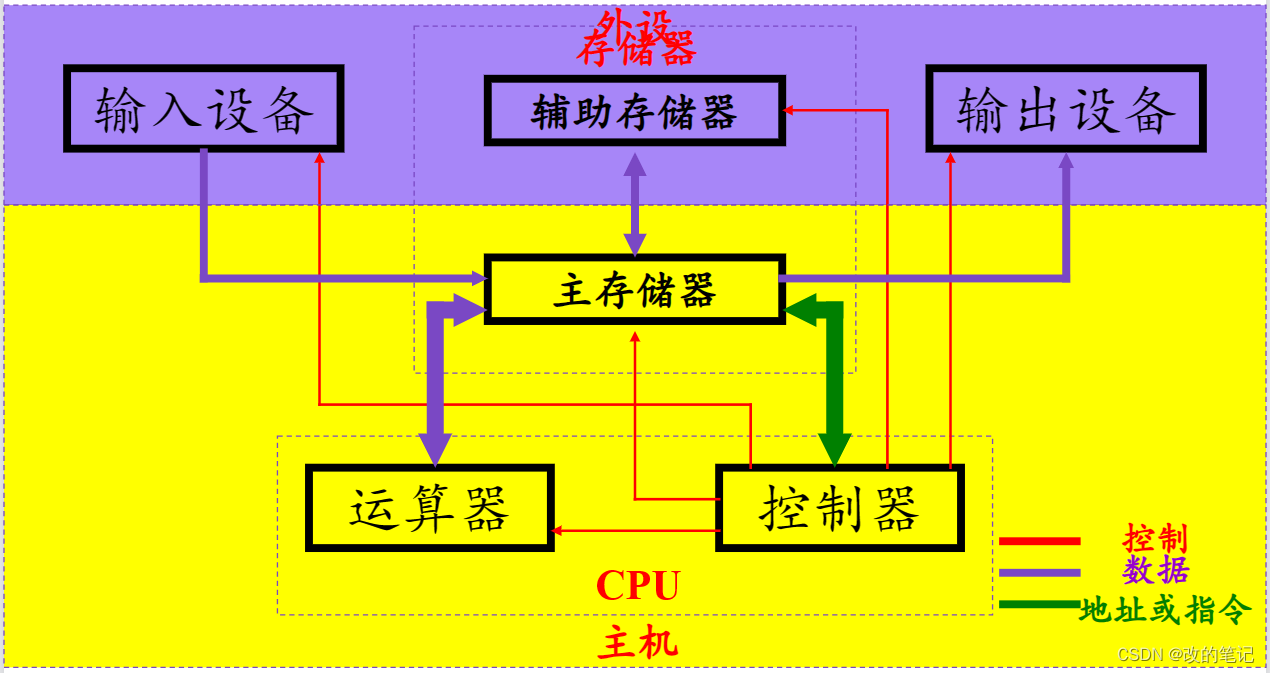

一、计算机的主要部件

计算机的组成框图

1、输入设备

输人设备的任务是把人们编好的程序和原始数据送到计算机中,并且将它们转换成计真机内部所能识别和接受的信息方式。

按输入信息的形态输入可分为字符(包括汉字)输入、图形输入、图像输入及语音输入等。

目前常见的输入设备有键盘、鼠标、扫描仪、摄像头、手写输入板等。辅助存储器(磁盘、磁带)也可视为输入设备。

2、输出设备

输出设备的任务是将计算机的处理结果以数字、字符(汉字)、图形、图像、声音等形式道收各那件的出计算机。

常用的输出设备有打印机、显示器、绘图仪等。辅助存储器也可以视为输出设备。

3、存储器

存储器是用来存放程序和数据的部件,它是一个记忆装置,是计算机能够实现“存储程序控制“的基础。

在计算机系统中,规模较大的存储器往往分成若干级,称为存储系统。

主存储器可由CPU直接访问,存取速度快,但容量较小,一般用来存放当前正在执行的程序和数据。辅助存储器设置在主机外部,它的存储容量大,价格较低,但存取速度较慢,一般用来存放暂时不参与运行的程序和数据。

CPU不可以直接访问辅存,辅存中的程序和数据在需要时才传送到主存,因此它是主存的补充和后援。

当CPU速度很高时,为了使访问存储器的速度能与CPU的速度相匹配,又在主存和CPU间增设了系统一级Cache(高速缓冲存储器)。

Cache 的存取速度比主存更快但容量更小用来存放当前最急需处理的程序和数据,以便快速地向CPU提供指令和数据。

4、运算器

运算器是对信息进行处理和运算的部件。经常进行的运算是算术运算和逻辑运等,所以运算器又称为算术逻辑运算部件(Arithmetic and Logical Unit,ALU)

运算器的核心是加法器。运算器中还有若千个通用寄存器或累加寄存器,用来暂存操作数并存放运算结果。寄存器的存取速度比存储器的存取速度快得多。

5、控制器

控制器是整个计算机的指挥中心,它的主要功能是按照人们预先确定的操作步骤,控制整个计算机的各部件有条不紊地自动工作。

控制器从主存中逐条地取出指令进行分析,根据指令的不同来安排操作顺序,向各部件发出相应的操作信号,控制它们执行指令所规定的任务。

控制器中包括一些专用的寄存器。

二、计算机各大部件之间连接

1、总线结构(小、微型机的典型结构)

总线(Bus)是一组能为多个部件服务的公共信息传送线路,它能分时地发送与接收各部件的信息。计算机中采用总线结构,可以天大减少信息传送线的数量,又可以提高计算机扩充主存及外部设备的灵活性。

最简单的总线结构是单总线结构。各大部件都连接在单一的-组总线上,故将这个单总线称为系统总线。

CPU与主存、CPU与外设之间可以直接进行信息交换,主存与外设、外设与外设之间也可以直接进行信息交换,而无须经过CPU的干预。

单总线结构提高了CPU的工作效率,而且外设连接灵话,易于扩充。

但由于所有部件都挂在同一组总线上,而总线又只能分时地工作,故同一时刻只允许一对设备(或部件)之间传送信息。

所谓单总线并不是指只有一根信号线(系统总线按传送信息的不同可以细分为地址总线、数据总线和控制总线)

地址总线(Address Bus)由单方向的多根信号线组成。用于CPU向主存、外设传输地址信息;

数据总线(Data Bus)由双方向的多根信号线组成。CPU可以沿这些线从主存或外设读入数据,也可以沿这些线向主存或外设送出数据:

控制总线(ControlBus)上传输的是控制信息,包括CPU送出的控制命令和主存(或外设)返回CPU的反馈信号。

总线结构是小、微型计算机的典型结构。这是因为小、微型计算机的设计目标是以较小的硬件代价组成具有较强功能的系统,而总线结构正好能满足这一要求。

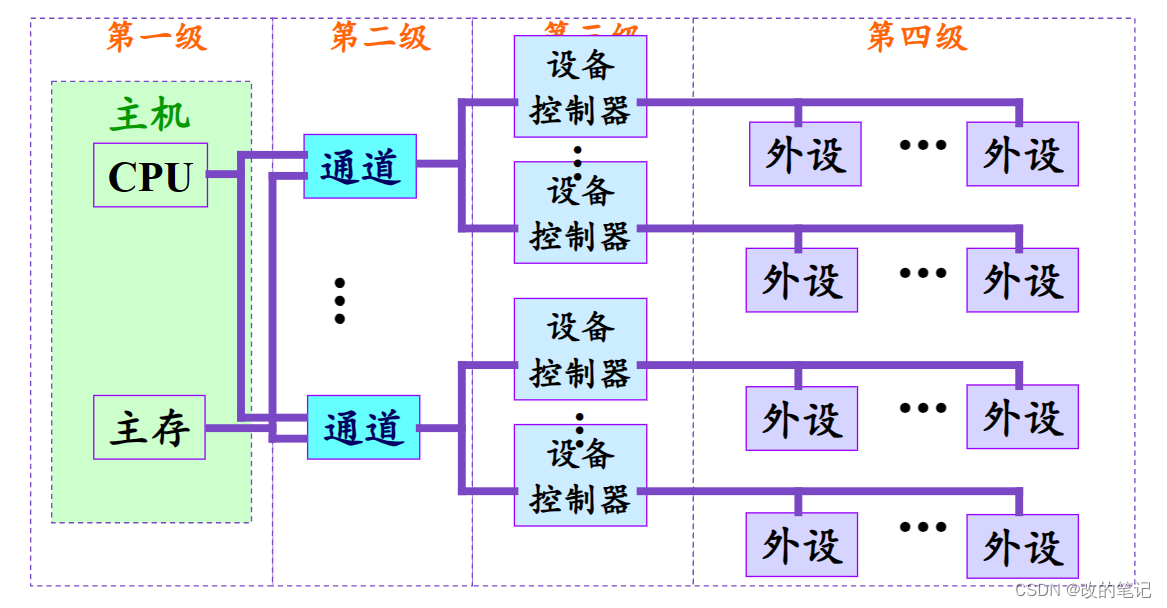

2.大、中型计算机的典型结构

大、中型计算机系统的设计目标更着正于系统功能的扩大与效率的提高。

在系统连接上分为四级:主机、通道、设备控制器和外部设备。

大、中型机系统的经典结构

通道是承担I/O操作管理的主要部件,每个通道可以接一台或几台设备控制器,每个设备控制器又可接一台或几台外部设备,这样整个系统就可以连接很多的外部设备。这种结构具有较大的扩充变化余地。

对较小的系统来说,可将设备控制器与外设合并在一起,将通道与CPU合并在一一起;对较大的系统,则单独设置通道部件;对更大的系统,通道可发展成为具有处理功能的外围处理机。

三、不同对象观察到的计算机硬件系统

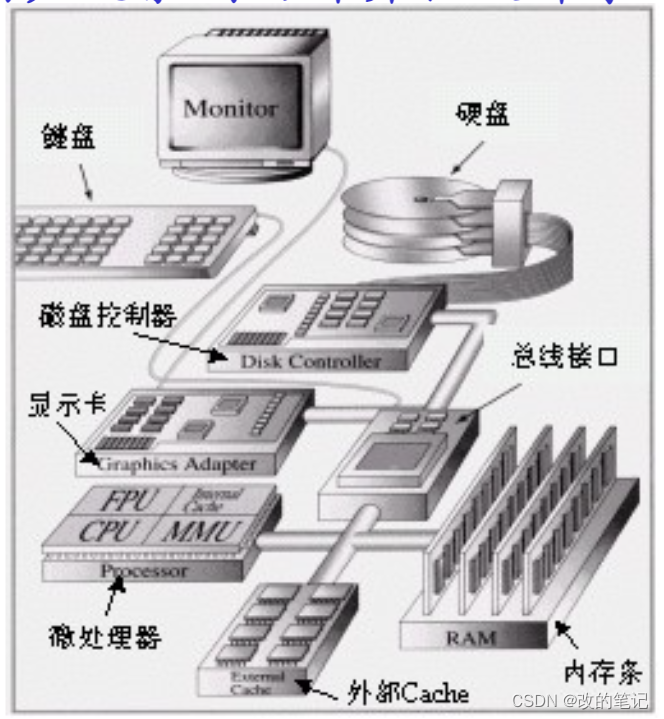

1、一般用户观察到的计算机硬件系统

一般用户观察到的计算机硬件系统

2、专业用户观察到的计算机硬件系统

专业用户观察到的计算机硬件系统

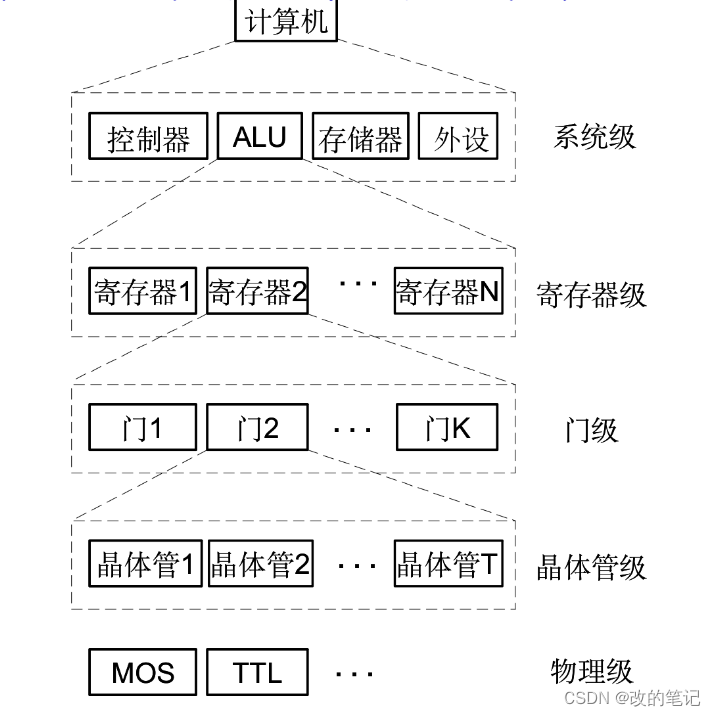

3、计算机设计者观察到的计算机硬件系统

计算机设计者观察到的计算机硬件系统

四、冯诺依曼结构和哈佛结构的存储设计思想

1.冯.诺依曼结构

冯.诺依曼结构也称普林斯顿结构,是一种传统的存储器设计思想。即指令和数据是不加区别地混合存储在同一个存储器中的,共享数据总线。

冯·诺依曼结构的存储器设计

指令地址和数据地址指向同一个存储器的不同物理位置,指令和数据的宽度相同。

指令和数据存放在同一存储器中,因此冯·诺依曼结构中不能同时取指令和取操作数。

存储器存取速度远远低于CPU运算速度,从而便计算礼运异速皮受到很入限的,CT心与共享存储器间的信息父快成了影响向违计等和系统性能的“瓶颈”。

使用冯●诺依曼结构的中央处理器是很多的。例如,Intel公司的80x86及其他中央处理器、ARM公司的ARM7和MIPS公司的MIPS等也都采用了冯·诺依曼结构。

2.哈佛结构

冯.诺依曼结构在面对高速实时处理时,不可避免会造成总线拥挤。为此哈佛大学提出了与冯.诺依曼结构完全不同的另种存储器设计思想,人们习惯称之为哈佛结构。

哈佛结构的指令和数据是完全分开的,存储器分为两部分,一个是程序存储器用来存放指令,另一个是数据存储器用来存放数据。

哈佛结构的存储器设计

哈佛结构至少有两组总线:

程序存储器(PM)的数据总线和地址总线

数据存储器(DM)的数据总线和地址总线

这种分离的程序总线和数据总线,可允许同时获取指令字(来自程序存储器)和操作数(来自数据存储器)而互不干扰。这意味着在一个机器周期内可以同时准备好指令和操作数,本条指令执行时可以预先读取下一条指令,所以哈佛结构的中央处理器通常具有较高的执行效率。

同时,由于指令和数据分开存放,可以使指令和数据有不同的数据宽度,如Microchip公司的PIC16芯片的指令宽度为14 位,而数据宽度为8位。使用哈佛结构的中央处理器有很多。例如,Motorola公司的MC68系列,Zilog公司的Z8系列,以及ARM公司的ARM9、ARM10和ARM11。大多数单片机和数字信号处理。

目前,许多现代微型计算机中的高速缓冲存储器(Cache)采用哈佛结构,将Cache分为指令Cache和数据Cache两个部分,而主存储器采用冯●诺依曼结构,只有一个,由指令和数据合用。如此将冯.诺依曼结构和哈佛结构结合起来,不仅可以提高主存储器的利用率,而且可以提高程序执行的效率,缩短指令执行的时钟周期。

2917

2917

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?