下列关于冯·诺依曼结构计算机基本思想的叙述中,错误的是

A.程序的功能都通过中央处理器执行指令实现 B.指令和数据都用二进制数表示,形式上无差别 C.指令按地址访问,数据都在指令中直接给出 D.程序执行前,指令和数据必须预先存放在存储器中

C

A程序的功能确实是通过中央处理器(CPU)执行指令来实现的。中央处理器是计算机系统的核心部件,负责解释和执行存储在内存中的指令序列。

中央处理器由运算器和控制器组成。控制器的主要功能是从主存中取出指令、分析指令(指令操作码译码)并产生有关的操作控制信号,从而执行指令。运算器则接收从控制器送来的命令,并对数据进行加工和处理

数据并不都是在指令中直接给出,指令中有时候给出的是数据的地址

计算机根据周期来区分指令和数据,因此数据是从存储器读出而非在指令中给出

2.考虑以下C语言代码:

unsigned short usi = 65535;

short si=usi;

执行上述程序段后,si的值是()

A.-1

B.-32767

C.-32768

D.-65535

A

gpt

在计算机系统中,有符号整数通常不使用原码表示,而是使用补码表示。补码表示有几个优点,使其成为计算机中广泛采用的标准。

原码表示

原码表示法(Sign-Magnitude)将符号和数值分开:

①最高位为符号位:0 表示正数,1 表示负数。

② 其余位表示数值的大小。例如,在 8 位系统中:

+5 的原码表示是 `0000 0101`。

-5 的原码表示是 `1000 0101`。缺点:

1. 有两个零:存在 `+0` 和 `-0` 两个不同的表示,处理起来复杂。

2. 运算复杂:加减法运算需要额外处理符号位和进位,增加了计算复杂度。补码表示

补码表示法(Two's Complement)通过对负数的数值部分取反后加 1 实现:

- 最高位为符号位:0 表示正数,1 表示负数。

- 其余位表示负数的补码形式。在 8 位系统中:

- +5 的补码表示是 `0000 0101`。

- -5 的补码表示是 `1111 1011`(取反 `0000 0101` 得 `1111 1010`,再加 1 得 `1111 1011`)。优点:

1. 唯一的零:只有一个零,即 `0000 0000`。

2. 加减法简单:加减法可以统一处理,不需要特殊处理符号位。

3. 溢出检测方便:通过符号位变化可以轻松检测到溢出。示例分析

对于一个 `unsigned short` 值 65535(在 16 位系统中):

`65535` 的二进制表示是 `1111 1111 1111 1111`。当把它赋值给一个 `short` 类型时,该二进制值被解释为补码形式的 `short`:

由于最高位为 1,它是一个负数。补码表示的负数,其值为 `-1`。

解释:

1. 对于补码 `1111 1111 1111 1111`:

取反得到 `0000 0000 0000 0000`。

加 1 得到 `0000 0000 0000 0001`,表示值 `1`。

因此,原补码值为 `-1`。```c

unsigned short usi = 65535; // usi = 65535 (binary: 1111 1111 1111 1111)

short si = usi; // si = -1 (binary: 1111 1111 1111 1111 in Two's Complement)

```总结

计算机中有符号整数使用补码表示,而不是原码表示(这里很重要)。这样处理更高效,也简化了加减法运算和溢出检测。因而,`unsigned short` 值 65535 被赋值给 `short` 时,结果是 -1。

一个数的补码(无论是负数还是正数)需要反转所有位,然后加1。👈

基础知识点走一波

原码(Sign-Magnitude Representation)

原码是一种直接表示带符号整数的方法。它使用一个二进制位来表示符号,其余位表示数值的大小。正数:符号位是0,其余位表示数值。

负数:符号位是1,其余位表示数值。例如,对于8位二进制数:

`+5` 的原码表示为:`00000101`

`-5` 的原码表示为:`10000101`反码(Ones' Complement Representation)

反码是一种表示负数的方式,负数的反码是将其对应正数的每一位取反。正数:与原码相同。

负数:正数各位取反(0变1,1变0)。例如,对于8位二进制数:

`+5` 的反码表示为:`00000101`

`-5` 的反码表示为:`11111010`补码(Two's Complement Representation)

补码是现代计算机中最常用的带符号整数表示方法。负数的补码是其反码加1。正数:与原码相同。

负数:正数的反码加1。例如,对于8位二进制数:

`+5` 的补码表示为:`00000101`

`-5` 的补码表示为:`11111011` (`11111010` + 1 = `11111011`)补码的优点

补码的使用有几个主要优点:

1. 唯一的零表示:补码表示中只有一个零,即`00000000`。反码和原码都有两个零,`00000000`(+0)和`11111111`(-0)。

2. 简化的加减运算:补码表示使得加法和减法运算可以统一处理,不需要区分正负数,简化了硬件设计。例子解释

计算`-5`的补码

1. 先求5的二进制表示:`00000101`

2. 求反码:`11111010`

3. 求补码:`11111010` + 1 = `11111011`验证`-5`的补码

通过补码验证可以看负数的表示是否正确:

1. `11111011` 直接解释为补码。

2. 求反码:`11111011` - 1 = `11111010`

3. 取反得到原码:`00000101`

4. 因为最高位是1,表示负数,实际值为-5。### 总结

原码:符号位表示正负,其余位表示数值。

反码:正数不变,负数按位取反。

补码:正数不变,负数反码加1。补码的使用简化了计算机的算术运算和硬件设计,使得处理带符号整数更加高效和一致。

3.假定计算机M1和M2具有相同的指令集体系结构ISA,主频分别为1.5GHz和1.2GHz。在M1和M2上运行某基准程序P,平均CPI分别为2和1,则程序P在M1和M2上运行时间的比值是()

A.0.4

B.0.625

C.1.6

D.2.5

C

CPI:执行一条指令所需的时钟周期数=总时钟周期数/IC

IC:总指令数

执行时间=(指令数*CPI)/时钟频率

因为具有相同的指令集,所以就约掉了😝

(2/1.5)/(1/2)=1.6

4.float 型数据通常用 IEEE754 单精度浮点数格式表示。若编译器将 float 型变量 x 分配在一个 32 位浮点寄存器 FR1 中,且 x=-23.125,则 FR1 的内容是( )。

A. C104 0000H

B. C142 0000H

C. C1B9 0000H

D. C1C9 0000H

C

以下是个人见解😊:

IEE754标准下单精度在内存中的中的存储方式

| 符号位 | 指数位(偏移后) | 尾数位 |

| 1bit | 8bits | 23bits |

十进制-23.125用二进制表示为

10111.001

1.先确认符号位:1

| 符号位 | 指数位(偏移后) | 尾数位 |

| 1 | 8bits | 23bits |

2.再来确认指数位:

把二进制转换为以2为底的指数形式,要求小数点前的数字非0(那就是只能是1.的形式?不知道我理解对没有🤨)

那就是1.0111001

橙色的数字是偏移后的位数

1.0111001*2^4

4+127=131

然后131的二进制为1000 0011(当当🤠指数位有了)

指数+偏移量=一个非负整数

其中1.0111001是尾数, 而4就是偏移前的指数(unbiased exponent),32位单精度浮点数的偏移量(bias)为127, 所以这里加上偏移量之后, 得到的偏移后指数(biased exponent)就是 4 + 127 = 131, 131转换为二进制就是1000 0011

| 符号位 | 指数位(偏移后) | 尾数位 |

| 1 | 1000 0011 | 23bits |

3.再对尾数进行处理

因为尾数的最高位始终为1,所以在存储尾数时,省略前面的1和小数点,只记录尾数中小数点之后的部分,也节约了一位内存👾

现在的二进制数为0111001总共7位,但是尾数位可是23位,怎么办😱

补零😜

| 符号位 | 指数位(偏移后) | 尾数位 |

| 1 | 1000 0011 | 11000001101110010000000000000000 |

验证浮点数内存网站

但是题目不要这一长串的二进制,它要16进制的数

B:11000001101110010000000000000000

H:用8421码求,超快😎

| 8+4 | 1 | 8+2+1 | 8+1 |

| 1100 | 0001 | 1011 | 1001 |

| C | 1 | B | 9 |

所以可得C1B90000(H)

5.某计算机采用大端方式,按字节编址。某指令中操作数的机器数为1234FF00H,该操作数采用基址寻址方式,形式地址(用补码表示)为FF12H,基址寄存器内容为F000 0000H,则该操作数的LSB(最低有效字节)所在的地址是()

A.F000 FF12H

B.F000 FF15H

C.EFFF FF12H

D.EFFF FF15H

D

王道:

注意:内存地址是无符号数

操作数采用基址寻址方式,EA=(BR)+A

基址寄存器BR的内容为F000 0000H,

形式地址用补码表示为FF12H即1111 1111 0001 0010B

因此有效地址为F000 0000H+(-00EEH)=EFFF FF12H

计算机采用大端方式编址,所以低位字节存放在字的高效地址,机器数一共4字节,该操作数的LSB所在的地址是EFFF FF12H+3=EFFF FF15H

讲解来自

按字节编址,采用大端方式,低位的数据存储在高地址位、高位的数据存储在低地址位,采用相对寻址模式,PC+A得到地址,于是F000 0000 +FF12得到EFFF FF12,这是高位地址,于是最低有效地址是EFFF FF12+3得到EFFF FF15H。

- 找出操作数的机器数:1234 FF00H

- 确定该操作数采用基址寻址方式,形式地址为FF12H,即相对于基址寄存器的偏移量为FF12H。

- 基址寄存器的内容为F000 0000H,将此与偏移量相加得到有效地址: F000 0000H + FF12H = F000 FF12H

- 按照大端字节序,LSB(最低有效字节)的地址应为 F000 FF15H,因为在大端字节序中,一个字(word)的最低有效字节的地址比字的首地址高3个字节。

补充:在大端字节序中,高位字节存放在低地址处,因此一个字的最低有效字节的地址比字的首地址高3个字节。例如,在一个以大端字节序存储的32位字中,第一个字节包含了该字的最高有效字节,而第四个字节则包含了该字的最低有效字节。因此,如果要访问一个字的最低有效字节,在大端字节序中需要先跳过前三个字节,才能到达最低有效字节所在的位置。

个人理解:

书P314

基址寻址需设有基址寄存器BR,其操作数的有效地址EA等于指令字中的形式地址与基址寄存器中的内容(称为基地址)相加,即

EA=A+(BR)

形式地址有了:FF12H

基址寄存器内容为F000 0000H

FF12H+F000 0000H=F000 FF12H

然后F000 FF12H+3

6.按字节编址的计算机中,某double型数组A的首地址为2000H,使用变址寻址和循环结构访问数组A,保存数组下标的变址寄存器初值为0,每次循环取一个数组元素,其偏移地址为变址值乘以sizeof(double),取完后变址寄存器内容自动加一。某次循环所取元素的地址为2100H,则进入该次循环时变址寄存器的内容是()

A.25

B.32

C.64

D.100

B

2000H+8*x=2100H

x=32

7.假定DRAM芯片中存储阵列的行数为r,列数为c,对于一个2K*1位的DRAM芯片,为保证其地址引脚数最少,并尽量减小刷新开销,则r,c的取值分别是()

A.2048,1

B.64,32

C.32,64

D.1,2048

C

2K*1位意味着有2K个存储位置

一个DRAM的存储阵列是一个二维结构,由行和列组成,行数*列数=总的存储位置

地址引脚的数量取决于r和c

刷新开销与行数有关

因为DRAM需要周期性地刷新每一行以保持数据,行数越少,刷新频率越低

书P86刷新的过程实质上是先将原存信息读出,再由刷新放大器形成原信息并重新写入的再生过程。

2K = 2048

A2048*1=2048,但是有2048行,会增加刷新的开销

B和C之间抉择🤠

因为64=2^6

32=2^5

5<6

8.设机器字长为32位,一个容量为32MB的存储器,CPU按字寻址,其可寻址的单元数为()

A.1M

B.4M

C.8M

D.32M

C

我根据我之前的文章做题思路算的

32/8=4

32MB=2^25

2^25/2^2=2^23

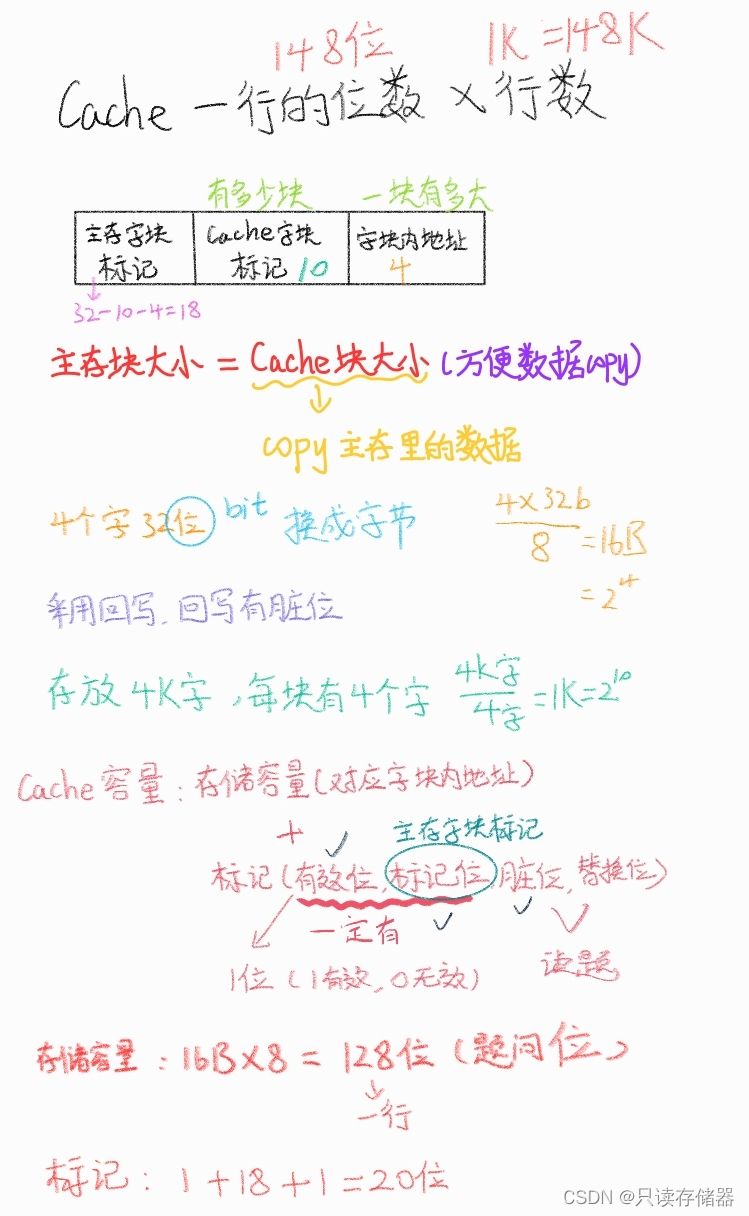

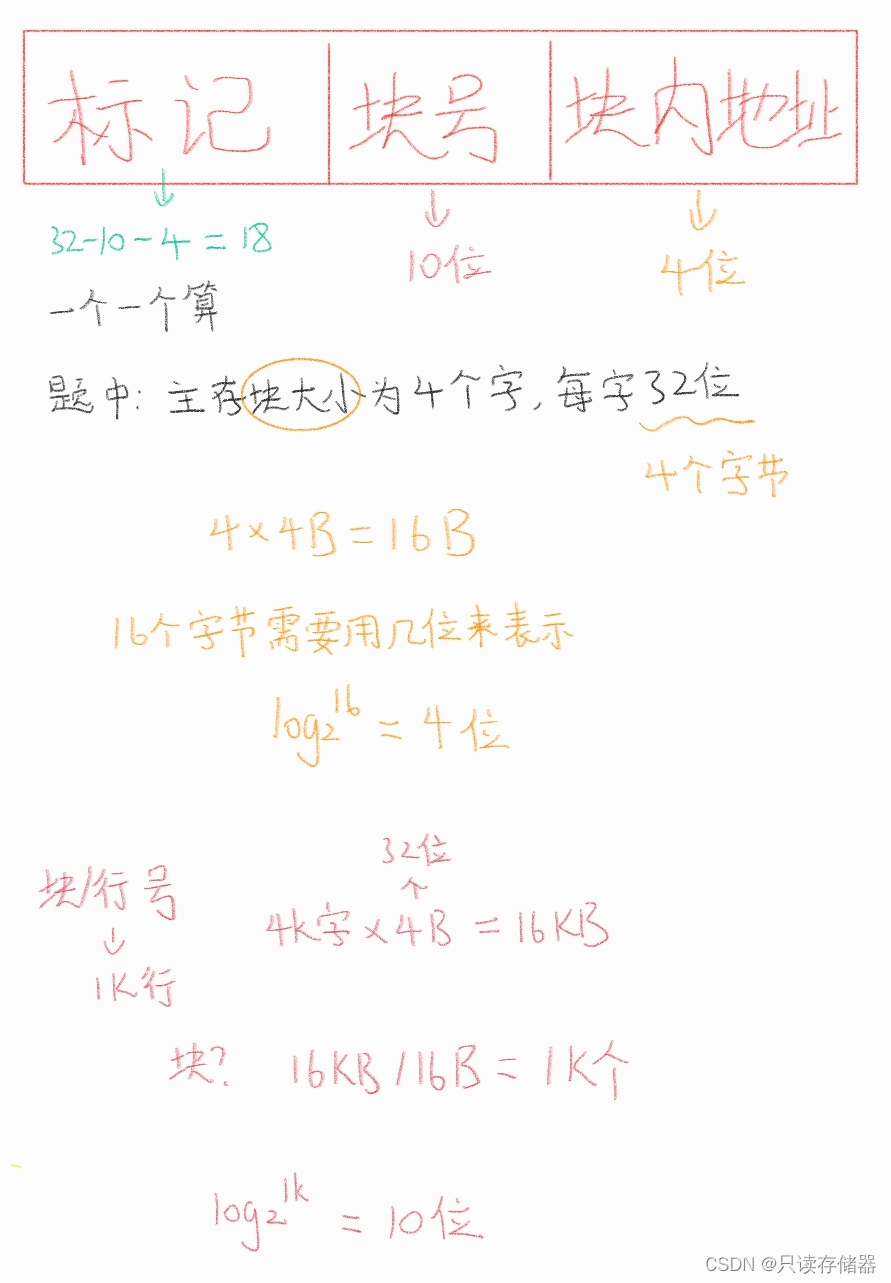

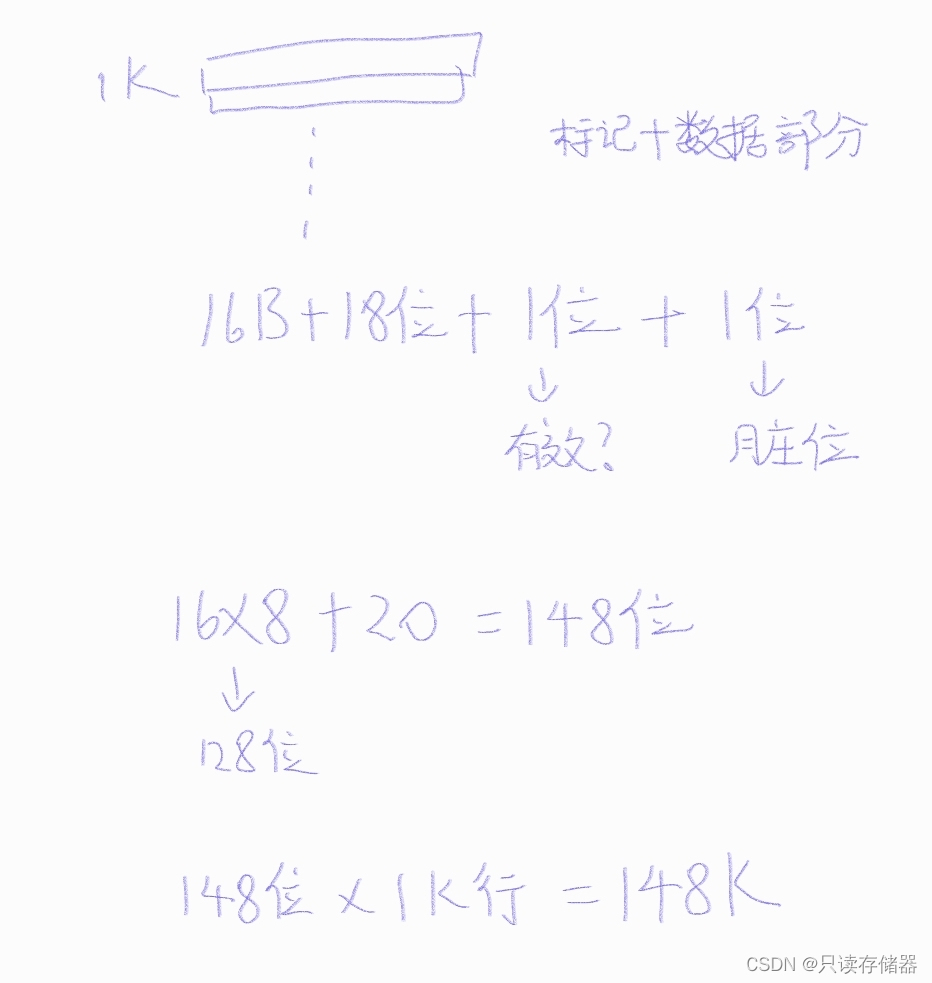

9.假定主存地址为32位,按字节编址,主存和Cache之间采用直接映射方式,主存块大小为4个字,每字32位,采用回写(Write Back)方式,则能存放4K字数据的Cache的总容量的位数至少是()

A.146K

B.147K

C.148K

D.158K

C

10.下列关于多总线结构的叙述中,错误的是()

A.靠近CPU的总线速度较快

B.存储器总线可支持突发传送方式

C.总线之间须通过桥接器相连

D.PCI-Express*16采用并行传输方式

D

桥接器用于连接不同的总线,具有数据缓冲,转换和控制功能

D是串行

突发传输:在地址总线上进行一次地址传输后,进行多次数据传输

突发是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输的周期数就是突发长度

突发传送——支持成块连续数据的传送,只需给出数据块的首地址,后续数据地址自动生成。

在一个总线周期内传输存储地址连续的多个数据字,也就是说一次传输一个地址和一批地址连续的数据

突发

11.某计算机使用4体交叉编址存储器,假定在存储器总线上出现的主存地址(十进制)序列为8005,8006,8007,8008,8001,8002,8003,8004,8000,则可能发生访存冲突的地址是对是()

A.8004和8008

B.8002和8007

C.8001和8008

D.8000和8004

D

之前文章写过

8005%4=2001...1

模块序号=访存地址%存储器交叉模块数

12.某计算机的Cache共有16块,采用4路组相联映射方式(即每组4块)。每个主存块大小为32字节,按字节编址。主存500号单元(所有序号都从0开始)所在主存块应装入到的Cache组号是()

A.1

B.2

C.3

D.4

?

147

147

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?