目录

一、指令周期的概念

计算机取出并执行完一条指令所需的全部时间,就叫做 指令周期。

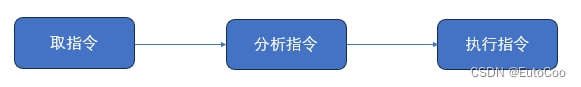

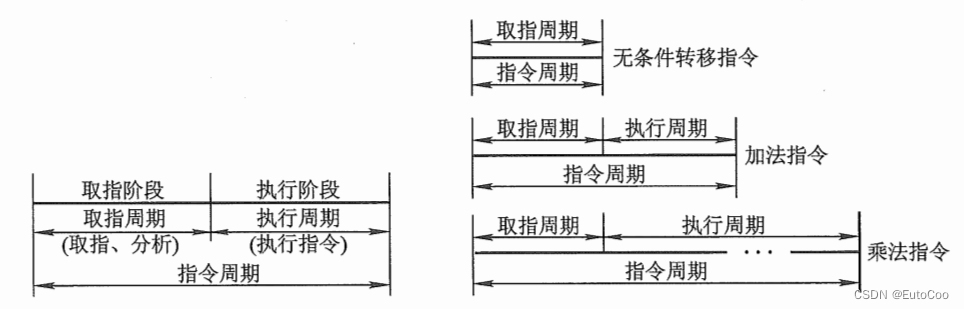

我们已经知道,一条指令的执行过程可以分为 取指令、分析指令 和 执行指令 三个步骤,因此一个指令周期也应该包含这三部操作需要的时间。由于分析指令时可以用硬件实现操作码的译码,因此这步操作用时很短,一般可以将取指令和分析指令合并为一个阶段,对应的时间称为 取指周期;而执行指令阶段所需的时间就称为 执行周期。

很明显,各种指令的取指周期是一样的,但由于具体的执行操作不同,执行周期各不相同;因此指令周期是可以不同的。

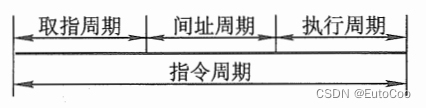

前面我们将 ”分析指令“ 这一步合并入了取指周期,是因为操作码的译码非常简单;但分析指令不仅仅要对操作码进行译码,还需要根据形式地址得到有效地址。在间接寻址的方式下,指令字中给出的是 ”地址的地址“,所以需要先访问主存一次、取出有效地址,然后再次访问主存取出操作数。这个阶段称为 间址周期。

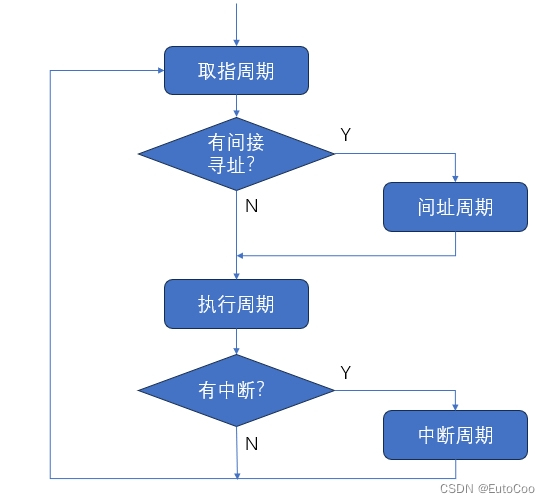

此外,计算机在执行过程中,可能会出现异常情况或者特殊请求,这时需要进行中断处理。所以 CPU 会在每条指令执行阶段结束前,发出 ”中断查询信号“,检测是否有某个 I/O 设备提出了中断请求;如果有,则 CPU 进入中断响应阶段,称为 中断周期。中断周期中 CPU 需要将程序断点保存到存储器中。

所以,一个完整的指令周期应该包括 取指、间址、执行 和 中断 4 个部分。间址和中断周期不一定会包含在指令周期中。这 4 个周期内都会有访存操作,又可称为 CPU 的 ”工作周期“。

-

取指:访问主存取出指令

-

间址:访问主存获取有效地址

-

执行:从主存中取操作数,或将结果写入主存

-

中断:将程序断点保存到主存

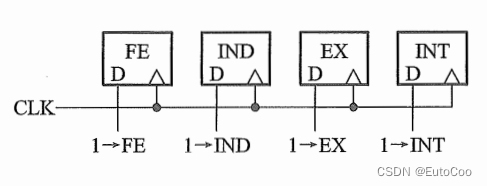

在 CPU 的硬件底层,为了区分不同的工作周期、更方便地设计控制单元 CU,往往会设置一组 CPU 工作周期的 ”标志触发器“。

上面的 4 个 D 触发器 FE、IND、EX 和 INT 就对应了指令周期的取指(fetch)、间址(indirect addressing)、执行(execute)、中断(interrupt) 4 个阶段,以 ”1“ 状态来表示有效。在取指阶段,只要设置 FE 为 1,就可以由它控制取指阶段的各步操作;当取指结束、进入间址周期时,只要将 FE 置 0、IND 置 1 就可以了。

二、时钟周期和机器周期

1.时钟周期

计算机是由 时钟信号 来控制时间顺序的。

时钟信号是由机器中的主振电路(比如晶体振荡器)发出脉冲信号后,经整型或分频后产生。时钟信号的宽度称为 时钟周期,时钟信号的频率就是 CPU 的 主频,时钟周期和机器主频互为倒数。时钟周期是 CPU 工作的最小时间单位。

用时钟信号控制节拍发生器,可以产生 节拍;每个节拍的宽度就对应着一个时钟周期。在一个节拍内,机器可以完成一个最小的操作(微操作),或者是几个需要同时执行的操作。

2.机器周期

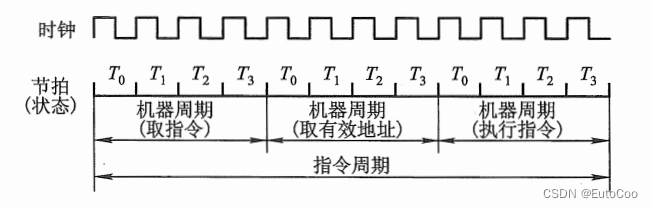

每条指令都可以包含四个不同的阶段,每个阶段都至少会访问一次主存。

由于访问主存占据了大部分时间,需要一次访存的操作耗时都差不多,因此我们可以设置一个统一的 ”基准时间“,在这个基准时间内,所有阶段的操作都可以完成;这个基准时间就被称为 机器周期。

可以看到,一个指令周期包含了若干个机器周期,而一个机器周期又包含若干时钟周期。

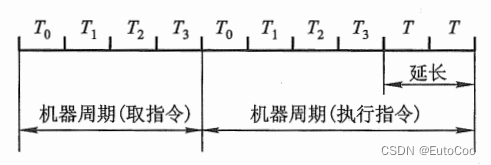

上面的例子中,每个机器周期都是相等的,包含 4 个节拍(时钟周期),这是定长的机器周期;如果每个机器周期中包含的节拍数不等,就是不定长的机器周期:

不定长的机器周期更适合比较简单的指令,它可以跳过一些不需要的时钟周期,从而让整个指令周期变短。我们可以默认给一个较短的机器周期,对于比较复杂的操作,则通过增加节拍、通过延长机器周期来解决。

三、处理器的设计方式

针对指令周期采用不同的方式,可以设计出不同类型的 CPU。

1.单周期处理器

单周期处理器中,指令周期固定为 一个时钟周期。

在这种方式下,所有的指令都在相同的时间内执行完成,把这个时间就设置为时钟周期,因此 CPI 为 1。因为指令是串行执行的,这样,时钟周期就会以最慢的指令的执行时间为准,从而导致 CPU 主频较低、运行速度较慢。

单周期处理器实现比较简单,但性能较差,不能充分利用硬件资源。

2.多周期处理器

多周期处理器,则是指每条指令需要若干个时钟周期来完成。

一般来说,多周期处理器会将整个 CPU 的指令执行过程分成几个阶段,每个阶段又用若干个时钟周期去完成,然后开始下一条指令的执行。这样,各种指令执行需要的时钟周期数就可能不同。

多周期 CPU 可以更加充分地利用硬件资源,提升执行效率。不过由于每种指令的执行时间不同,需要对指令进行分类,实现起来较为复杂。

3.流水线处理器

流水线处理器同样会将 CPU 执行指令的过程分为几个阶段,而每个阶段都占用相同的时间(机器周期);在同一时间,在计算机的各个部件上可以依次执行每条指令的不同阶段,就像在流水作业线上处理指令一样。

这样的方式使得指令可以并行执行,大大提升了系统运行效率。每个机器周期,CPU 都会取出一条新的指令;如果以机器周期作为时钟周期,那么理想情况下,流水线的执行效率可以做到接近于每个时钟周期处理 1 条指令,即 CPI 为 1。

2249

2249

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?