本文为个人准备集创赛-曾益慧创杯所作学习笔记

Cadence是一家公司(软件供应商),其软件主要有PCB设计工具allegro和芯片版图设计virtuoso[vɜːrtʃuˈoʊsoʊ]

大部分EDA工具使用Linux平台而不是Windows?因为多数工程软件原先都是在UNIX平台上开发和使用的。这些工具出现的时候还没有微软的Windows呢。

virtuoso

Linux内软件使用

-

双击打开文件夹观感不大好,右击Browse Folder更符合Windows习惯(IC618没有?)

-

在terminal中,可以使用which指令

查找对应的文件路径, eg:which virtuoso -

ctrl+L在文件目录中开启

搜索(进入路径) -

terminal中输入"空格&"可以保持terminal窗口继续运行(否则只能执行一次,关掉才能干其他的)

软件介绍

Tools菜单

-

Library Manager: 是设计过程中频繁使用的库管理界面,可以在界面方遍地看到库名称,操作库内容。

-

Library Path Editor: 这个实际就是cds.lib文件的内容,有的用户不习惯操作文件,可以直接在这个界面内设置库的路径。

-

Technology File Manager: 上一节跟大家提到过不同设计可能采用不同的工艺设计库,这个工具可以用来实现把用户的不同设计对应到不同工艺库。

快捷键

有大小写区分

i:放置器件

g:查看报错详情。如果原理图中有遗漏的地方软件会报错或者警告

确认原理图没有出错,可以在电路旁边加上适当的注释,在原理图输入界面的菜单栏,选择:Create->Note, 可以选择添加文本注释或者注释框,写上原理图功能、状态,如果完成仿真之后还可以添加电路的工作条件、性能等信息,以供日后方便阅读。

F:(fit)适当缩放

-

移动命令:M(move), 按下快捷键之后,鼠标左键单击器件,实现对象移动;m(stretch), 按下快捷键之后,鼠标左键单击器件,实现对象拖拽(移动的时候保持连线关系不变)。

-

文件命令:S(save), 按下快捷键保存原理图设计;x(check), 按下快捷键检查输入的原理图是否存在错误;X(check & save), 按下快捷键检查输入的原理图是否存在错误并保存设计。

-

其他命令:c(copy), 按下快捷键之后,鼠标左键单击器件,实现复制功能;r(rotate), 按下快捷键之后,鼠标左键单击器件,实现对象旋转;u(undo), 按下快捷键撤销上一个操作;U(redo), 按下快捷键撤销上一个撤销操作。

工程创建

-

在home内建立自己的工程文件夹

-

在里面放入cds.lib;cdsinit;.cdsenv三个文件

-

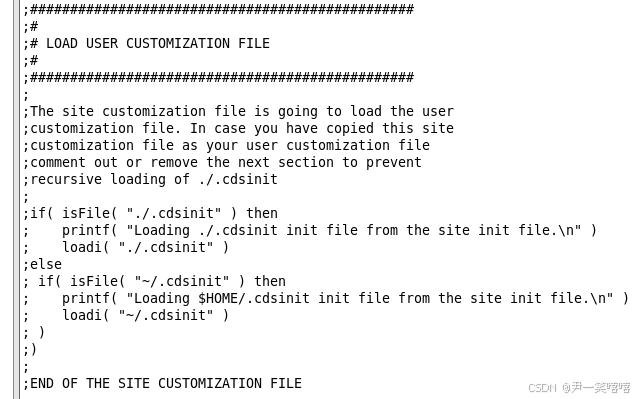

将cdsinit文件内最后那段ifelse语句注释掉(在行首加;)(防止递归调用导致死机,暂时用不到) (注意只注释掉load user customizattion file)

-

在terminal中输入"virtuoso"打开软件

-

在弹出的窗口里左上角的tools选项中单击第一个"library manager"可以管理库

-

file->new->library->取名&选择工艺库 -

file->newcellview->取名->放器件(i)->连线(w)->给线命名(l)(lable)加引脚(p)->check&save -

调参数:点击元件按q

-

这时就可以进行仿真了

Launch->ADEL,当然也可以"封装"完之后再仿真 -

creat->cellview->from cellview->OK->规定pin脚的位置(一般把gnd放下边,需要修改)->OK -

"画symbol":先把里边那个方框删掉->再使用上方的工具作画(可以先在空白处画好再移过去,眼睛不花)->保证所有的东西都在外框内->

check&save -

Testbench验证:

Library Manager->file->cellview->命名(一般为sim_xx或xx_tb)->ok->放置刚才的电路->从analoglib调用电压源(vdc)、地(gnd)、方波信号(vpulse)用作激励源,在输出端接一个电容(cap)引到Gnd;修改激励源的参数(电压)(3V直接输3即可,3μV输3u);->左上角的launch->ADEL->右击Analyses框下空白处->edit->tran(时序仿真)->stop time(一般五倍于观测周期),仿真精度一般选第二个moderate(第一个最准),Sweep Variable(扫描变量)可以选择想要观察的自变量如BJT的Vds,下方是Range -

setup->modellibraries中需要添加所需要的"仿真库",并且选择库里面用了哪些section -

三个框左侧那个

Design Variables中可以编辑变量(Vcc,gnd),Copy From Cellview可以从原理图中选择.在outputs->To be plotted->Select on design,点击想看点位就是了,不易看多个点位的波形可以点花花绿绿的图标的第一个(family右侧第一个)(波形上方的滑轨或右键一划拉可以缩放)(第一个是分割第二个是合并) -

保存仿真波形在adel窗口内点击

session->save state->cellview

补充与解释

步骤2

文件名称的解释

-

cds.lib文件:该文件是设计库管理文件,包含一些基础设计库定义和用户自定义工程库。

-

cdsinit文件:包含Cadence的一些初始化设置信息,以及软件的快捷键设置,部分功能和.cdsenv文件重叠

-

cdsenv文件:是Cadence环境的软件变量包含Cadence各种工具的初始化设置信息

文件的原始路径

cds.lib的路径:/opt/eda/cadence/IC618/share/cdssetup/cds.lib(文件内出现softinclude 后无论是一行还是四行性质都是一样的) 这里也有/opt/eda/cadence/IC618/tools/dfII/samples

cdsinit的路径:/opt/eda/cadence/IC618/tools/dfII/samples/local/cdsinit

cdsenv的路径:/opt/eda/cadence/IC618/tools/dfII/samples

步骤3

光标是实心的不能输入注释怎么办呢?可以按键盘上的ins键(insert)切换输入与覆盖模式,在home左边,也可以选一个不重要的字符,随便敲一个字符就变成输入模式了

步骤5

-

Virtuoso 的

工艺库分为两种,CDS(Cell Database Standard)(老版)和OA(OpenAccess)(新版)。-

CDS主要是51版本(老版)使用,比如IC5141。OA主要是61版本使用,比如IC617 和IC618 。

-

-

导入库:

Tools->Library Path Editor->Edit->Add Library->选好右边library栏的库->OK->file->save(如果无法保存,去Edit->Exclusive lock取消勾选即可,这样读写cds.lib保护锁就会打开) -

library manager中没有标准库???解决方法是将工程目录cds.lib文件内的SOFTINCLUDE改成如下四行

-

SOFTINCLUDE /opt/eda/cadence/IC618/share/cdssetup/dfII/cds.lib SOFTINCLUDE /opt/eda/cadence/IC618/share/cdssetup/hdl/cds.lib SOFTINCLUDE /opt/eda/cadence/IC618/share/cdssetup/pic/cds.lib SOFTINCLUDE /opt/eda/cadence/IC618/share/cdssetup/sg/cds.lib

-

库分类

-

基准库: sample存储普通符号;

US_8ths存储各种尺寸和模版;basic库则包含特殊管脚信息;Analog基本模拟器件单元库。 -

设计库:用户根据使用需要自行创建。

-

-

库结构

-

库(library)

-

单元(cell)

-

视图(view)

-

tsmc18rf名称中的18指的是0.18μm(180nm)的技术节点

-

单元(cell)则是一个电路的基础单位,一个单元就相当于电路的一个模块module,这个模块即可以是低层模块,表示部分电路;也可以是顶层模块,表示整个电路。同一个单元在设计中需要不同的表示方法,例如一个模拟电路模块,在设计内部结构的时候可能需要将它表示为电路图;而在引用该模块的时候则需要将其表示为一个器件符号;在绘制版图的时候可能需要将该模块表示为版图的一个部分。所以一个单元就必须有多种表示方式,称为“Views”。上面举例的模块就可以有电路(schematic)、器件符号(symbol)、版图(layout)三个(View)。在设计中应当保证同一个"Cell”的各个“View”是等效的。 -

cell内名词解释:

-

rm是电阻;

-

mim是电容MIM电容(Metal-Insulator-Metal):MIM电容相当于一个平行板电容(金属-绝缘体-金属电容结构);

-

数字代表最大耐压

-

-

步骤7

放置器件:点击Creat->instance在库里边选(快捷键i)

可以在界面点browse,勾选上方show categories方便选择

鼠标左键是选择,滚轮键是移动,滑轮上下是缩放

原理图全部是黄色怎么办?去工艺库中把display.drf文件(编辑器中显示的颜色等配置)放到工程目录下

步骤12

-

验证时可以双击自己的器件,选择open in new tab可打开新窗口看到内部原理图

-

方波参考设置:voltage1:0V;voltage2:3V;period:2μs;delay time:1ns;raise time:1ns;fall time:1ns;pulse width:1μs

-

地(gnd)可以通过analoglib库添加,也可以选中gnd那条线,按快捷键

L,把name设置为'gnd!'

步骤13

仿真库的文件路径:/home/IC/YIN/tsmc180rf/tsmc180rf_OA/models/spectre/rf018.scs

步骤14

扫描参数仿真Tools -> Parametric Analysis

Schematic编辑

ADE L仿真操作

库管理与工程移植

Library manager是cds.lib文件的图形化显示

在Library manager栏右侧的cell中,右击想要移植的cell进行copy,注意勾选options下的Copy Hierarchical(否则可能在cds.lib中会被注释)与下方的Updata Instances(更新实例化关系,子元素的连接关系)

若工程为只读,元素不可更改,可以从路径找到schematic(原理图)文件夹内删除后缀为.cdslck文件(lock是锁);或者在工程目录内open terminal:find[space].[space]-name[space]"*.cdslck"[space]-exec[space]rm[space]-f[space]{}[space]\; 回车就全删了[space]为空格

删除cdslck文件: find -name "*.cdslck" find -name \*.cdslck | xargs rm 关于这个cdslck文件,会lock掉文件,目的是保护文件,但是有时候阻止修改啥的会烦人,所以删掉cdslck文件。 在CIW窗口输入命令 “exit” 来退出Cadence可以有效的防止cdslck文件出现。

839

839

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?