目录

1.1 概述

⚫符合AMBA规范

⚫8个DMA通道,每个通道都可以支持单向传输。

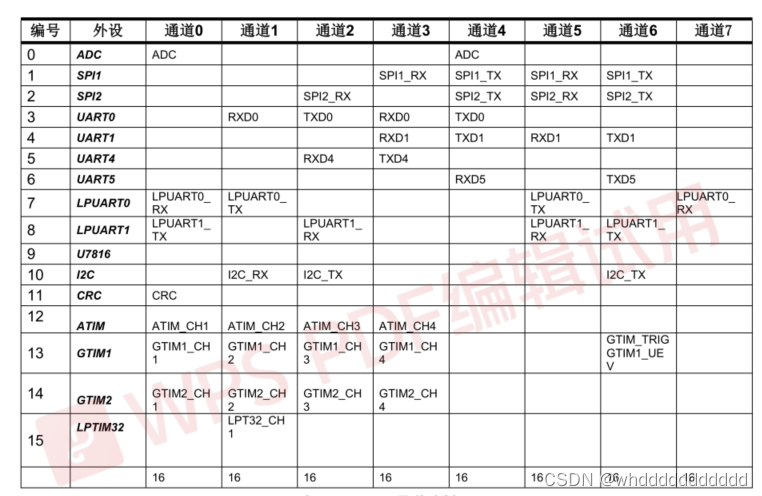

⚫16个DMA请求。PrimeCellDMAC提供16个外围DMA请求线。

⚫单一DMA和突发DMA请求信号。每个连接到PrimeCellDMAC的外围设备都可以断言突发DMA请求或单个DMA请求。DMA突发大小是通过编程PrimeCellDMAC来设置的。

⚫支持内存到内存、内存到外设、外设到内存和外设到外设传输。

⚫硬件DMA通道优先级。每个DMA通道有一个特定的硬件优先级。DMA通道0具有最高的优先级,直到具有最低优先级的通道7。如果来自两个通道的请求同时处于有效状态,那么优先级最高的通道将首先得到服务。

⚫AHBslaveDMA编程接口。PrimeCellDMAC是通过在AHBslave接口上写入DMA控制寄存器来编程的。

⚫两个AHBbusmaster用于传输数据。当DMA请求有效时,这些接口用于传输数据。

⚫32-bitAHBmaster总线宽度。

⚫递增或非递增的源和目标寻址

⚫可编程DMA突发大小。DMA突发大小可以编程以更有效地传输数据。通常,突发大小被设置为外围设备的FIFO大小的一半。

⚫每个通道支持内部4-wordFIFO。

⚫支持8-bit、16-bit和32-bit传输。

⚫支持大端和小端模式,复位时默认为小端模式。

⚫分离和合并DMA错误和DMA计数中断请求。在一个DMA错误或DMA计数达到0时(这通常用来表示传输已经完成)产生一个对处理器的中断。三种中断请求信号被用来做这个:-DMACINTTC在传输完成时发出信号。-DMACINTERR错误发生时发出信号。-DMACINTR是将DMACINTTC和DMACINTERR中断请求信号合并。DMACINTR中断请求可以用于有很少中断控制器请求输入的系统。

⚫中断屏蔽。DMA错误和DMA终端计数中断请求可以被屏蔽。

⚫原始中断状态。DMA错误和DMA计数原始中断状态可以在屏蔽之前读取。

⚫测试寄存器用于模块和集成系统级测试。

1.2 工作原理

(1)、外设DMA为外设和内存的通道,采用外设请求触发方式进行数据传输,每个外设通道都可以支持Peripheral->RAM或者RAM->Peripheral的数据传输,并且根据目标外设类型的不同,自适应选择byte/half-word/word传输方式。DMA作为Master,在收到request后将发起AHBtransactions进行数据操作,外设目标地址根据通道接入选择自动定位,RAM目标地址则根据寄存器配置定位。

(2)、每个channel可以从多个外设中选择一个作为source或destination,同时软件可以设置通道优先级,当两个通道同时要访问RAM时,由优先级决定谁先访问,另一个通道将被挂起,直到优先通道访问完毕。

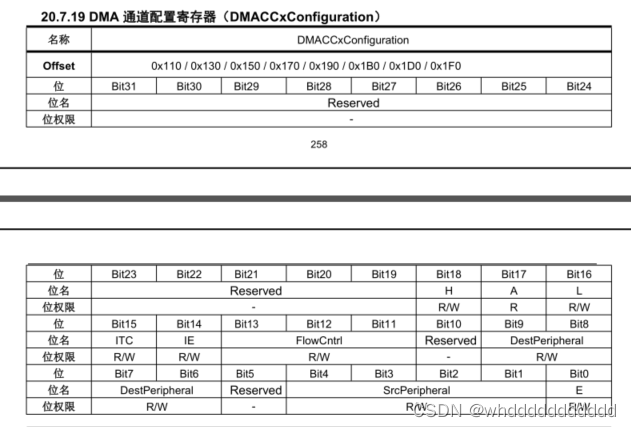

(3)、外设请求可以是准备发送(RAM/Flash->Peripheral)或接收完成(Peripheral->RAM),数据传输通过AHB总线完成,当DMA访问外设时,CPU对同一个外设的访问将引起冲突,哪个Master访问被挂起取决于BusMatrix设置的仲裁优先级。这里需要注意的是,由于大部分外设都被挂在APB总线上,APB映射到AHB仅为一个slave,因此当DMA访问APB中任意外设时,CPU即使访问APB下的其他外设,也同样会引起总线仲裁。通过DMACCxConfiguration(通道配置寄存器)的FlowCntrl可以配置每个通道的传输方向,软件必须保证传输方向配置与实际挂载到这个通道上的外设请求相一致。比如通道1当前挂载的外设请求是UART0接收,则必须将FlowCntrl配置为010(数据从外设读出,写入RAM),每次UART0接收完一帧数据,将发送RXD0请求给DMA,DMA响应请求后,从UART0接收缓存寄存器读取数据,如果DIR被错误的配置为,则DMA对UART0接收缓存寄存器的写操作将被UART0忽略。

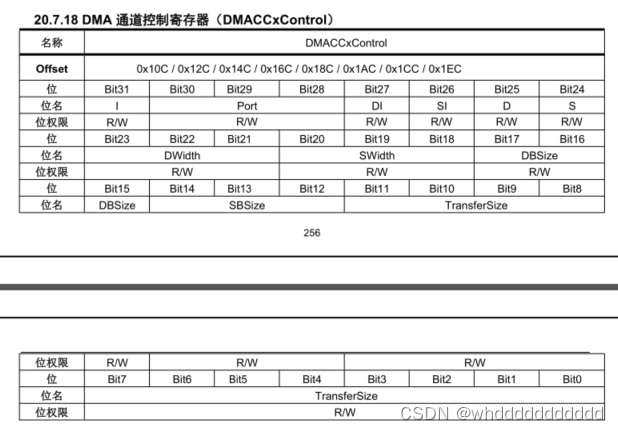

(3)、软件可设置DMA的存储器指针,用于配置DMA传输的起始地址,可以选择指针递增或递减方式。另有DMACCxControl寄存器的TransferSize位配置传输次数,根据起始地址和传输次数,计算得到终止地址,当存储器指针指向终止地址时,本次传输结束,关闭通道。

(4)、在DMA一个完整transferblock完成之前,软件随时可以关闭channel使能,这将导致当前AHB传输(如果正在进行)完成,然后通道被禁用。通道中的所有数据FIFO都会丢失。通过简单地设置通道使能位来重新启动通道会产生不可预测的影响,必须完全重新初始化通道。到达最后一个LLI或遇到通道错误时,通道也被禁用,通道启用位被清除。如果必须在不丢失通道FIFO中的数据的情况下禁用通道,则必须设置暂停位,以便进一步的DMA请求被忽略。然后必须轮询Active位,直到它达到0,表明在通道FIFO中没有数据留下。最后,可以清除通道使能位。

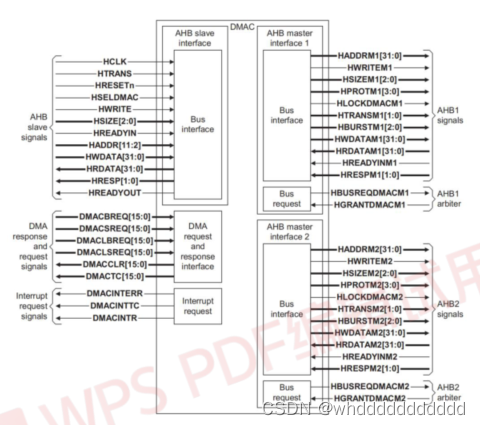

1.3 DMA结构框图

DMA包含两个AHB master接口,一个AHB slave接口,一个DMA响应请求接口,一个中断请求接口。

1.4 工作流程

工作流程分为:通道请求处理与数据搬运过程

通道请求处理:

(a)、DMA接受到请求,跳到步骤b

(b)、判断是否有其他通道正在搬运数,若有,则停留在步骤b直至其他通道当次搬运完成;若无,进一步判断是否有其他同时置起的请求信号,若有,则判断当前通道优先级是否高于其他通道,若是,则跳到步骤c并向数据搬运过程发起请求,若否,则停留在步骤b直至其他通道当次搬运完成

(c)、并等待数据搬运完成响应信号,得到响应则,跳到步骤d,否则停在步骤c

(d)、数据搬运长度+1,判断是否达到设定长度,若是则产生通道使能关闭脉冲;判断请求是否释放,若是,则跳到步骤a,若否,则停留在步骤d判断数据传输达到设定长度,否则跳到步骤a

数据搬运:

(a)、等待通道请求处理过程发起请求

(b)、向HADDR写源地址

(c)、向HADDR写目的地址,同时读取HRDATA

(d)、将读到的HRDATA数据写到HWDATA

(e)、向通道请求处理过程发出搬运完成响应,并跳到步骤a

1.5 通道访问带宽

DMA外设通道支持字节/半字/字访问,每个通道都可以通过通道控制寄存器中的DWidth和SWidth位来配置传输带宽。

1.6 DMA通道映射以及优先级说明

DMA通道优先级是固定的。DMA通道0具有最高的优先级,DMA通道7具有最低的优先级。如果DMA正在为一个较低优先级的通道传输数据,然后一个较高优先级的通道开始有效,在切换到高优先级通道传输数据之前,它要完成由低优先级通道授权给master接口的传输次数。在最坏情况下,这相当于一个四字节。

在DMAC中,两个最低优先级的通道6和7被设计成不会使AHB总线饱和。如果这些较低优先级的通道中的一个被激活,那么DMAC为一个周期的可编程的WIDTH的每4次传输放弃总线,而不管传输的大小。例如,如果可编程的大小宽度是8,那么在8位的4次传输后DMAC放弃总线。这使其它AHBmaster可以访问总线。建议RAM->RAM传输使用这些低优先级通道之一,或者在DMACRAM到RAM传输期间阻止其它低优先级的AHB总线master访问总线。

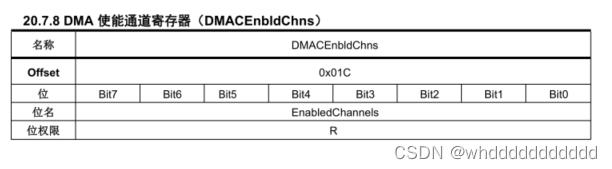

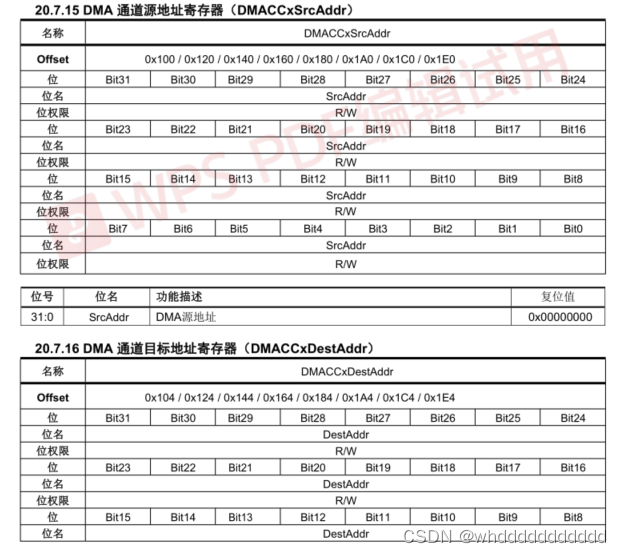

1.7 主要寄存器

本文详细介绍了PrimeCell DMAC的特点,包括8个DMA通道、16个DMA请求、优先级设计、AHB接口、数据传输类型、工作流程、通道带宽配置以及主要寄存器。它探讨了DMA的工作原理,如外设请求触发数据传输、通道请求处理和数据搬运过程,以及如何通过编程控制传输方向和优先级。

本文详细介绍了PrimeCell DMAC的特点,包括8个DMA通道、16个DMA请求、优先级设计、AHB接口、数据传输类型、工作流程、通道带宽配置以及主要寄存器。它探讨了DMA的工作原理,如外设请求触发数据传输、通道请求处理和数据搬运过程,以及如何通过编程控制传输方向和优先级。

698

698

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?