Advanced eXtensible Interface(AXI)是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。

首次是在2003年发布的AMBA3标准中出现,经历AMBA4,目前已经到达AMBA5版本。AXI包括AXI与AXI-Lite两个版本。

注:协议中的前面章节介绍了AXI3/4/5共同遵循的基本协议,有区别的地方会单独介绍或者加以说明。后面会单独介绍AXI4和AXI5的扩展能力和不同的地方。

A1.1 About the AXI protocol

AMBA AXI 协议支持高性能、高频率的系统设计,用于主设备和从设备之间的通信。

AXI 协议的特点包括:

- 适用于高带宽,低延迟的设计[1]

- 不需要通过复杂的桥转换就可以实现高频下的操作

- 满足多种组件的接口要求[2]

- 适合于高初始化访问延迟的内存控制器[3]

- 支持灵活的实现互联结构

- 可以向下兼容AHB,APB等接口

注:[1]例如,最大支持1024bit数据位宽,可运行在1GHz频率下,则理论带宽可达128GB/s(单向)。

[2]目前大部分高速外设接口IP都支持AXI接口,例如PCIe、DDR、USB等。

[3]内存控制器在初始化或者重置时需要准备和配置,从而造成比较大的访问延迟。AXI的某些特性可以确保在启动或重置期间,系统能够高效、稳定地处理内存访问请求,从而提高系统的整体性能和可靠性

[4]目前市场上大部分的嵌入式系统的内部总线使用的都是AMBA总线。

AXI 协议的关键特点包括:

- 独立的地址/控制和数据周期。[1]

- 支持使用字节选通指示的未对齐数据传输。[2]

- 支持仅需要发出起始地址的突发事务。[3]

- 独立的读和写数据通道,能够提供低成本的直接内存访问 (DMA)。[4]

- 支持发出多个未完成地址(outstanding传输)。[5]

- 支持无序事务完成(out-of-order)。[6]

- 允许灵活的添加寄存器以实现时序收敛。

注:[1]是的数据可以先于地址发出,提高传输效率;

[2]地址对齐传输一方面会浪费带宽,另一方面灵活性不足,是的软件设计复杂;

[3]突发事务是AXI提高效率的一种方式,对于访问连续地址空间的数据尤其明显。

[4]DMA直接内存访问,是指设备可以不通过CPU直接通过总线访问内存数据,减轻了CPU的负担;

[5]outstanding是指请求者发出请求后不必等待该请求的响应完成,就可以继续发送剩余的请求。例如,读取请求发送地址A后,不用等到数据的返回,就可以继续发送地址B、地址C的请求。

[6]out-of-order: 被请求者可以不用按照请求者发出的请求顺序来恢复响应。例如,请求者发出的请求顺序为读地址A、写地址B、读地址C,被请求者可以根据自身的情况,选择先回复地址C的数据,再回复写地址B的响应,最后回复地址A的数据。

AXI 协议包括:

AXI4-Lite,这是 AXI4 的一个子集,用于与组件内简单控制寄存器接口的通信。参见 B1 节 AMBA AXI4-Lite。

AXI5-Lite,这是 AXI5 的一个子集,用于在组件内使用 AXI5 特性的简单控制寄存器风格接口。参见 C2 节 AMBA AXI5-Lite。

注:AXI5-Lite是AXI5的简化版本,适合低带宽、低复杂度的应用场景,而AXI5则提供了高性能和灵活性的特性,适合复杂系统设计。主要区别体现在协议的复杂性、传输模式的支持、数据通道的支持、应用场景、性能等方面

A1.2 AXI Architecture

AXI协议是基于突发(burst)的,并定义了五个独立的事务通道:

- 1 读地址通道,信号名称以AR开头。

- 2 读数据通道,信号名称以R开头。

- 3 写地址通道,信号名称以AW开头。

- 4 写数据通道,信号名称以W开头。

- 5 写响应通道,信号名称以B开头。

注:相比于APB和AHB总线,AXI总线的最大特点是读写分为不同的通道,可以实现读写同时进行。并且busrt传输支持的数据量更大。

注:burst传输,突发传输,发送一次地址,可以连续发送大量的数据(有burst属性决定)。

地址通道(包括读地址通道和写地址通道)主要描述要传输的数据性质的控制信息。

传输的数据则是以以下方式在主设备和从设备之间进行传输;

- 写数据通道:用于将数据从主设备传输到从设备。在写事务中,从设备使用写响应通道向主设备传输写事务的完成情况。

- 读数据通道:用于将读取的数据从从设备传输到主设备。

AXI协议具有以下特点:

- 允许地址信息在实际数据传输之前发出。

- 支持多个未完成的事务。outstanding

- 支持事务的乱序完成。out-of-order

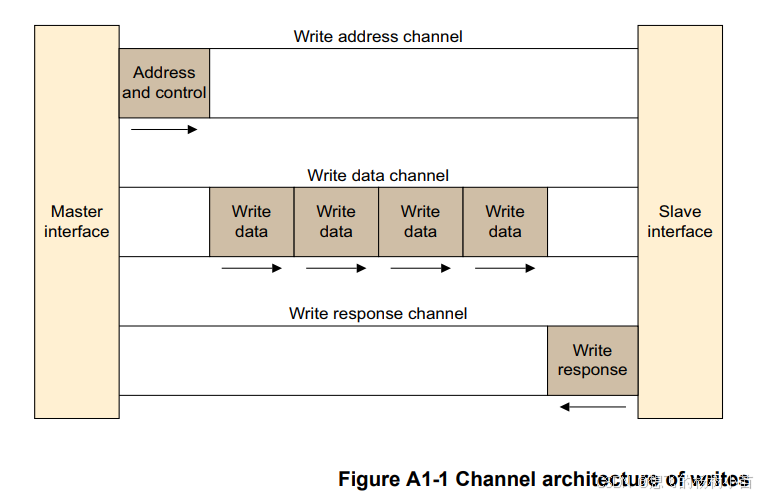

图A1-1展示了写事务如何使用写地址、写数据和写响应通道进行数据传输。

注:[1]写地址通道的时序与写数据通道的时序没有前后关系,可以提前,也可以同时,也可以在写数据之后发出。但写响应通道的信号必须在写数据、写地址完成之后发生。

[2]写数据通道上的数据间隔无要求,可以连续周期发出,也可以中间有间隔,但数据的前后顺序不能改变。

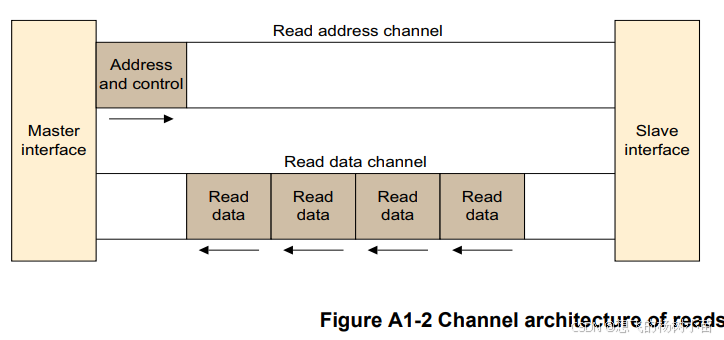

图A1-2展示了读事务如何使用读地址、读数据通道进行数据传输。

注:[1]读数据通道必须在读地址通道之后发生。应为设备如果不知道读取的数据地址,则无法返回相关数据。

[2]读数据通道上的数据间隔无要求,可以连续周期发出,也可以中间有间隔,看从设备的行为,但数据的前后顺序不能改变,按照地址依次传输。

A1.2.1 Channel definition

每个独立的通道由一组相关信号以及 VALID 和 READY 信号组成,并使用双向握手机制。

- 信号发出者使用 VALID 信号来指示通道上的地址、数据或控制信息何时可用。

- 信号接受者使用 READY 信号来指示何时可以接收信息。

- 读数据通道和写数据通道还包括一个 LAST 信号,用来指示事务中最后一个数据项的传输。

注:[1]即地址、控制、数据信息只有在VALID和READY同时为高时才有效。

[2]写/读数据的最后一笔有效时,VALID和READY和LAST信号同时为高。

读地址通道和写地址通道

读事务和写事务分别有各自的地址通道。地址通道承载了事务所需的所有的地址和控制信息。

读数据通道

读数据通道包括从设备传送到主设备的读数据和读响应信息,包含:

- 数据总线,宽度可以为 8、16、32、64、128、256、512 或 1024 位。

- 表示读事务完成状态的读响应信号。

写数据通道

写数据通道包括主设备传送到从设备的数据信号,包含:

- 数据总线,宽度可以为 8、16、32、64、128、256、512 或 1024 位。

- 每八个数据位都有一个字节通道时钟信号,指示有效数据字节。

注:写数据通道上的数据和信息被认为可以被从设备进行缓存的,也就是说,即使当前写数据通道上的信息发出去之后还没有收到从设备的相应之前,继续执行其他写事务的。

写响应通道

从设备使用写响应通道来响应写事务。所有写事务在写响应通道上都需要完成信号。

注:完成信号仅针对完整事务发出,而不是针对事务中的每个数据传输。

注:五个通道为独立的通道,可大大提供系统传输性能。需要注意读操作有2个通道,写操作有3个通道,读通道中没有单独的响应通道,读响应与读数据共用一个通道传输,都是slave一块返回没有必要分离。

A1.2.2 Interface and interconnect

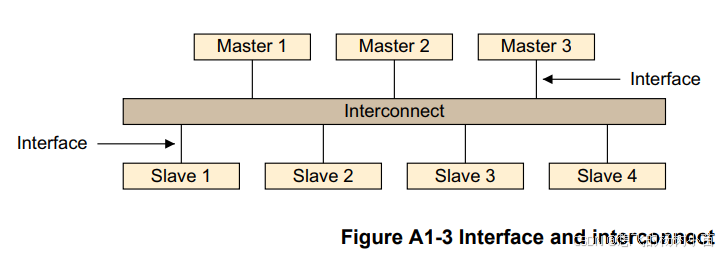

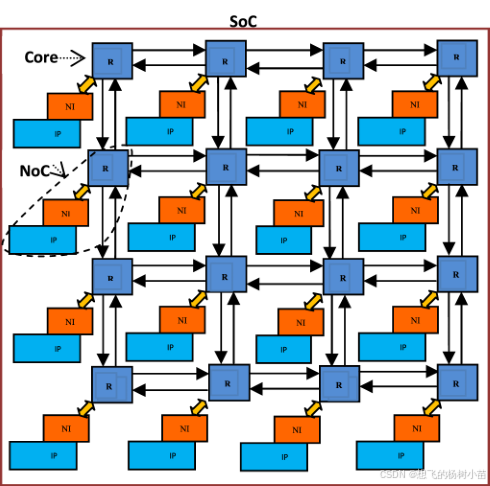

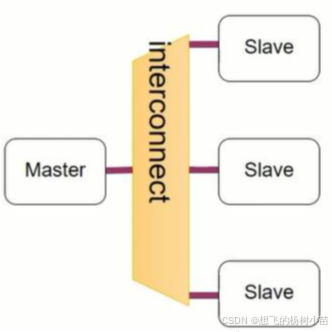

一个典型的系统由多个主设备和从设备组成,这些设备通过某种形式的互连连接在一起,如图A1-3所示。

AXI协议为以下设备的互联提供了接口定义:

- 主设备与互连组件(interconnect)之间

- 从设备与互连组件(interconnect)之间

- 主设备与从设备之间

该接口支持多种不同的互连实现。

Note:设备之间的互连组件(interconnect)等同于一个设备,具有主端口和从端口,真实的主设备和从设备可以连接到这些端口上。

典型的系统拓扑

大多数系统使用以下三种互连拓扑:

- 共享地址和数据总线

- 共享地址总线和多个数据总线

- 多层互连,具有多个地址和数据总线

在大多数系统中,地址通道的带宽需求显著低于数据通道的带宽需求。这类系统可以通过使用共享地址总线和多个数据总线来实现系统性能与复杂性之间的良好平衡,从而实现并行数据传输。

注:对于互连组件(interconnect)的举例:

1、crossbar拓扑,例如ARM NIC-400

2、mesh拓扑,例如ARM CMN-700

3、直接相连,一对多

4、多层次拓扑

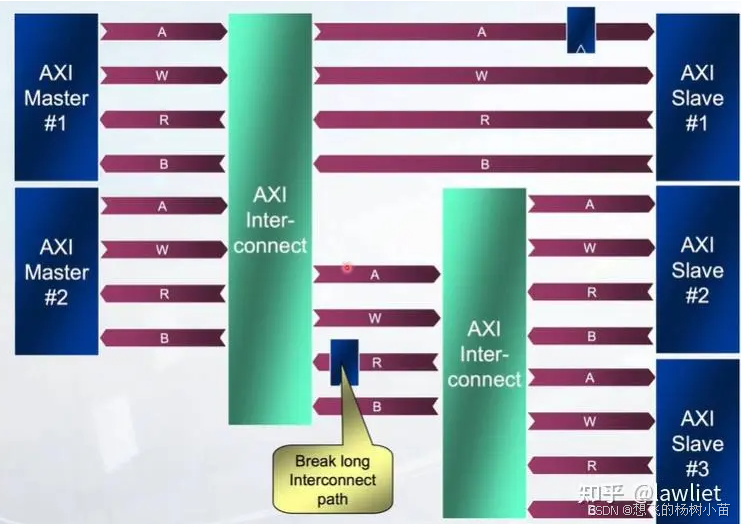

A1.2.3 Register slices

每个 AXI 通道仅以单一方向传输信息,且该架构不要求通道之间存在任何固定关系。这些特性意味着可以在任意通道的任意位置插入寄存器来满足时序要求,代价是增加一个额外的延迟周期。

这些特性使以下事项成为可能:

- 在延迟周期和最大操作频率之间进行权衡。

- 在处理器与高性能内存之间建立直接、快速的连接,同时使用简单的寄存器来隔离较长路径以连接性能要求不那么关键的外设。

A1.3 Terminology

本节总结了本规范中使用的术语,这些术语在术语表或其他地方有定义。。

A1.3.1 AXI组件和拓扑

以下术语描述了AXI组件:

- 组件

- 主组件

- 从组件,包括内存从组件和外设从组件

- 互连组件

在特定的AXI事务中,“上游”和“下游”指的是AXI拓扑中AXI组件的相对位置。

A1.3.2 AXI事务和内存类型

当AXI主设备发起针对AXI从设备的AXI操作时:

- 在AXI总线上所需的完整操作集构成了AXI事务

- 任何所需的有效载荷数据作为AXI突发传输

- 一次突发可以包含多个数据传输,或称为AXI节拍(AXI Beats)

A1.3.3 缓存和缓存操作

本规范不定义标准的缓存术语,这些术语在有关缓存的参考文献中都有定义。然而,术语表中对“缓存”(Cache)和“缓存行”(Cache line)的条目阐明了这些术语在本文档中的用法

3085

3085

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?