Verilog实战学习到RiscV芯片设计 - 0

文章目录

引言

在FPGA设计领域,大公司的商用工具链通常价格高昂,且安装包体积庞大,给许多个人开发者和小型企业带来了不小的挑战。为了降低进入门槛,并促进创新,近年来一系列强大且免费的开源FPGA工具链得到了广泛的关注和使用。本文将为大家介绍一套完整的开源FPGA设计工具链,包括Yosys、Icarus Verilog、Netlistsvg、Nextpnr、Icestorm。

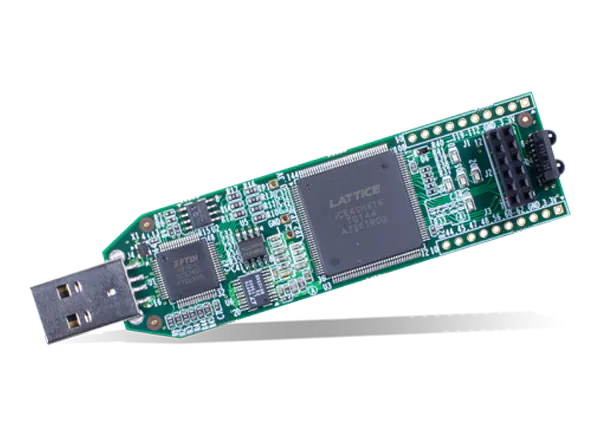

我们将使用Lattice公司的Ice40系列评估板IceStick实践我们的例程,包括最后的RiscV开发。

工具链介绍

Yosys

Yosys是一个功能强大的开源逻辑综合工具,能够将Verilog HDL描述的数字电路综合为网表。它支持多种综合策略和优化方法,能够生成高效的逻辑设计。Yosys的灵活性和可扩展性使其成为开源FPGA工具链中的核心组件。

Icarus Verilog

Icarus Verilog是一个开源的Verilog仿真器,支持Verilog-2005标准。它可以用于前仿真,帮助设计者验证设计的正确性。在开源工具链中,Icarus Verilog与Yosys配合使用,提供了从设计到仿真的完整解决方案。

Netlistsvg

Netlistsvg是一个用于生成网表可视化图形的工具,可以将Yosys生成的网表文件转换为SVG格式的图形。通过图形化的方式,设计者可以更直观地理解和分析电路设计的结构和连接关系。

gtkwave

gtkwave是一个功能强大的波形查看工具,用于查看由仿真器生成的波形文件。它支持多种波形格式,如VCD、LXT和FST,可以帮助设计者详细分析和调试电路的时序行为。结合Icarus Verilog,gtkwave为设计者提供了完整的仿真和调试解决方案。

Nextpnr

Nextpnr是一个灵活的开源FPGA布线器,支持多种FPGA架构。它接收由Yosys生成的网表,并将其映射到FPGA的具体硬件资源上。Nextpnr的开源性质允许用户根据需要进行定制和扩展,以适应不同的设计需求。

Icestorm

Icestorm是一个面向Lattice iCE40系列FPGA的开源工具链。它包括多个工具,可以将综合后的网表转换为iCE40 FPGA的配置位流文件。Icestorm为小型、低成本的iCE40 FPGA提供了全面的开源支持,是FPGA开发者不可或缺的工具之一。

Workflow 工作流

一般的FPGA开发的IDE会包含的工具链包括:

- 综合

- RTL电路图

- RTL仿真

- 实现(布局 + 布线)

- 生成比特流

- 下载到FPGA

以上介绍过的开源工具分别对应到每一步分别是:

- 综合: Yosys

- RTL电路图: Netlistsvg

- RTL仿真: Icarus Verilog + gtkwave

- 实现(布局 + 布线): Nextpnr

- 生成比特流: Icestorm

- 下载到FPGA: Icestorm

系列文章展望

本系列文章将以实践操作为主,逐步介绍如何使用上述开源工具链进行FPGA设计。我们将提供详细的教程和Verilog关键例子,帮助读者掌握每个工具的使用方法和设计流程。最后,我们还将动手实验一个开源的RISC-V设计,展示如何在实际项目中应用这些开源工具。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?