1.前仿:零延迟仿真

前仿(功能仿真、行为级仿真、RTL级仿真):针对不带任何延迟信息的RTL代码进行的功能验证。

2.后仿:带真实的反标延迟仿真

后仿(时序仿真):采用后端工具生成的SDF文件对布局布线后的门级网表进行的时序和功能验证。

后仿有两种说法,一种是综合后仿真:对DC综合后的网表进行仿真,连线延迟来自于线负载模型的估计;另一种是布局布线后仿真:对布局布线后的网表进行仿真,连线延迟来自于版图的提取。(验证中的后仿一般是针对布局布线后的仿真)

后仿也叫动态时序仿真,相比于静态时序分析STA(针对同步电路设计中时序分析),它主要应用在异步逻辑、多周期路径、错误路径的时序验证中。

SDF文件介绍

SDF(standard delay format):描述电路布局布线后单元及互联线的延时数据,主要作用是将延迟信息反标(back annotation)到功能模型中,模拟芯片在真实工作时的状态。

反标SDF文件有两种方法:一种是作为elaboration的选项指定,一种是使用系统函数$sdf_annotate来完成。

3.芯片后仿违例类型:

1、Setup/hold违背(posedge D -> posedge CK , negedge D -> posedge CK)

2、Recovary/Removal违背 (posedge CDN -> posedge CK ,posedge SDN -> posedge CK)??

3、Width违背 (CK,CDN,SDN)

4、IP接口时序不符合datasheet?外设器件是否也需要带延时的model?

4.后仿的意义

后端一般会进行静态时序分析(STA),静态时序分析根据一定的模型从网表中创建无向图,计算路径延迟的总和,如果所有的路径都满足时序约束和规范,那么认为电路设计满足时序约束规范。静态时序分析的方法不依赖于激励,且可以穷尽所有路径,运行速度很快,占用内存很少。对于同步设计电路,可以借助于静态时序分析工具完成时序验证的任务,但是不能对异步电路进行时序分析。所以如果设计中存在异步电路,就要借助于后仿真。

后仿真主要意义在于:

1、确认异步路径、multi cycle path、false path。

2、功能仿真不包含的信息,如DFT插入的扫描链,或者基于工艺单元的功耗评估以及时序信息等。

3、检查时序约束(SDC)的正确性,防止约束错误。

4、检查网表的完备性,防止综合、布局布线过程中的意外错误。

5、为后续流程如功耗分析、IR drop分析提供波形(后仿波形分析更准确)。

6、完整的系统初始化上电处理流程和复位流程,尤其是面对系统中存在不定态的情况。

由于后仿真较为耗时,一般不会将所有的前仿case都进行后仿,通常的做法是挑出一部分进行后仿即可,而case的挑选可以基于以上几点,将有风险的case挑选出来进行仿真。

5.SDF延迟反标注方法:

方法一:使用$sdf_annotate将SDF文件反标到网表中:

$sdf_annotate("sdf_file" [,module_instance] [,"sdf_configfile"] [, "sdf_logfile"] [,"mtm_spec"]

[, "scale_factors"] [, "scale_type"]);

其中,module_instance是例化的模块名,例如在testbench中,例化顶层:

digital_top digital_top_u

digital_top_u是例化的模块名,那么按照上面的格式,在testbench中添加下列代码:

initial begin

$sdf_annotate( "fast.sdf" ,digital_top_u , , “fast_sdf.log" ,"MAXIMUM" , , );

end

sdf_file: sdf文件;(此例中sdf文件名为fast.sdf)

module_instance:调用$sdf_annotate模块实例的范围;

sdf_configfile:指定SDF配置文件;

sdf_logfile:生成所有的sdf反标错误的文件,需在编译时使用+sdfverbose。

mtm_spec:指向哪一种延时类型,通常有三种min,typ,max,分别表示最小延时,常规延时,最大延时。对应写在$sdf_annotate函数中是"MINIMUM", "TYPICAL", "MAXIMUM"。

在仿真器读入SDF的时候,要指定使用哪一组。

scale_factors:指定min:typ:max的缩放因子,默认为三个正实数“1.0:1.0:1.0”。

由于是默认参数,所以在上面的$sdf_annotate( "fast.sdf" ,digital_top_u , , “fast_sdf.log" ,"MAXIMUM" , , ); 中的对应位置用空格表示,也可以不用空格,用空格对应参数看起来更清楚。

scale_type:指定SDF文件中缩放前使用的延迟值,它可能的值是"FROM_TYPICAL",

"FROM_MINIMUM" , "FROM_MAXIMUM"和默认"FROM_MTM";

此项参数也是默认,同样在$sdf_annotate函数中对应位置可以用空格来表示。除sdf_file必须要给出以外,其他参数都可以使用默认值,用空格来表示,也可以不用空格。

VCS编译指令:-full64 -kdb -sverilog -f vflist -l com.log -debug_access+all +vcs+vcdpluson +negdelay -sdfretain +sdfverbose

Notes:其中testbench,dut.v,sdf文件放在同一层目录(同一个文件夹),但vflist里面只需要有testbench和dut.v的文件名,不需要把sdf文件的名字写进去,因为sdf文件已经用$sdf_annotate函数调用了。

如何确认成功反标?

编译完成后,可以从终端或者log文件中看到这么一句话:

SDF annotation completed.

同时也会显示反标过程中有多少个error和warning。

方法二:VCS编译器配置

在VCS编译指令中加上 -sdf min|typ|max:instance_name:file.sdf,

具体格式为 -sdf max:tb_digital_top.digital_top_u:fast.sdf

其中,tb_digital_top为testbench的模块名,digital_top_u为顶层的例化名。

同时编译选项加上 +neg_tchk -negdelay -sdfretain

注意VCS编译指令中最大延时用max表示,在$sdf_annotate函数中最大延时用MAXIMUM表示。

Notes:关于后仿的延时文件fast.sdf以及slow.sdf,前者表示快的,后者表示慢的。fast.sdf检查hold时间,slow.sdf检查setup时间,越慢setup越不容易满足,越快hold越不容易满足。

其中,sdf反标注有延迟类型的选择,分最坏,最好,最常用三种情况,最坏情况:slow对应max,fast对应min。

Tips:如果需要对多个例化的模块进行延迟反标注,可以在testbench里面,用多个$sdf_annotate,分别用来标注需要反标的模块。

较为常见的方法是在bench中调用系统函数$sdf_annotate来完成。还有其他的方法,比如作为elaboration的选项指定等。$sdf_annotate的标准格式如下:

$sdf_annotate(“sdf_file”[,module_instance][,“sdf_configfile”][,“sdf_logfile”][,“mtm_spec”][,“scale_factors”][,“scale_type”]);

其中:

“sdf_file”:指定SDF文件的路径。

“module_instance”:指定反标设计的范围(scope)

“sdf_configfile”:指定SDF配置文件

“sdf_logfile”:指定VCS保存error 和warnings消息的SDF日志文件。也可以使用+sdfverbose runtime option来打印所有反标消息

“mtm_spec”:指定延迟类型"MINIMUM(min)", "TYPICAL(typ)“或者"MAXIMUM(max)”。

“scale_factors”:分别指定minmax的缩放因子,默认是"1.01.0"

“scale_type”:指定缩放之前延迟值的来源。

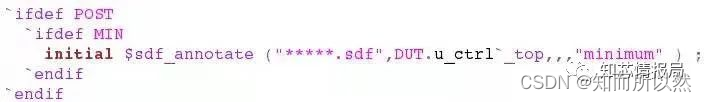

如下图举例:

在反标SDF后,specify块中定义的延迟不再有用,取代的将是SDF文件中的延迟。

6.参考链接:

芯片后仿相关记录_sdf max min_ASIC_DBGer的博客-CSDN博客

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?