状态:特征是会保持一段时间的,不会突变。

时序(sequential ,顺序)电路:预测输出会怎么变化,是由当前状态和输入决定。(时序电路的特征和时钟没关系)

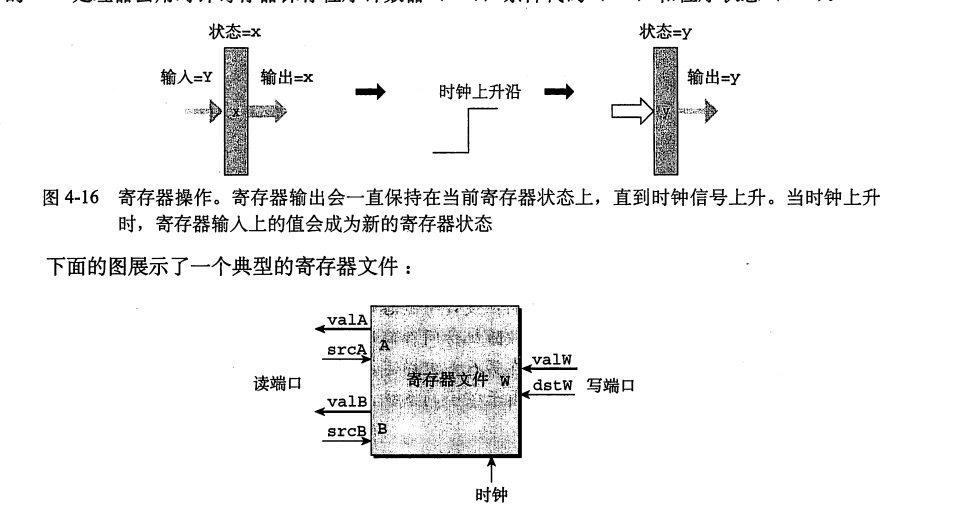

寄存器和时序逻辑什么关系。!!!!! 通过控制逻辑(时钟信号与地址为输入),控制存储器是否接受时钟信号的控制,若接受,则存储器,实际就是钟控触发器(在上升沿时,触发器接受输入)。 见下图(指反映写的情况)。

不是内部存在着时序电路的电路,就存在时序电路的特征(输出反馈到输入,改变输入时,输出当前的输出也称为输入一部分)。 触发器是时序电路,随机访问存储器(包括寄存器文件)是由触发器构成的,但是在读取数据时,存储器就类似于组合电路了。

寄存器——. :

特点:(1)输出不是简单的等于输入的某个函数(组合电路特征。),而是在时钟控制下响应。 否则输出和输入没关系,保持状态(输出)。

(2)在使能输入0情况下,状态保持不变,时钟控制响应寄存器响应了,结果发现使能输入为0,则仍然保持输出状态。

结论:寄存器输出状态的改变,需要两个条件,1. 时钟控制允许 2.输入对于当前状态对应的输入发生改变。 3. 使能端为0。 3个条件是并的关系。

寄存器文件实现原理(即随机访问存储器实现原理): 有读端口和写端口,每个端口都包含数据信号通路和地址输入。

(1)当读取时,地址输入可以选取某一个寄存器,即寄存器输出信号电路接上了端口的输出信号电路,所以可以看成,读取数据好像就是一个以地址为输入,数据为输出的一个组合逻辑电路块,实际是使能作用。(实际上,地址线和数据线是总线,即接到了每个寄存器,所以地址线是使能线,选取某个寄存器,即某个寄存器能接受输入)

(2)当写过程时,数据需要存储在寄存器的“输出”上。 所以地址输入选中存储的寄存器,数据输入信号电路接上寄存器输入电路,再时钟控制允许,则写入成功。

(3)数据保存过程,当使能为0,寄存器不受任何输入影响。

所以,寄存器要集成为寄存器文件,上图4-16还需要加入使能输入端(即地址线),时钟控制信号线。

指令处理对应的数字电路过程(牵涉到内存读写,寄存器读写),

取指:在该周期,PC寄存器输出( 地址),使能了存储器PC和PC+1字节的存储,icode:ifun,ra:rb信号在数据总线上。

译码:总线RA,RB字段接到寄存器文件的地址输入(寄存器是多端口,可以同时读写多个寄存器),读取是使能,不用时钟。

执行:寄存器文件输出接到ALU的数据输入,总线的func字段接到ALU的控制输入. ALU组合电路计算,输出VALE。

访问:

写回:VALE信号线接到R[rb],等到时钟到来就能写入

更新PC:PC+2信号接到PC,等到时钟到来就能写入

这是SEQ处理器的模式,一个周期处理一条完整的指令,非流水线。

864

864

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?