随着算法对处理器计算能力要求不断提高,项目定位于研发一款高性能的视觉处理平台,经过多方验证确定采用TI公司Keystone结构的C665X DSP作为核心处理器。项目正式立项于2016年10月份,设计处理平台原理图花费1个月时间;委托兴森快捷公司进行PCB Layout、制版焊接大约花费2个多月时间;调试硬件和编写底层驱动大约花费3个月时间,项目于2017年5月底调试大体结束。

文章主要是记录开发的大体过程,留作以后进行回顾与参考。

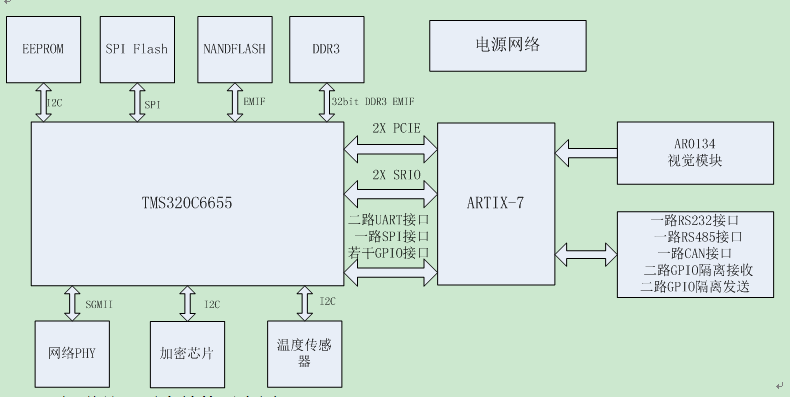

C665X视觉处理平台结构示意图

数据流程

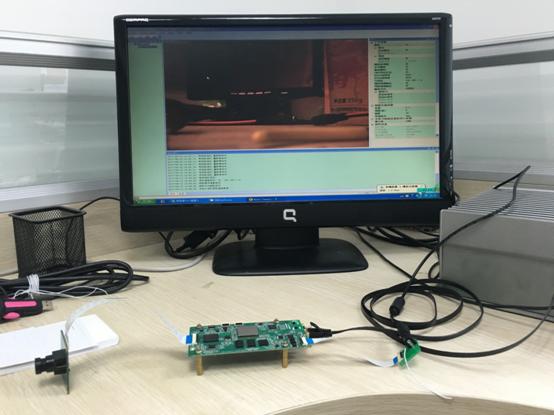

AR0134视觉模块产生的视频信号,按行发送到Artix-7上,Artix-7按行对数据进行打包,通过PCIE总线传输给TMS320C6655,同时统计发送数据的大小,如果达到一帧数据大小,就向TMS320C6655发送PCIE断信号,通知一帧图像数据传输完毕。TMS320C6655随即开始对该帧图像数据进行算法处理或者通过SGMII接口发送PC上。Artix-7对外提供24bit的数字接口(3.3V/1.8V),也就是说处理平台既可以接收AR0134发送的数字信号,又可以接收AD芯片产生的数字信号,使用比较灵活,不单单针对图像数据。

注:ARTIX-7和TMS320C6655进行通信大体上存在三种方式,UPP、PCIE、SRIO,如果使用UPP进行通信会占用大量的管脚,且通信效率比较低,和定位于高性能的视觉处理平台标准不符,PCIE和SRIO速率和性能等方面大体类似,最终比较起来SRIO稍占优势,但是在FPGA程序开发的时候,SRIO IP核需要向Xilinx公司购买License,而PCIE则不需要购买,出于成本的考虑,最终采用PCIE2X作为通信协议。

技术指标

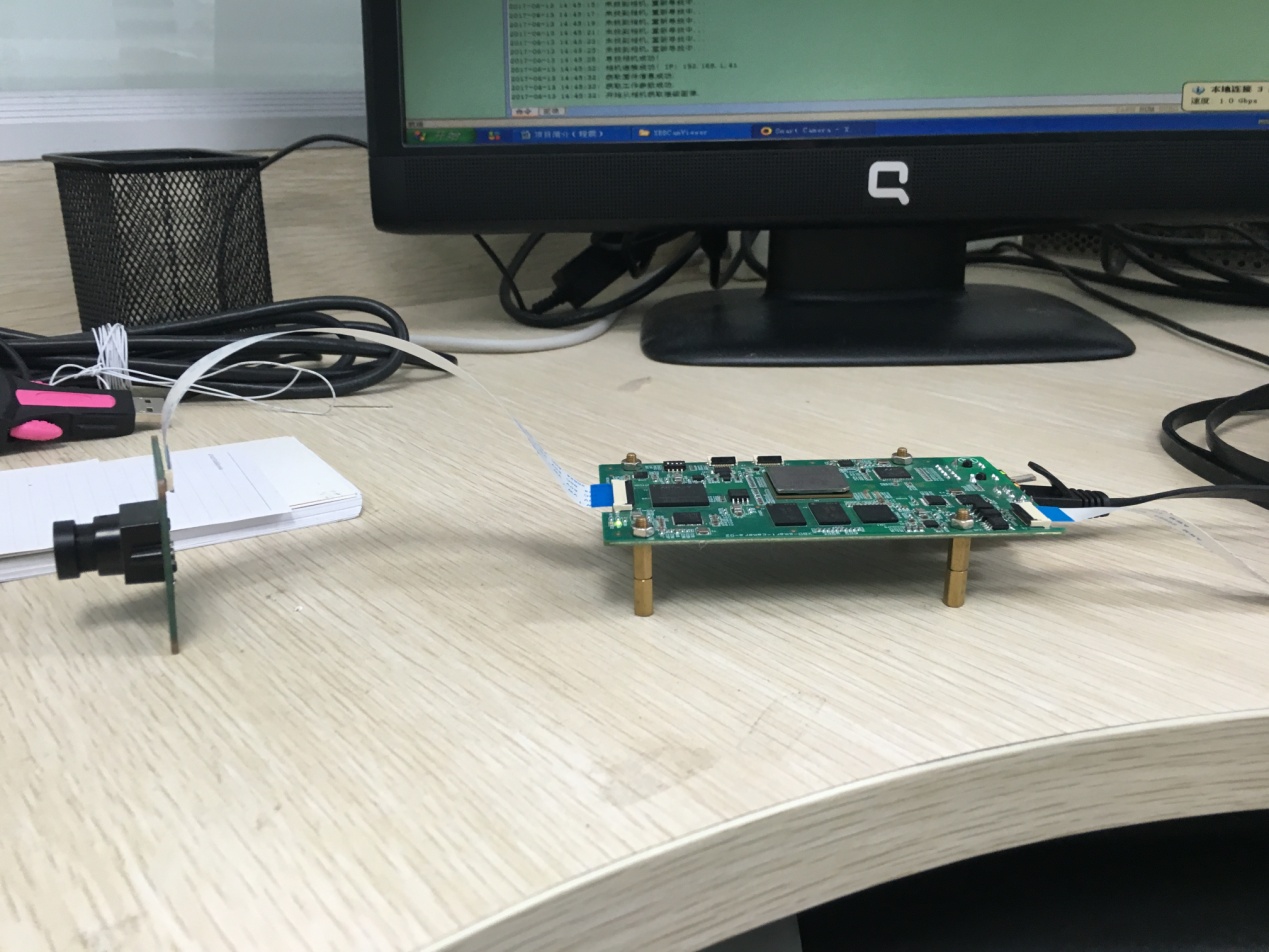

1、 核心处理器采用TI TMS320C6655 ,FPGA平台采用Xilinx XC7A35T

2、 电源输入9V~30V,在输入处进行了过流保护和过压保护

3、 DDR3 存储大小256MB 时钟频率1333Hz

4、 NAND Flash 存储大小 128MB;EEPROM 存储大小 1MB; SPI FLASH 存储大小8MB

5、 加密芯片 DS28CN01; 温度传感器TMP102

6、 一路1000Mbps网口;一路RS232接口;一路RS485接口;一路CAN接口;二路GPIO光电隔离输出;二路GPIO光电隔离输入

7、 一路24bit通用数据接口,可接AD芯片、CMOS等。

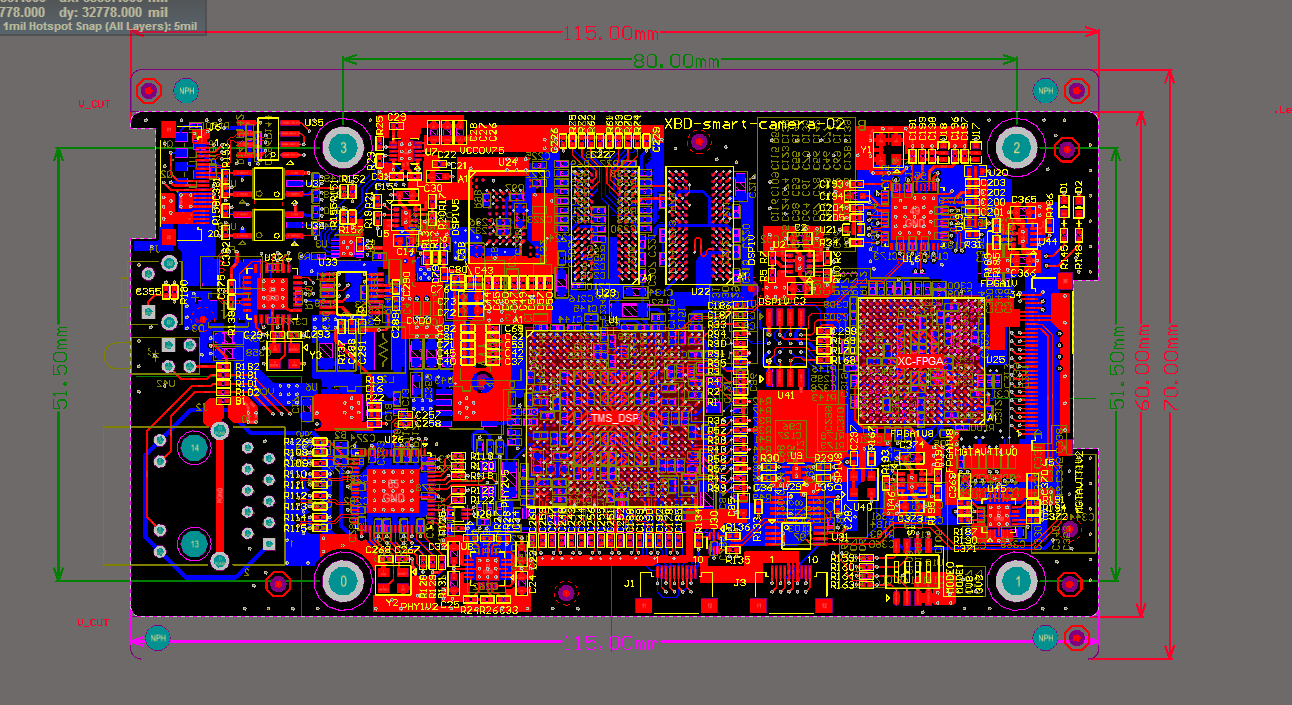

原理图&PCB设计

设计软件使用的是Altium Designer15,主要参考的资料Hardware Design Guide for KeyStone I Devices文档;还有TMS320C6657EVM网址是:

注意:在电源CVDD设计的时候,按照文档Hardware Design Guide for KeyStone I Devices的描述有两种方式1、LM10011 and Analog Controller Solutions 2、UCD92xx Digital Controller Solutions。在TMS320C6657EVM使用了第二种方式,但是由于电路比较复杂,而且上电需要配置比较复杂,建议使用第一种方式。

开发板的尺寸115mmX60mm,设计使用了10层,TOP-GND-SIG-GND-SIG-GND-POWER-SIG-GND

-BOTTOM,可以看到上面设计使用4层GND,在实际生产中可以将中间两层GND去掉。

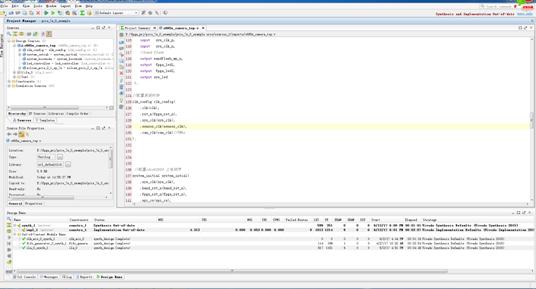

FPGA驱动开发

FPGA驱动开发使用开发工具是Xilinx公司Vivado2015.4,FPGA主要工作大体有三个:1、在平台启动的时候,控制电源芯片的上电顺序、配置可编程时钟芯片、配置DSP启动的工作模式;2、将接收的数据打包通过PCIE总线发送给DSP;3、对管脚进行逻辑管理,譬如LED闪烁、电平转换等。

其中最为复杂的是PCIE总线开发,需要对PCIE协议大体理解,可以参考王齐 PCI Express体系结构导读。

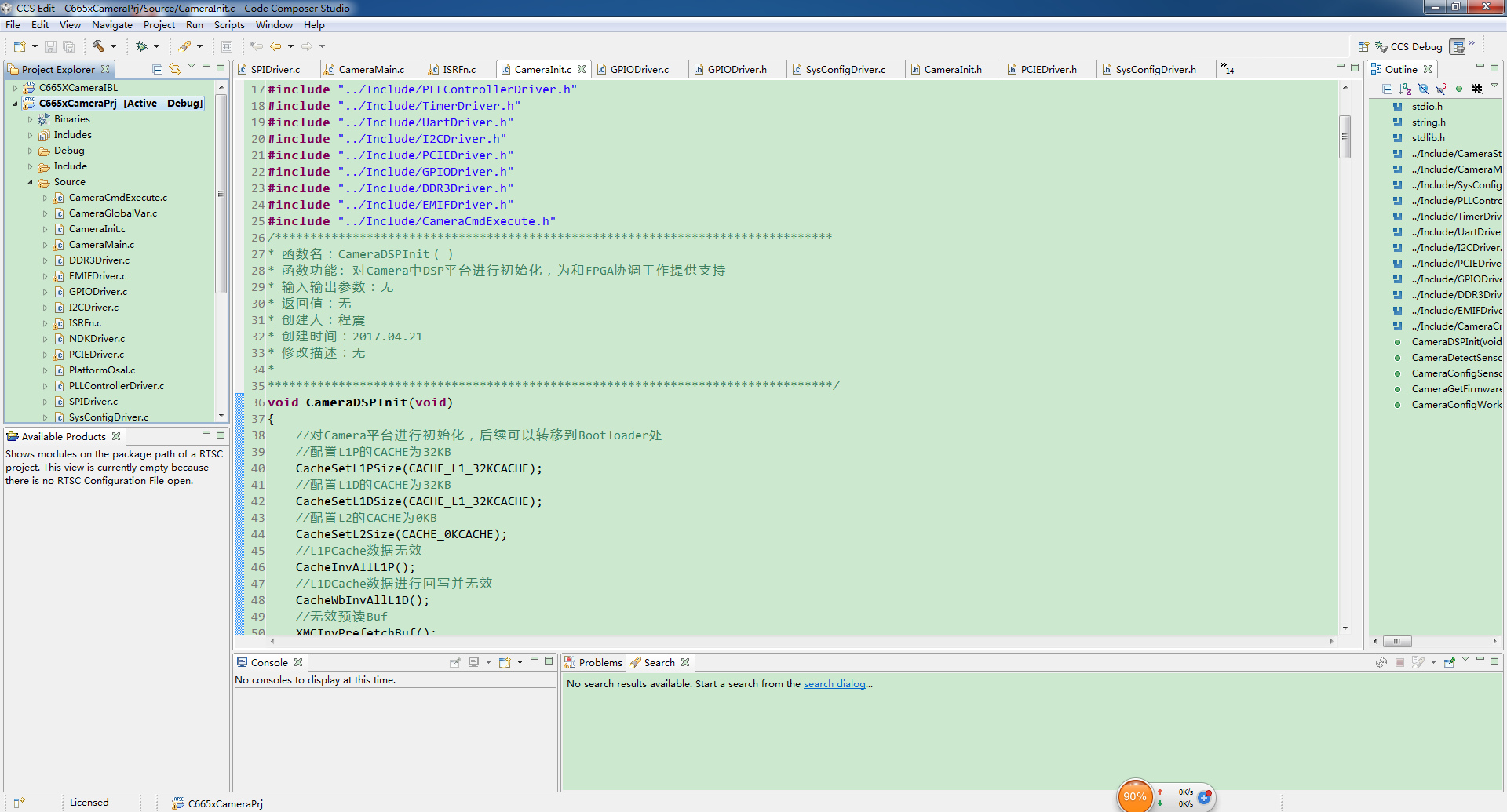

DSP驱动开发

DSP驱动开发使用的TI的CCS5.5编译器。按照工程的不同,可以分为BootLoader工程、Flash烧写工程、App应用工程。

BootLoader工程:主要是在系统启动时运行,对系统进行初步配置(DDR3、PLL、Cache、PSC等),根据Flash中的标志解析对应应用程序。这里涉及到out文件解析,应用程序首地址定位等,在这不再展开,后面将单独在博文中阐述。

Flash烧写工程:将App应用工程和BootLoader工程编译的out文件烧写在指定位置。

App应用工程:为了驱动外设的正常工作需要编写Cache、DDR、PLL、PSC、SPI、I2C、UART、EMIF、GPIO、PCIE、中断等驱动来操作相关外设;由于平台通过网络和PC进行通信,需要加载TI NDK网络协议栈进行支持;随着任务不断增多,任务之间、任务和中断之间等,需要调用嵌入式操作系统SYS BIOS进行协调。

实物图

如有问题需要讨论,微信open_chengzhen qq 123186738

9239

9239

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?