Interposer 是一种用于连接芯片的中间层技术,它的基底通常是一块硅基底,而硅基底也是 Substrate 的一种。因此,Interposer 与 Substrate 有一定的关系。对于RDL Interposer来说,Si Interposer的信号布线密度进一步提高,可以实现更高的 I/O 密度以及更低的传输延迟和功耗。然而与有机基板及RDL Interposer 相比,Si Interposer 的成本更高。

下面详细讲解关于这部分的相关概念

一、Substrate(衬底或基板)

衬底和基板用英文中的单词substrate来表示,衬底是指用于电子产品封装的板材,它提供了电子元器件的支撑和电气连接。衬底的材料可以是硅、陶瓷或有机材料,具体选用哪种材料取决于应用的特定要求。

最常见分两种,一种是硅工艺的互连衬底,另一种是封装有机基板,具体来说:

(1)硅工艺的互连衬底

硅工艺的互连衬底是指使用硅材料制作的基板,用于电子产品的封装。硅是一种半导体材料,具有较高的热导率和电导率,因此在封装电子产品时常常使用硅基板。硅基板的生产工艺比较复杂,需要经过多个步骤,包括硅片的切割、表面处理、基板制备和定向处理等。 具有较高的热稳定性,可以在高温条件下使用。此外,硅基板的电气性能也很好,具有较低的电阻和较高的电容,因此在高频电路的应用中非常常用。但是,硅基板的生产成本较高,因为它们的生产工艺比较复杂,并且在生产过程中使用的材料也较昂贵。

(2)封装有机基板

封装有机基板(Organic Substrate)是一种通常用于芯片封装的基板材料。它的主要成分是有机材料,通常是基于聚酯、玻璃纤维或陶瓷材料的有机复合材料,具有较低的热导率和较高的电气绝缘性能,这使得它们在高频电路的应用中具有一定的优势。此外,封装有机基板的生产成本通常比硅基板低,因为它们的生产工艺更简单,而且在生产过程中可以使用较低成本的材料。

尽管封装有机基板具有一些优势,但它们也存在一些局限性。封装有机基板的温度稳定性较差,通常不能在高温条件下使用。此外,封装有机基板的电气性能也较差,具有较高的电阻和较低的电容。这使得它们在高频电路的应用中受到限制(要求更有效地传输和储存电荷)

在选择封装基板时,应考虑应用的特定要求,并综合考虑各种因素,如材料性能、生产成本、温度稳定性和电气性能等。

封装有机基板工艺相对于硅工艺的互连衬底工艺有材料及生产成本低的巨大优势同时可靠性高,因此备受青睐。

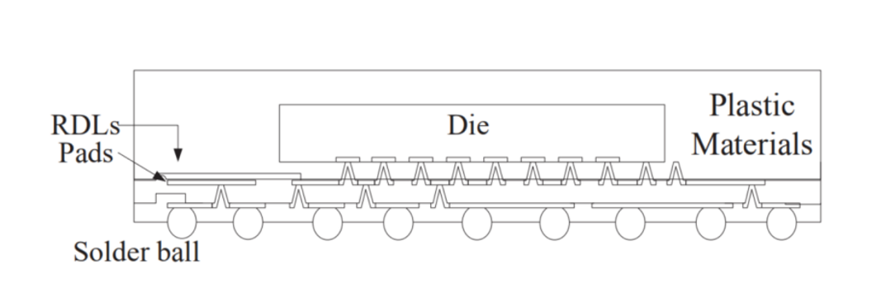

二、RDL Interposer 技术

RDL Interposer是一种常用的封装技术,常用于制造集成电路和其他电子元器件。该技术在硅衬底上通过等离子刻蚀等技术制作带有通孔(TSV)的硅基板,该硅基板可以为芯片提供互连基础。在硅基板的正面和背面制作重新分配层(RDL),可以为 TSV 和硅衬底上集成的芯片提供互连基础。RDL Interposer 技术可以提高信息传输的效率和稳定性,在制造集成电路和其他电子元器件方面具有较高的应用价值。

RDL(Redistribution Layer)是指再分配层,是一种用于电子产品封装的技术,由金属层和基板组成,主要用于将外部电路连接到芯片的内部电路。在基板上形成微小的金属引脚连接不同的电路。RDL Interposer封装技术可以将芯片与芯片之间的电路连接距离变得更小,使芯片封装的密度更高,使信号走线宽度和间距大幅度降低,从而提高单位面积的信号密度,提高电路的性能。

主要原理就是在晶片表面沉积金属层和介电层。它形成了一个再分配层,以携带相应的金属布线模式,并在芯片外的松散区域上重新排列芯片的IO端口。由于RDL形成的金属布线的线宽和间距较小,从而提供了更高的互连密度,同时可以通过缩短电路长度来提高信号质量,通过减少芯片面积来提高芯片集成能力。

传统封装工艺步骤主要在裸片切割分片后进行,先对晶圆(Wafer)进行切割分片(Dicing),然后再封装(Packaging)成各种形式。封装过程中大部分工艺过程都是对晶圆进行操作,即在晶圆上进行整体封装(Packaging),最后再进行切割分片。

三、硅中介层(Si Interposer)

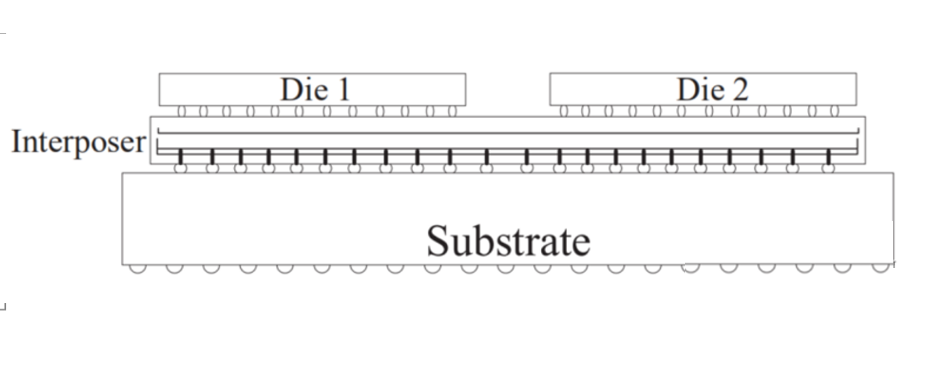

Interposer 是一种中介层,常用于分布式系统中,它可以帮助上层或下层的节点之间进行信息交换(比如连接两个芯片)。Interposer 通常可以使用微凸点(ubump)和 C4 凸点(C4 bump)与芯片、封装基板进行电性能互连,实现芯片与封装基板之间的信息交换。Interposer 可以用于提高芯片的性能和带宽,以及使芯片更加紧凑。

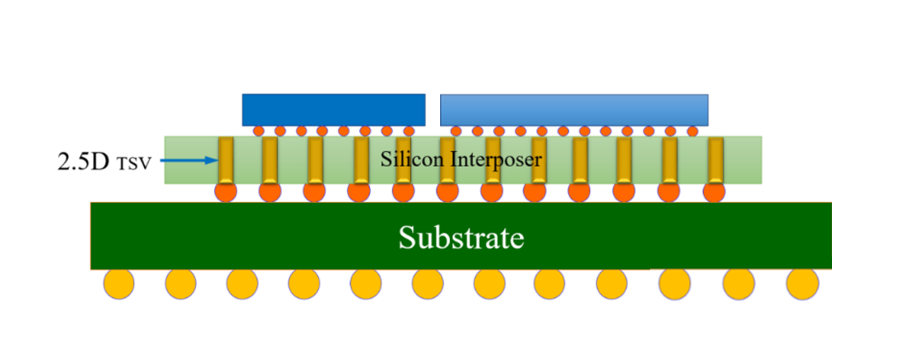

Si Interposer 技术是基于硅工艺的传统 2.5D 封装技术。 该技术在基板和裸片之间放置了额外的硅中介层,Die之间的互连和通信是通过在衬板和芯粒之间放置额外的硅层来实现的,裸片堆叠在中介层的顶部。由于凸块(Bump)允许的最小间距不足以支持多芯片互连和I/O需求,而硅中介层具有较高的细间距布线能力,堆叠芯片中再分布互连线。

Die之间的互连和通信是通过在衬板和芯粒之间放置额外的硅层来实现的,裸片堆叠在单个中介层的顶部。不再用线路板或者载板来作为承载芯片连接的载体,可以解决载板自身制造工艺极限所造成的封装工艺瓶颈问题。

四、嵌入式硅桥(EMIB)

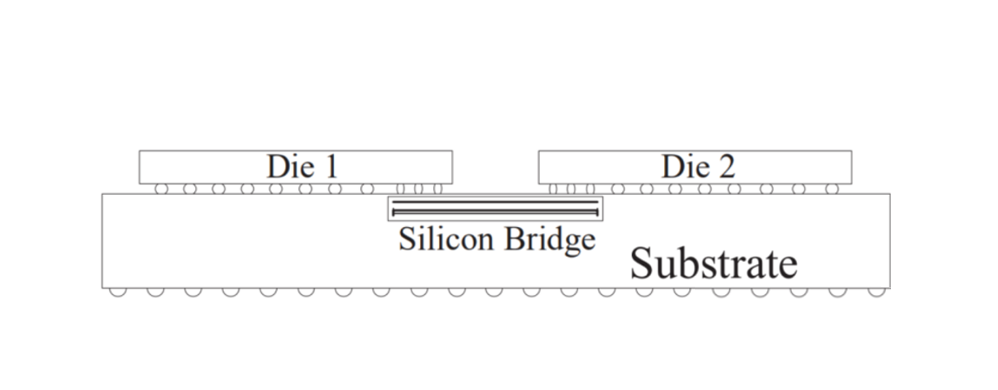

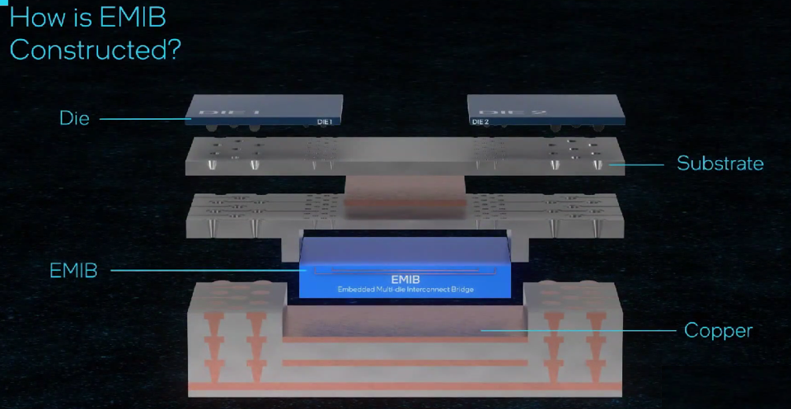

尝试将基底技术和硅中介层技术结合起来。它在基板上集成了小的薄层——硅桥,用于芯片间的互连,并将硅桥嵌入封装基板中,从而在性能和成本之间取得了良好的平衡。

EMIB是一个嵌入在底层封装基板中的小型硅芯片,并提供了模具之间的专用的超高密度互连。EMIB的物理尺寸并不限制可以集成的模具的数量。相比之下,替代实现使用位于封装衬底顶部的一大块Si Interposer,并超过了要集成的模具的整个长度。

五、硅通孔 TSV(Through Silicon Vias)

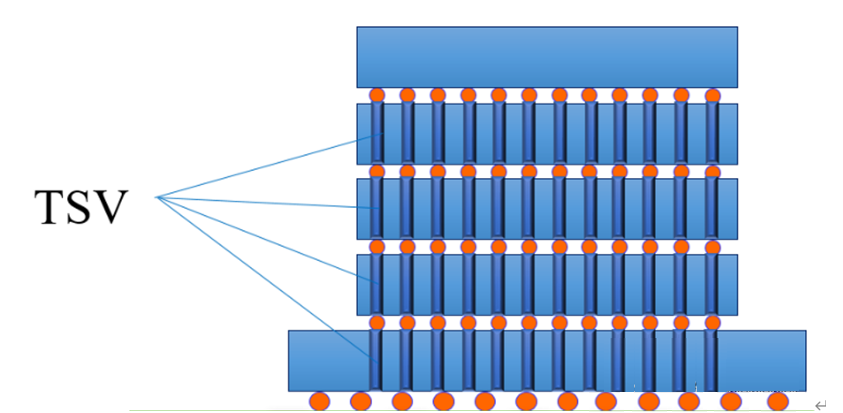

硅通孔:一种穿通硅圆晶片或芯片的垂直互连结构,可以完成连通上下层晶圆或芯片的功能,是晶圆多层堆叠中有效提高系统整合度与效能的关键工艺。它实现了贯穿整个芯片厚度的垂直电气连接,更开辟了芯片上下表面之间的最短通路。通过硅通孔技术将多层芯片互连导通,是一项高密度封装技术。例如存储器芯片和处理器芯片可以通过硅通孔(Through Silicon Vias, TSV)技术的方式连接在一起,不再受载板布线线宽、线距、密度的限制,从而可以实现数据带宽在接口上的提升。

芯片相互靠得很近,所以延迟会更少,此外互连长度的缩短,能减少相关寄生效应,使器件以更高的频率运行,从而转化为性能改进,并更大程度的降低成本。TSV主要优点如下:

2254

2254

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?