最近在看《计算机程序的解释和构造》,对其中的一个数字电路模拟器的设计例子比较感兴趣,主要是想体会其中的信号流动及驱动机制,现将其思路及细节整理一下, 其原理同现实世界数字电路的模块化设计思想类似,利用基本的与、或、非门电路元件作为基本积木块来构建更大的系统,这里面有若干要解决的问题:

1)与、或、非基本门电路的建模;

2)元件之间的信号驱动及流动机制的建模;

3)信号流动的并发性处理和时序控制。

不论是基本的门电路还是复杂的电路模块,它们都由两部分构成:内部电路逻辑计算过程以及电路的外部输入输出线路,内部逻辑计算过程根据输入线路上的信号值计算输出线路上的信号值,并经过一个模拟时延将计算得到的输出信号值设置到相应的输出线路上,承担着信号的变换过程;而电路的外部输入输出线路承担着信号值的传输过程。

非门的Scheme代码如下:

(define (inverter input output)

(define (invert-input)

(let ((new-value (logical-not(get-signal input))))

(after-delay inverter-delay

(lambda ()

(set-signal!output new-value)))))

(add-action! input invert-input)

'ok)

(define (and-gate a1 a2 output)

(define (and-action-procedure)

(let ((new-value

(logical-and (get-signala1) (get-signal a2))))

(after-delay and-gate-delay

(lambda ()

(set-signal!output new-value)))))

(add-action! a1and-action-procedure)

(add-action! a2and-action-procedure)

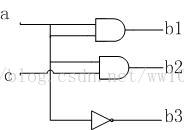

'ok)after-delay过程带有一个时延参数和一个信号赋值过程,实现经过给定的时延后完成某个输出线路上信号的赋值过程,定义了输入信号经过电路运算之后输出线路上的变化情况,相当于电路的传递函数,add-action!过程带有一个线路参数和一个过程参数,实现为指定的输入线路添加一个after-delay任务或者probe任务,一般来说,一条线路连接了n个输入端子就会拥有n个after-delay任务,如下图所示,a线路连接了5个输入端子就会构建5个激励任务,这5个激励任务会对连接在a线路上的所有的电路模块的输出端进行信号求值,从信号的传播角度考虑,以线路为对象进行信号幅值任务的配置是合理的,因为在现实过程中,当一个信号传输到某条线路上时,必然会对所有连接在此线路上的电路构成一个激励源,影响着所有连接在此线路上的电路的输出信号值,所以把线路a的信号对所有连接在此线路上的电路的影响过程添加到线路a这个对象当中去。

从上面的分析过程可以看到,对线路的操作是整个数字电路设计的核心,线路包含以下几个操作:1、线路的信号赋值;2、线路的信号取值;3、线路的激励任务添加,将这三个过程封装在线路对象的内部,并采用dispatch消息的方法对外提供线路的操作接口,代码如下:

(define(make-wire)

(let ((signal-value 0) (action-procedures'()))

(define (set-my-signal! new-value)

(if (not (= signal-value new-value))

(begin (set! signal-value new-value)

(call-each action-procedures))

'done))

(define (accept-action-procedure! proc)

(set! action-procedures (cons procaction-procedures))

(proc))

(define (dispatch m)

(cond ((eq? m 'get-signal) signal-value)

((eq? m 'set-signal!)set-my-signal!)

((eq? m 'add-action!) accept-action-procedure!)

(else (error "Unknownoperation -- WIRE" m))))

dispatch))于是,对线路操作的过程可以定义如下:

(define(get-signal wire)

(wire 'get-signal))

(define(set-signal! wire new-value)

((wire 'set-signal!) new-value))

(define(add-action! wire action-procedure)

((wire 'add-action!) action-procedure))观察make-wire过程可以看出,每一条新定义的线路的初始信号值为0,不拥有的任何激励过程,从其中定义的set-my-signal!过程可以看到,一旦线路a的信号值发生改变,在线路a中添加的所有的激励过程(action-procedures)会通过调用call-each过程全部执行一遍,call-each定义如下:

(define(call-each procedures)

(if (null? procedures)

'done

(begin

((car procedures))

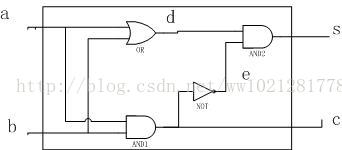

(call-each (cdr procedures)))))现在我们试着构建一个半加器来追踪上述代码的调用情况以及信号在线路上的变化情况,半加器的电路图如下:

半加器的定义代码如下:

(define(half-adder a b s c)

(let ((d (make-wire)) (e (make-wire)));;定义内部连线d和e

(or-gate a b d);;将线路a、b连接到或门的输入,d连接到或门的输出,

(and-gate a b c);;将线路a、b连接到与门的输入,c连接到与门的输出

(inverter c e);;将线路c连接到非门的输入,e连接到非门的输出

(and-gate d e s);;将线路d、e连接到与门的输入,s连接到与门的输出

'ok))定义门电路时延:

(define inverter-delay 2)

(define and-gate-delay 3)

(define or-gate-delay 5)创建半加器的两个输入两个输出连线:

(define a(make-wire))

(define b(make-wire))

(define s(make-wire))

(define c(make-wire))为两个输出端口添加信号探针,当此两个端口的信号发生改变时,可以打印出信号的状态信息:

(probe 's s)

(probe 'c c)将半加器的输入输出端口和上述创建的四条线路相关联:

(half-adder a b s c)此时的半加器处于初始状态,四个端口的信号值均为0.为端口1设置信号值1:

(set-signal! a 1)现在我们分析代码的调用情况以及信号的流动情况:

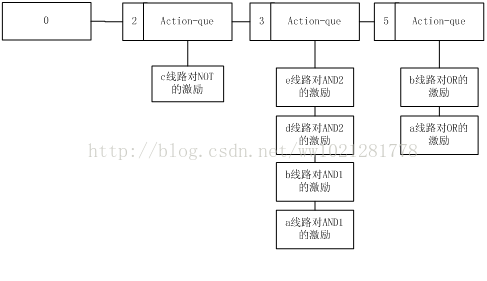

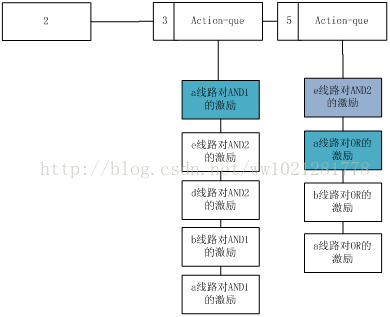

此时的半加器处于初始状态,四个端口的信号值均为0。当执行(half-adder a b s c)的时候,half-adder过程首先创建两根线路d和e,接着执行or-gate a b d),将线路 a、 b连接到或门OR的输入,d连接到或门OR的输出,同时为线路 a和线路 b分别添加一个对或门OR的after-delay激励过程,并且将这两个激励过程加入一个全局的过程容器the-agenda;接着执行(and-gate a b c);;将线路 a、 b连接到与门AND1的输入,c连接到与门AND1的输出,同时为线路 a和线路 b分别添加一个对与门AND1的after-delay激励过程, 并且将这两个激励过程加入the-agenda;接着执行(inverter c e),将线路c连接到非门NOT的输入,e连接到非门NOT的输出,同时为线路c添加一个对非门NOT的after-delay激励过程,并且将这个激励过程加入the-agenda;最后执行(and-gate d e s),将线路d、e连接到与门AND2的输入,s连接到与门AND2的输出,同时为线路d和线路e分别添加一个对与门AND2的after-delay激励过程,,并且将这两个激励过程加入the-agenda;至此线路 a(a)和线路 b(b)各拥有两个after-delay激励过程,线路d、e各有一个after-delay激励过程,线路c拥有一个after-delay过程和probe过程,s拥有一个probe过程,而 the-agenda中共有七个和after-delay过程相对应的set-signal激励过程。the-agenda的结构如下:

当调用(set-signal!a 1)的时候实际上调用的是a线路内部的set-my-signal!过程,该过程先调用set!过程将a线路上的信号值设置为1,然后调用call-each过程将a内部的action-procedures过程表中的激励过程(有两个过程)逐个执行一遍:a内部的action-procedures列表中的第一个过程将针对线路d的set-signal激励添加进the-agenda,由于OR的输出延迟为5,the-agenda的当前时间为0,5+0=5,所以将a对d的激励过程添加进时间标志为5的段;而第二个过程把针对线路c 的set-signal输出激励添加进the-agenda,由于AND1的输出延时为3,the-agenda的当前时间为0,3+0=3,所以将a对c的激励过程添加进时间标志为3的段内,the-agenda变成如下结构:

“propagate”过程的主要作用是将the-agenda内部的过程从左至右,从上至下执行一遍,并进行时序管理。其代码如下:

(define (propagate)

(if (empty-agenda? the-agenda)

'done

(let ((first-item (first-agenda-item the-agenda)))

(first-item)

(remove-first-agenda-item! the-agenda)

(propagate))))当执行到语句“(propagate)”时:

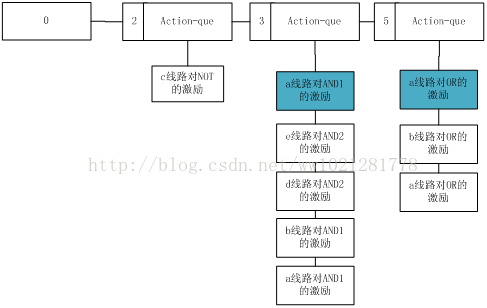

1、先执行时间标签为2下面的激励过程(将the-agenda的当前时间设置为2),该过程是c线路对NOT的激励,也就是根据c线路的信号状态设置NOT的输出线路e上的信号,由于c=0,e的信号要由0变为1,所以会将调用call-each过程将线路e内部的action-procedures过程表中的after-delay过程(只有一个)执行一次,将e对s的输出激励加入the-agenda,同时删除时间标志为2的时间段,如图:

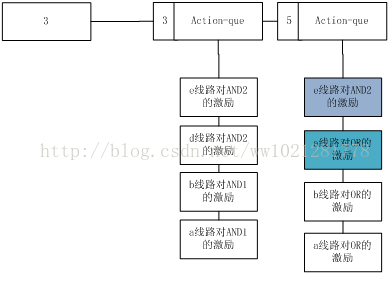

2、接着执行时间标志为3的段下面的激励过程,第一个被执行的为a线路对AND1的激励过程,也就是根据a=1,b=0设置c的信号值,但由于应当设置的值和初始的值都为1,所以不会执行c上的action-procedures过程表。将the-agenda的当前时间设置为3,并且删除刚才执行的激励过程,变为:

同理,执行e线路对AND2的输出激励,由于此时d=0,e=1,所以s=0,值未发生改变,删除该激励过程;接着执行d线路对AND2的激励,s=0未发生改变,删除该激励过程;执行b线路对AND1的激励过程,c=0未发生改变,删除该激励过程;接着执行a线路对AND1的激励过程,c=0未发生改变,删除该过程,删除时间标志位3的段,the-agenda的结构如下:

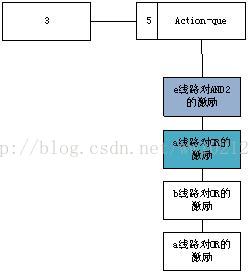

3、接着执行e线路对AND2的输出激励过程,s=0未发生改变,将the-agenda的当前时间修改为5,删除该过程;接着执行a线路对OR的输出激励过程,将d的信号设置为1,由于d上的信号数值发生了改变,将执行d的action-procedures过程表,将d对AND2的输出激励添加进the-agenda,由于the-agenda的当前时间加上AND2的延迟为8,所以需要新建一个时间标志为8的段,并将其添加至the-agenda尾部,同时删除当前a线路对OR的输出激励过程,于是the-agenda的结构如下:

接着执行b线路对OR的输出激励过程,c未变,删除之;接着执行a线路对OR的激励过程,d未变,删除之;时间标志为5的段已空,删除之。于是the-agenda的结构如下:

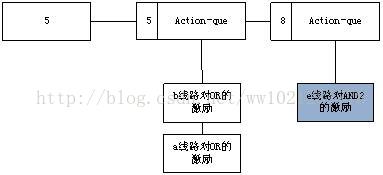

4、接着执行时间标志为8的段下的e线路对AND2的输出激励过程,将the-agenda当前时间设置为8,由于d=1,e=1,所以s=1,s的值发生了改变,会调用s的action-procedures过程表,表中只有一个输出当前线路状态的探针过程,所以会打印出当前s线路的当前状态,接着删除该激励过程,此时时间标志为8的段为空,也被删除,最终the-agenda只剩下一个当前时间标志段:

此时模拟器完成工作,如果继续(set-signal! input-2 1),那么又会在the-agenda中添加一系列的激励过程,执行(propagate)后又会变为只剩下时间标志的空表。

这个程序的the-agenda结构很有意思,从水平方向看,带时间标志的段的插入与删除是以队列方式组织的,从垂直方向看,激励过程的删除与插入是以栈的方式组织的,总的来说,是一种“一对列多堆栈”的结构,其在多对象并发的时序管理方面的行为值得揣摩。

这个程序最难看懂的地方在于如何实现对线路状态进行时间排序输出,我看了很久才完全看懂...我相信这应该是一个威力强大的技术思路,到时候有什么想法再记录。

294

294

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?