一、ADC基础

ADC(Analog to Digital Conver),通常是指一个将模拟信号转变为数字信号(二进制表示的离散信号)的转换器。

1. 间接ADC 先将输入模拟电压转换成时间或频率,再把中间量转换成数字量

双积分型 ADC,先对输入采样电压和基准电压进行两次积分,获得与采样电压平均值成正比的时间间隔,同时用计数器对标准时钟脉冲计数。抗干扰能力强,稳定性好,但转换速度低。

2. 直接ADC

①并联比较型 ADC,采用各量级同时并行比较,各位输出码也是同时并行产生,转换速度快。缺点是成本高、功耗大。

②逐次逼近型 ADC,逐个产生系列比较电压,逐次与输入电压分别比较,以逐渐逼近的方式进行模数转换,属于中速 ADC 器件。

3. 位数、分辨率、精度

ADC位数,每个通道转换结果的位数。

n位的ADC的分辨率为2的n次方。

假如量程是5V,用12位ADC能采集得到的最小电压值为5/(2^12)=1.2mv,此为该ADC的精度。

二、ADC128S022

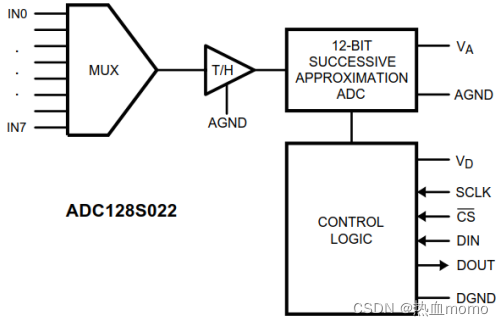

1. 结构

AC620 使用逐次逼近型的低功耗芯片 ADC128S022,具有8通道及12位分辨率。12位ADC,转换结果需要通过12个SCLK将数据采集出来。

12 位分辨率,该ADC 1bit 代表的电压值即为 VA/4096。手册中同时指出,模拟输入电压低于 VA/8192 时,输出 0000_0000_0000b,当输出数 0000_0000_0000b 变为 0000_0000_0001b 时,实际输入电压变化为 VA/8192 而不是 VA/4096。当输入电压大于等于 VA-1.5* VA/4096,输出数据即为 1111_1111_1111b。

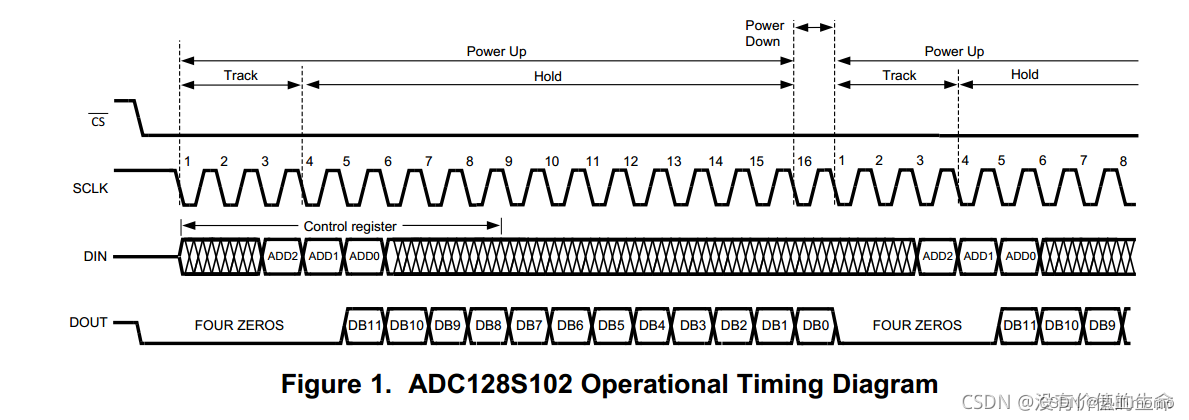

2. 接口时序

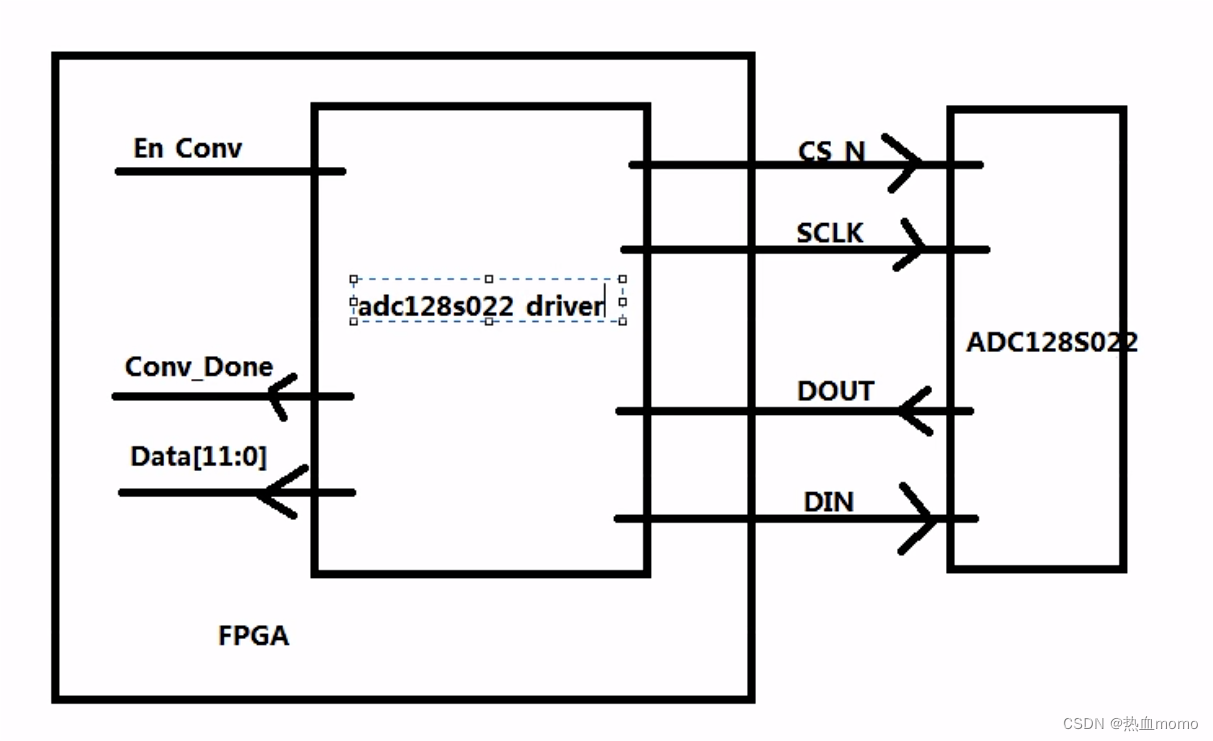

ADC128S022 通过 SPI 接口与控制器进行通信,FPGA 按SPI 时序实现对ADC的控制。

DIN:ADC通道信号,FPGA输出,ADC在SCLK上升沿采样输入,在下降沿改变数据。

DOUT:ADC采集到的模拟串行信号,输入FPGA转换为并行数字信号Data,FPGA在上升沿采样,在下降沿改变数据。

一帧包含 16 个SCLK上升沿,前三个处于采样模式track,后13个为保持模式hold。下降沿 1~4 为前导零,5~16 为输出转换结果。(SCLK第一个下降沿自动进入采样模式)

三、线性序列机设计接口时序

线性序列机:计数器每个计数值对应一个时间,按顺序执行,SCLK每个下降沿、上升沿应

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?