计算机组成原理学习开篇

做了几年Java Coder自认为Java相关基础还够用,但往往对一些更深底层实现只能点到为止,不能很好的融汇贯通。搜索各种资料,想一层一层的剥开,却也很难解释透彻。随着技术知识的了解越广,对技术的敬畏也越深,但值得庆幸的是对技术刨根揭底的心没死透。从最底层的计算机组成原理开始学习,还大学的4年游戏所欠的(出来混迟早都得还,以此告诫还在上学的同学们)…..

本系列文章主要围绕硬件的学习记录笔记,通过博客来跟大家一起学习探讨,如果错误之处请求大家指正,以免误导了他人

计算机发展史

| 发展阶段 | 时间 | 硬件技术 | 速度(次/秒) |

|---|---|---|---|

| 第一阶段 | 1946-1957 | 电子管 | 40000 |

| 第二阶段 | 1958-1964 | 晶体管 | 200000 |

| 第三阶段 | 1965-1971 | 中小规模集成电路 | 1000000 |

| 第四阶段 | 1972-1977 | 大规模集成电路 | 10000000 |

| 第五阶段 | 1978-现在 | 超大规模集成电路 | 100000000 |

百度百科查的各个阶段的物理元件,至于这些元件为什么有这些物理特性,就不深挖了,毕竟我们不做硬件工程师

电子管, 是被封闭在玻璃容器(一般为玻璃管)中的阴极电子发射部分、控制栅极、加速栅极、阳极(屏极)引线被焊在管基上。利用电场对真空中的控制栅极注入电子调制信号,并在阳极获得对信号放大或反馈振荡后的不同参数信号数据。目前高端音响有用电子管的。

晶体管,是一种固体半导体器件,具有检波、整流、放大、开关、稳压、信号调制等多种功能

集成电路,是一种微型电子器件或部件。采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构

计算机组成结构

计算机由硬件和软件两大部分组成。本文主要从硬件结构方面介绍。自从1945年,冯·诺依曼(von Neumann)提出存储程序的概念,发展到至今计算机结构都是以此为基础构建的。现代计算机主要由处理器、存储器、IO模块以及连接这些部件总线。

冯·诺依曼理论

- 计算机由运算器、存储器、控制器、输入设备和输出设备五大部件组成

- 指令和数据以同等方式存放在存储器中,按地址访问

- 指令和数据都用二进制表示

- 指令由操作码和地址码组成,操作码用来表示操作的性质,地址码用来表示操作数在存储器中的位置

- 指令在存储器内按顺序存放

- 机器以运算器为中心,输入输出设备与存储器间的数据传送通过运算器完成

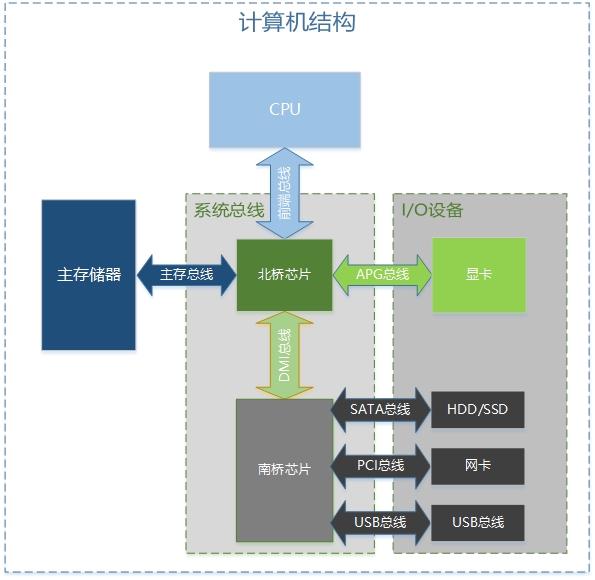

现代计算机结构图

CPU

CPU是由一块超大规模的集成电路组成,是计算机的运算核心和控制核心。主要包括运算器(ALU)、控制器(CU)、寄存器和高速缓冲等部件。

主存储器

主存储器简称主存,是一个临时存储设备,存放指令和数据,CPU能直接随机存取。

总线

总线(Bus)是计算机各种功能部件之间传送信息的公共通信干线,它是由导线组成的传输线束, 按照计算机所传输的信息种类,计算机的总线可以划分为数据总线、地址总线和控制总线,分别用来传输数据、数据地址和控制信号。

I/O设备

输入/输出(Input /Output ,简称I/O),指的是一切操作、程序或设备与计算机之间发生的数据传输过程。I/O设备是计算机系统与外部联系的通道。

计算机硬件主要性能指标

- 机器字长是指CPU一次能处理的数据位数,通常与CPU的寄存器位数有关。字长越长,数字范围越大,精度也越高;同时也会影响机器的运算速度,如运算位数多的数据,需要经过多次运算才能完成。

- 存储容量是指主存存放的二进制代码的总位数。主存容量越大,系统功能就越强大,能处理的数据量就越庞大。

- 运算速度是指单位时间内能执行的指令数量。一般受机器主频,取指周期,总线带宽,CPU流水线设计等因素影响。

后面再围绕这总线、存储器、I/O设备、CPU依次展开详细介绍….

参考文献

1. 《计算机组成原理》

2. 《深入理解计算机系统》

3. 《计算机组成与体系结构-性能设计》

1662

1662

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?