总线简介

总线(bus)是计算机各个功能部件之间传送信息的公共传输线,是由导线组成的传输线束。通过总线使计算机各个功能部件之间完成地址、数据和控制信号等信息交换。由许多传输线或通路组成,每条线可以一位一位的传输二进制代码。

传输方式

串行传输,数据在单条1位宽的传输线上,一位一位的顺序传送。如1字节的数据需要通过传输线8次由低位到高位按顺序传送。适用于远距离传输。

并行传输,数据在多条并行1位宽的传输线上,同时由源传送到目的地。如1字节的数据,需要通过8条并行线同时由源传送到目的地(每位数据同时发送同时呗接收)。适用于高速近距离传输。

总线优势

- 简化了硬件的设计。便于采用模块化结构设计方法,面向总线的微型计算机设计只要按照这些规定制作cpu插件、存储器插件以及I/O插件等,将它们连入总线就可工作,而不必考虑总线的详细操作。

- 简化了系统结构。整个系统结构清晰。连线少,底板连线可以印制化。

- 系统扩充性好。一是规模扩充,规模扩充仅仅需要多插一些同类型的插件。二是功能扩充,功能扩充仅仅需要按照总线标准设计新插件,插件插入机器的位置往往没有严格的限制。

- 系统更新性能好。因为cpu、存储器、I/O接口等都是按总线规约挂到总线上的,因而只要总线设计恰当,可以随时随着处理器的芯片以及其他有关芯片的进展设计新的插件,新的插件插到底板上对系统进行更新,其他插件和底板连线一般不需要改。

- 便于故障诊断和维修。用主板测试卡可以很方便找到出现故障的部位,以及总线类型。

总线分类

总线分类,从不同的角度有不同的分类方法。按信号传输方式可以分为并行传输总线和串行传输总线。按连接的部件可以分为片内总线、系统总线、通信总线。

片内总线

片内总线是指连接芯片内部的总线,如在CPU芯片内部运算器、控制器、寄存器之间连接的传输线。

系统总线

系统总线是指连接CPU、主存、I/O设备等各大部件的传输线。系统总线按传输的信息不同分为数据总线、地址总线、控制总线。

- 数据总线

数据总线用来传输各个功能部件之间的数据信息,可以双向传输。并行传输方式,总线宽度一般与机器字长相等或成倍数。 - 地址总线

地址总线用来指出数据总线上的源数据或目的数据在主存中的地址或I/O设备的地址。例如,从主存中读出一个数据,则CPU要将此数据所在的存储单元地址送到地址线上;往主存写入一个数据,则CPU除了将数据送到数据线,还得将需要存入的存储单元地址送到地址线。因此,地址线是单向的,都是由CPU传出。 - 控制总线

控制总线是用来传输各种控制信息或接收反馈信息的传输线,双向传输。如有中断请求、总线请求、主存读写命令等等控制信号。

总线性能指标

影响总线性能的主要因素有:总线宽度、总线时钟萍绿

- 总线宽度

总线宽度指的是总线中数据总线的数量,用bit(位)表示,总线宽度有8位、16位、32位和64位之分。显然,总线的数据传输量与总线宽度成正比。 - 总线时钟

总线时钟频率是总线中各种信号的定时标准。一般来说,总线时钟频率越高,其单位时间内数据传输量越大。 - 总线带宽

总线带宽是总线的数据传输速率,即单位时间内总线传输数据的位数,通常用每秒传输的字节数(MBps)表示。例如,总线工作的时钟频率位200MHz,总线宽度位32位,则总线带宽为200×(32/8)= 800MBps。 - 总线负载

总线的负载能力即驱动能力,通常表示可连接扩增最大电路板数。

总线标准

总线标准,计算机各个模块之间互连的标准协议。各个模块根据标准完成自身的接口功能,无需关注对方与总线的连接要求。主要为解决I/O设备的多样化发展,以及不断被推出的各种外设,提供统一的标准。这也是最早期的硬件面向接口设计,使计算机各个功能部件实现解耦,也为计算机各个部件,各个厂商的发展提供了良好的环境。

| 总线标准 | 数据线 | 总线时钟 | 带宽 |

|---|---|---|---|

| ISA | 16 | 8MHz(独立) | 16MBps |

| EISA | 32 | 8MHz(独立) | 33MBps |

| VESA | 32 | 32MHz(CPU) | 133MBps |

| PCI | 32/64 | 33/66MHz(独立) | 132/528MBps |

| AGP | 32 | 66.7/133MHz(独立) | 266MBps(AGP 1x) 533MBps(AGP 2x) 1GBps(AGP 4x) 2.1GBps(AGP 8x) |

| RS-232 | 串行通信 | 数据终端设备和数据通信设备之间的接口 | |

| USB | 串行接口 | 1.5~12Mbps(USB1.0) 480Mbps(USB2.0) | |

| PCI Express | 8,点对点串行连接的设备连接方式 | 2.5 GHz | 支持双向多通道,最大带宽可达256Gbps |

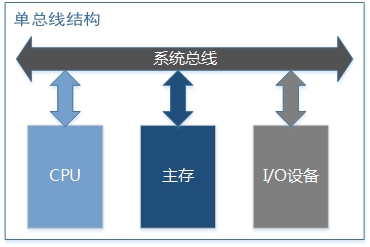

总线结构

总线结构是总线将CPU、主存、I/O设备通过某种方式连接在一起的结构。通常可以分为单总线结构和多层多总线结构。

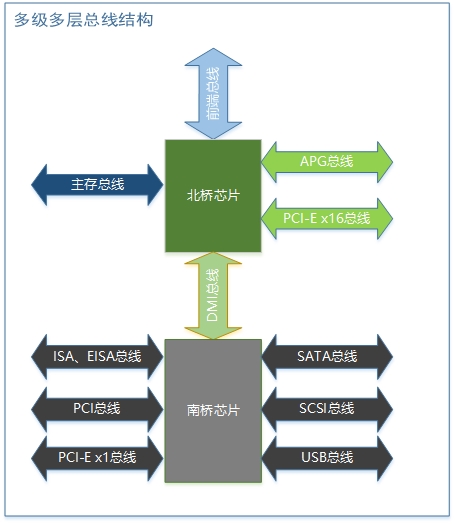

由于同一时间只能一个功能部件占用总线,很明显单总线结构会使高速的CPU被低速的I/O设备拖累,从而影响整体系统工作效率。随着技术的进步演化成复杂的多级多总线结构,如下图所示。

北桥负责CPU和高速接口之间数据通信,以及桥接CPU和南桥。主要集成内存控制器、PCI-E控制器等。

南桥负责I/O总线之间的通信,主要管理中低速外部设备,如PCI总线、USB、LAN、ATA、SATA、音频控制器、键盘控制器、实时时钟控制器、高级电源管理等。还集成了中断控制器、DMA控制器。

随着工艺的进步CPU的集成度越来越高,现代计算机把主存控制器、PCI-E控制器等集成到CPU中;连接北桥的FSB总线,也逐步被QPI总线也逐步替换。

参考文献

1. 《计算机组成原理》

2. 《深入理解计算机系统》

3. 《计算机组成与体系结构-性能设计》

4. http://www.icourses.cn/coursestatic/course_6011.html

2201

2201

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?