Altera的嵌入式软处理器系列使您能够充分利用FPGA内在的并行优势,实现高级系统性能。多个处理器可以同时执行代码,而硬件加速器也能够同时卸载大计算量算法。不需要重新设计电路板或者手动优化汇编程序,便能够在产品生命周期的任何阶段更新嵌入式系统的性能。

以下介绍更新系统性能的几种方式:软核处理器;定制指令;硬件加速器;可配置高速缓冲和紧耦合存储器;多处理器系统;宽带系统互联。

方式1:软核处理器

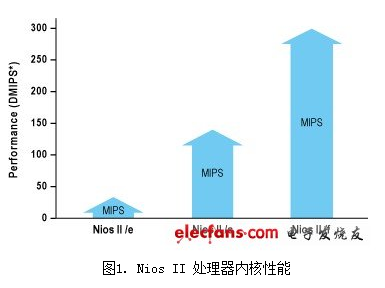

如果您使用Altera的Nios® II 处理器,可以从三种代码兼容的软核处理器中进行选择(参见图1):一种针对最佳系统性能进行了优化;一种针对最少逻辑占用进行了优化;还有一种是二者之间达到平衡。

采用乘法器、用户设定的高速缓存、定制指令、硬件调试逻辑等特性来配置这些内核,能满足用户的特殊性能需求。

Altera嵌入式系列产品的其他软核处理器包括:

MP32处理器:业界第一款100%兼容MIPS®的软核处理器。

ARM® Cortex-M1处理器:三级32位ARM Cortex处理器。

Freescale V1 ColdFire处理器:具有全综合内核以及长度可调RISC 16位、32位和48位指令。

Intel® Atom® E6x5C处理器:在多芯片封装中组合了Intel Atom处理器E6xx系列以及Altera® FPGA。

方式2:定制指令

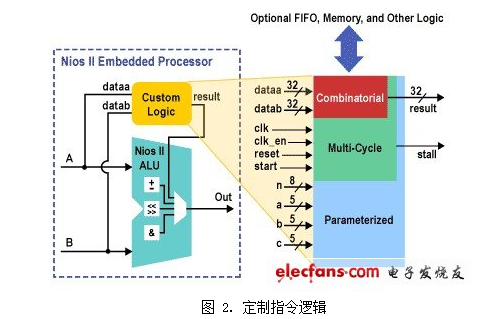

在Nios II 处理器指令集中加入定制指令来加速对时间要求较高的软件算法。您可以在每一处理器内核中加入256条定制指令,从而减少了数值计算、位操作以及其他复杂处理算法所需的时钟周期数(参见图2)。

定制指令支持Nios II设计人员将部分软件代码在硬件功能中实现,从而提升了系统性能。但是,定制指令是在处理器边界内实现的,扩展了CPU指令集以加速对时间要求较高的软件。

利用Nios II处理器的可配置特性,设计人员能够将定制逻辑直接集成到算术逻辑单元(ALU)中。通过定制指令,开发人员可以优化实际应用中的软件内循环,这些应用包括数字信号处理(DSP)、数据包帧头处理,以及计算量较大的应用,将复杂的运算序列缩减为在硬件中实现的一条指令。

使用定制指令,设计人员能够优化系统性能,其实现方式是传统商用处理器所不具备的。Altera的SOPC Builder提供图形用户界面,开发人员可以利用它很方便的导入自己的硬件设计文件,开发定制指令,自动集成到Nios II处理器中。

Nios II处理器定制指令提供:256条用户定义的指令、固定和可变周期运算、用户逻辑导入向导、C和汇编语言软件宏。

方式3:硬件加速器

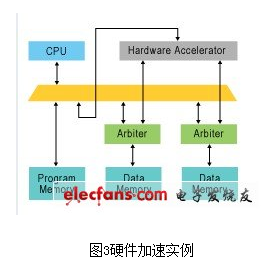

将C语言子程序转换为硬件加速器,自动加速软件实现,不用提高时钟频率和功耗便能够提升性能。在Nios II 处理器中,使用Nios II C语言至硬件(C2H)加速编译器,简单地“右键单击加速”性能关键的功能,从而不用手动生成Verilog或者VHDL加速器,节省了时间和投入(参见图3)。

硬件加速器是由Nios II C语言至硬件加速(C2H)编译器自动生成的逻辑模块,也可以是手动设计用于从系统处理器中卸载某些任务的逻辑模块。很多数学运算在硬件中实现时,要比软件实现更快,效率更高。SOPC Builder和AvalonTM交换架构支持使用硬件加速器来提升Nios II处理器软件的性能。与其他方法相比,硬件加速器能够:使用主存储器和其他系统资源,这些资源具有全流水线和存储器延时匹配主机端口,支持非常高的存储器带宽;由CPU通过从机端口进行控制;具有软件打包器功能,由CPU进行控制,在工具链中替代了最初的C代码。

图3显示了一个典型的硬件加速器,它含有两个连接至Avalon交换架构的的主机端口(读和写)。加速器使用直接存储器访问(DMA)组件来执行总线读和写操作,它提供控制端口以便处理器进行控制。最后,在中心位置,加速器逻辑是计算指定算法的引擎。

如果您使用Nios II C2H编译器,会自动产生所有这些组件,并集成到您的系统中。

硬件加速器为Altera FPGA增加了强大的功能,它作为复杂多周期协处理器来实现,可以流水线访问系统中的所有存储器和外设。它们可以使用FPGA资源(例如,片内存储器和硬核宏乘法器)来实现本地存储器缓冲以及乘法累加(MAC)电路。它们能够根据需要尽可能多的使用主机端口,启动读写操作,访问系统中的所有I/O引脚。很多Nios II开发人员发现,硬件加速器是提升软件代码性能最好的方法,能够充分发挥Altera® FPGA高性能体系结构的优势。

方式4:可配置高速缓冲和紧耦合存储器

调整处理器指令或者数据缓冲的大小,以满足您应用的性能要求。为了在Nios II 处理器中能够快速访问经常使用的例程,加入了4个紧耦合存储器,避免了缓存丢失的代价,实现了类似缓存的访问功能。

方式5:多处理器系统

使用多处理器来调整系统性能,或者将软件划分成更简单、更小的任务,更易于编写、调试和维护。Nios II 嵌入式设计包(EDS)以及来自业界一流嵌入式软件供应商的工具支持多处理器应用程序的开发和调试。Nios II 处理器结合Stratix® 系列FPGA等高密度器件和HardCopy® ASIC,是建立高性能多处理器系统的理想平台(参见图 4)。

方式6:宽带系统互联

在之后的Quartus® II 设计软件的版本中可获得Altera的Qsys 系统综合工具,利用FPGA的内在并行能力,帮助您生成大吞吐量系统。系统互联架构是全交换的,主机和从机之间的专用互联支持多路同时操作,而没有传统总线体系结构的仲裁瓶颈。利用智能直接存储器访问(DMA)通道来减轻您的处理器负荷。

Quartus® II 设计软件充分发挥了FPGA、CPLD和HardCopy®ASIC的效率和性能,提供多种设计特性,加速设计过程:设计输入、脚本支持、渐进式编译:初始设置、Qsys 系统集成工具、SOPC Builder、MegaWizard® 插件管理器、I/O引脚分配分析、Quartus II 集成综合、Rapid Recompile、第三方设计输入和综合、基本编译流程。

378

378

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?