一、硬件连接

1) 通过

USB

数据线,将逻辑分析仪连接至

PC

的

USB

端口,并确认硬件指示灯被点亮。

2) 打开

DSView

软件(

windows

系统首次使用时系统需要搜索驱动程序,请耐心等待),确认硬件指示灯变为

绿色

,同时

DSView

正确识别设备,并在设备列表框显示正确的设备名称。

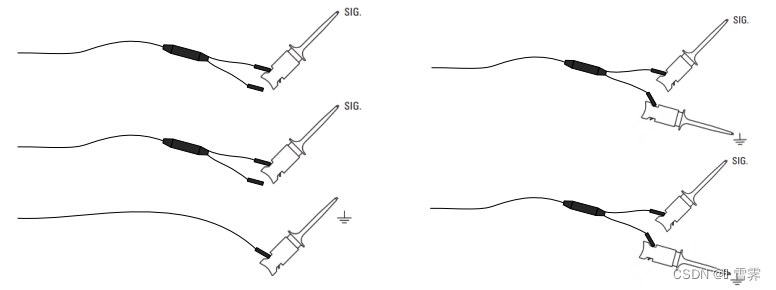

3) 连接排线至逻辑分析仪的采样端口,下图

显示了排线和通道的对应关系。对于增强版设备,每个通道为屏蔽线,末端分为信号和地两个端口;对于基础版设备,每 4

个通道配一个地线(黑色),彩色线顺序对应

0-15

这

16

个通道。 除此之外,排线还有 CK

,

TI

和

TO

信号,一般情况都不需要连接。其中

CK

通道为状态采样的时钟输入,可以把外部时钟作为采样时钟,TI

为外部触发信号的输入,TO

为触发信号的输出,会在采样过程中触发条件满足时输出脉冲。

4) 根据测量需求,连接通道至被测信号。对于低频信号(

<5MHz

),可以仅连接被测信号和一个公共地信号

,对于高频信号,建议每个通道单独接地,以获得最佳的信号完整性

。

二、软件设置

(一)软件安装与介绍

DSView 是一款多功能的信号捕获与分析软件,主要功能包括数字逻辑信号捕获与测量,数字协议分析与调试,模拟信号实时显示与测量,信号频谱分析等。

下载地址:

中文站点:

http://www.dreamsourcelab.cn/download/

国际站点:

http://www.dreamsourcelab.com/download/

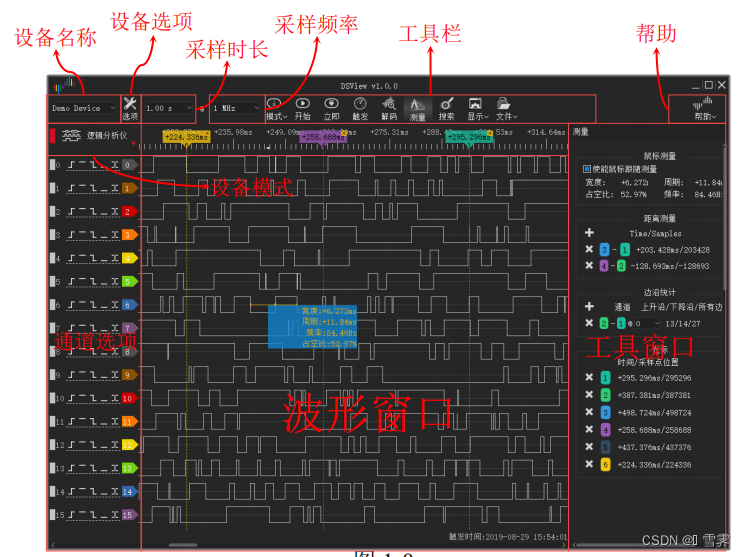

打开后界面如下:

(二)采样设置

(1)采样频率: 通常情况下,采样频率需要设置为被测信号最高频率的 4x-10x 倍。例如采样 115200 波特率的串口信号,采样率通常设置为 1MHz,采样 50MHz 的 SPI 信号,采样率可以设置为 400MHz。当然,采样率越高,获取的采样结果的分辨率越高,也越接近真实的信号。

(2)触发设置: 设置触发条件后,如果被测信号的波形不满足设定条件,采样过程会一直等待,直到满足设定条件后,才可完成当前采样。触发可以帮助我们捕获想要观察的特定时刻的信号,是逻辑分析仪最重要的特性之一。DSView 支持两种触发模式:简单触发和高级触发。

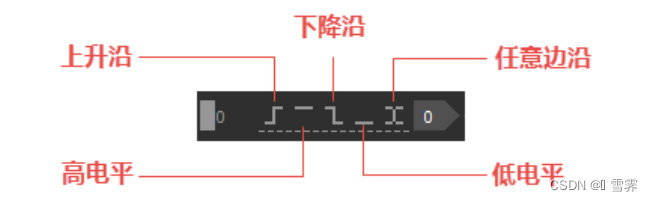

简单触发:

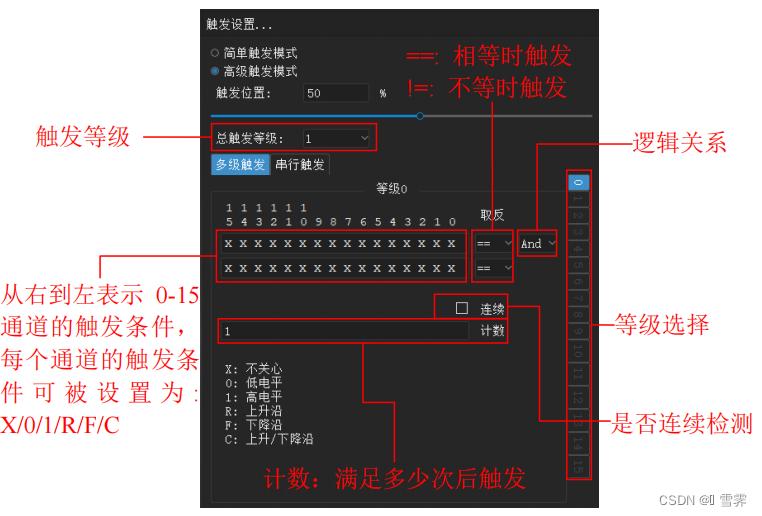

高级触发:

(3)采集模式:单次采集:在这个模式下,采集操作只会被执行一次。当采样时长达到时,采集会自动停止。 重复采集:在这个模式下,采集操作会被自动重复执行,直到按下停止按钮。结合触发条件的设置,这个模式可以帮助我们持续观察特定事件下的波形,而不用任何人工的干预。例如每次重启,或者每次按键等等。另外,此模式支持每次采样间隔时间的定义(从 1s 到 10s)。

(4)协议解码:单击解码按钮即可调出协议解码窗口,协议解码窗口主要分为两个部分,协 议选择和设置以及解码结果列表显示区域。

注: 帮助栏有详细使用手册

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?