上拉电阻、下拉电阻的讲解在CSDN上也有很多了,对运放和二三极管的阻值选择会写的比较详细,但是具体应用中大多数使用为主控芯片的GPIO引脚进行上拉和下拉,对此上拉、下拉阻值的选择却说不明道不清。

上拉电阻通常可以选择1k到10k数值不等,常用4.7K,你问老硬件工程师为什么是这个值?

答:经验值(哪个怪经验值多,我也要刷)

进入正题,一下会从两部分进行讲解,1为普通MCU主控的GPIO上拉电阻,2为I2C信号的上拉电阻。

上拉电阻:

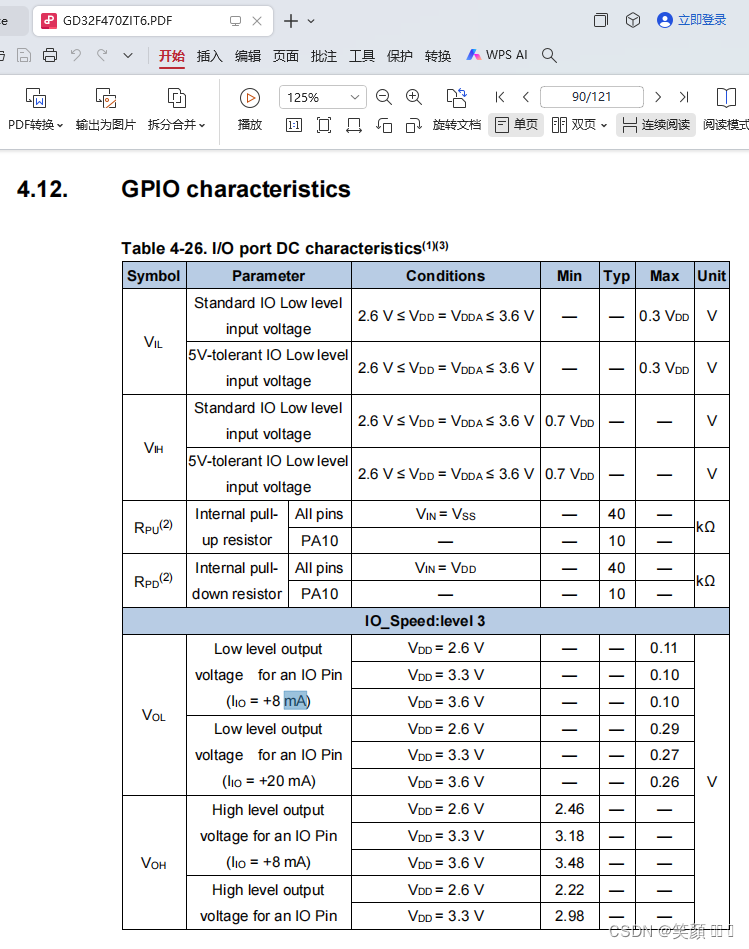

1、那么如下图MCU型号为GD32F470ZIT6(随便找的一个用过的小型处理器芯片做例子)

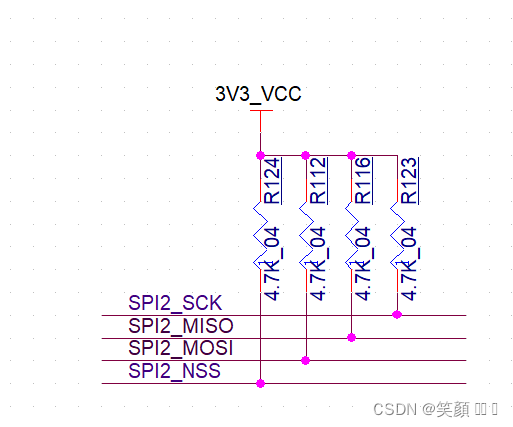

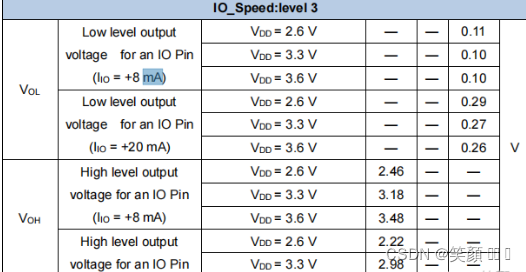

对于使用这颗芯片,GPIO脚上拉电阻值如何选择?看这部分写明Iio=±8和±20mA,因为我这边正常3.3V供电,所以IO也是3.3V的最大值计算得到3.3V÷8mA=412.5Ω,3.3V÷20mA=165Ω,所以其实只要大于计算得出的这两个值理论上所以也没问题,那为什么选择4.7K上拉?因为IO本身不进行上拉也可以输出,上拉的目的:

一是确保上下电时IO的稳定状态为高;

二是进一步提供输出能力足够(因为负载情况未知,可以参考http://t.csdnimg.cn/CudUb计算负载电流);

三是某些主芯片的IO会处于开漏状态,例如FPGA(就是不上拉就没输出,具体去搜索开漏是什么含义);

为保证IO的正常工作一般选择3.3V÷4.7kΩ=0.7mA的驱动电流,与其说是选上拉电阻,你也可以理解为选驱动电流大小。

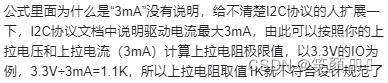

2、I2C上拉电阻如何选择参考以及扩展如下:

看到这里,对上拉电阻为什么选择4.7KΩ还是有点懵?

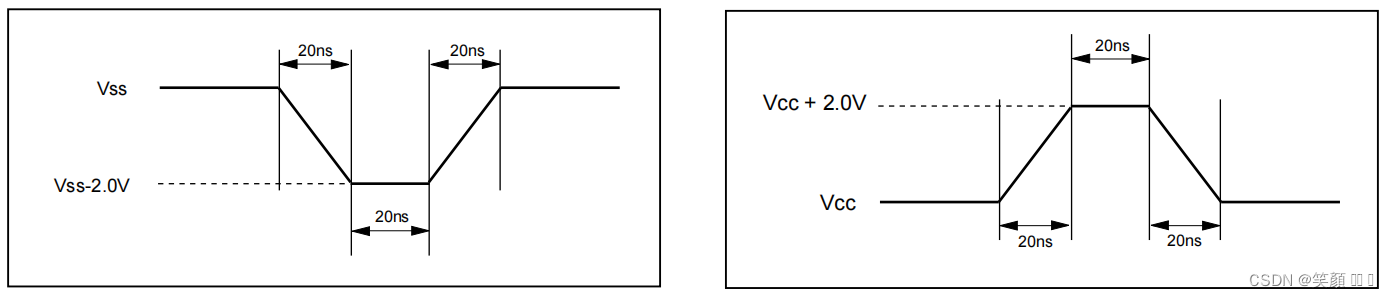

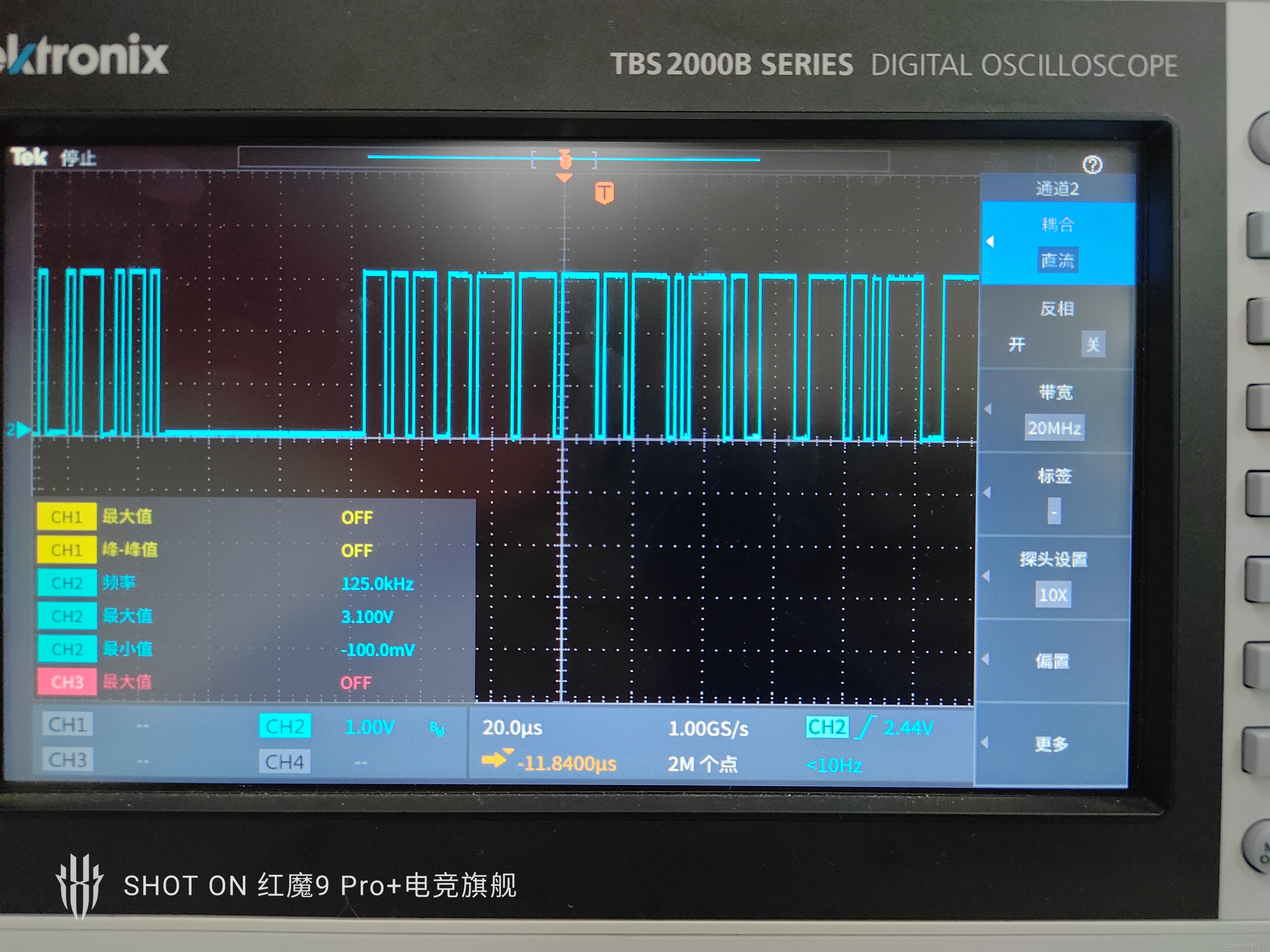

看看这个图,这个值为4.7KΩ会对图中上升和下降的曲线有一定影响,修改这个值越接近1K曲线越陡峭,越接近10K曲线斜角越大,下图示波器波形上升沿时间和下降沿时间是多少不重要,看着很方就好。

下图提到的公式为下方链接中的计算公式。

下拉电阻:

使用下拉电阻范围在1k~100k,阻值范围比上拉电阻还广但使用比上拉情景要少,讲下拉电阻下次一定。

767

767

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?