以上内容均为博主学习总结,如有侵权请联系我删帖。

目录

1.上拉电阻选择

由于IIC的接口电阻普遍是开漏输出,因此需要添加上拉电阻,电阻的值确定也是有一定的规则

1K<RP<10K

RP 不宜过小,一般不低于1KΩ

一般 IO 端口的驱动能力在 2mA~4mA 量级。如果 RP阻值过小,VDD 灌入端口的电流将较大,这导致端口输出的低电平值增大(I2C 协议规定,端口输出低电平的最高允许值为 0.4V);如果灌入端口的电流过大,还可能损坏端口。故通常上拉电阻应选取不低于 1KΩ的电阻(当 VDD=3V 时,灌入电流不超过 3mA)。

RP 不宜过大,一般不高于 10KΩ

由于端口输出高电平是通过 RP 实现的,线上电平从低到高变化时,电源通过 RP 对线上负载电容 CL 充电,这需要一定的时间,即上升时间。端口信号的上升时间可近似用充电时间常数 RPCL 乘积表示。

信号线负载电容(对地)由多方面组成,包括器件引脚、PCB 信号线、连接器等。如果信号线上挂有多个器件,负载电容也会增大。比如总线规定,对于的 400kbps 速率应用,信号上升时间应小于 300ns;假设线上 CL 为 20PF,可计算出对应的 RP 值为 15KΩ。

如果 RC 充电时间常数过大,将使得信号上升沿变化缓慢,达不到数据传输的要求。因此一般应用中选取的都是几 KΩ 量级的上拉电阻,比如都选取 4K7 的电阻。

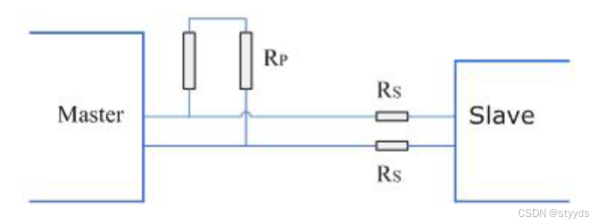

2.上拉电阻摆放位置

上拉电阻应安置在 OD 输出端附近。当 I2C 总线上主从器件(Master & Slave)两端均为 OD 输出时,电阻放置在信号路径的中间位置。当主设备端是软件模拟时序,而从设备是 OD 输出时,应将电阻安置在靠近从设备的位置。

I2C 协议还定义了串联在 SDA、SCL 线上电阻 Rs。该电阻的作用是,有效抑制总线上的干扰脉冲进入从设备,提高可靠性。这个电阻的选择一般在 100~200ohm 左右。当然,这个电阻并不是必须的,在恶劣噪声环境中,可以选用。

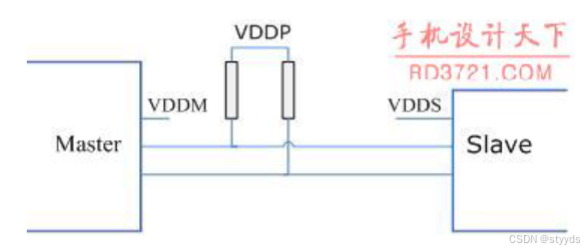

3.上拉电阻电源选择

在部中分应用中,还存在主从设备以及上拉电阻电源不一致的情况,比如 Camera 模组。在很多设计方案中,Camera 模组不工作时,并不是进入 Power Down 模式,而是直接关闭模组供电VDDS。此时,处理器与模组相互连接的所有信号线都应该进入高阻态,否则就会有电流漏入模组;而对于此时的 I2C 控制信号线来说,由于上拉电阻的存在,必须关断上拉电阻电源 VDDP。如果上拉电阻使用的是系统电源 VDDM(VDDP=VDDM),无法关闭,就会有漏电流进入模组;因此这种情况下,应该使用 VDDS 作为上拉电阻电源(VDDP=VDDS),这样上拉电阻电源与 Slave 电源即可同时关闭,切断了漏电路径。

4.I2C总线初始电平

(1)空闲状态电平要求

I2C总线的SDA和SCL信号线在空闲时必须保持高电平,这是通过外部上拉电阻实现的物理层规范。若信号线被强制拉低,会导致上拉电阻持续导通,产生不必要的功耗。

(2)上电初始化配置

当使用软件模拟I2C主设备时:GPIO默认应配置为输入模式(高阻态),依赖外部上拉电阻维持高电平;若配置为输出模式,必须初始化输出高电平+开漏模式(避免强推挽输出低电平锁死总线)

(3)异常场景规避

若IO默认输出低电平(如硬件设计缺陷或软件配置错误),会导致:总线无法进入空闲状态,破坏通信协议时序;

实现建议:初始化阶段先设置GPIO为输入模式,待系统稳定后再切换为开漏输出模式,并通过代码主动拉高信号线,同时使能内部上拉电阻(若硬件支持)

4765

4765

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?