芯片的低功耗

1.1 低功耗的测量数据

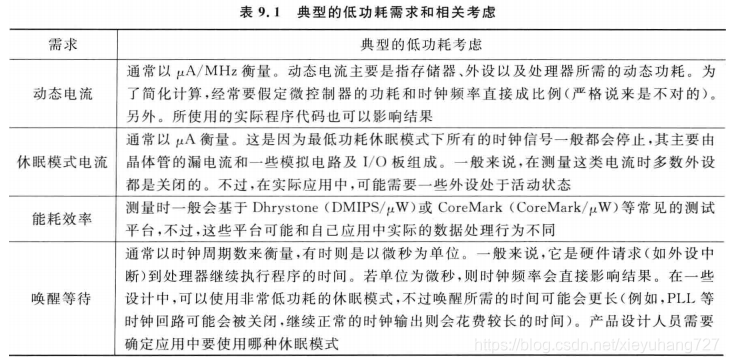

Cortex-M微控制器的一个主要优势在于能耗效率和低功耗特性。能耗效率一般有一定的能量可以完成的工作来衡量,可以为DMIPS/uW或CoreMark/uW等形式,不过,低功耗的测量只会注重动态电流和休眠电流,其中动态电流的单位为uA/MHz, 休眠电流则为uA(时钟停止)。

1.2 低功耗的系统特性

目前,许多Cortex-M微控制器都具有许多可以提高电池寿命的系统特性。例如:

- 多种运行模式和休眠模式

- 超低功耗的实时时钟(RTC)、看门狗和掉电检测(BOD)

- 在处理器处于休眠模式时仍可以运行的只能外设

- 灵活的时钟系统控制特性,设计中不活跃的部分可被关闭

1.3 低功耗的系统需求

低功耗系统在设计时需要考虑的需求如下:

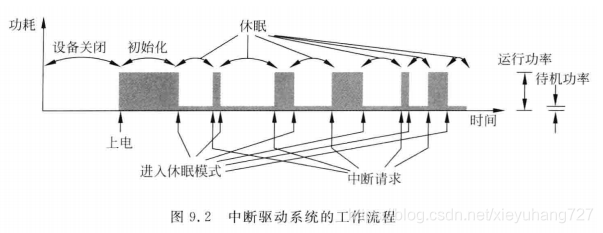

不同的嵌入式系统需要考虑的低功耗需求也是不同的,比如,对于一些电池供电的产品,能耗效率是最为关键的因素,但是对于一些追求实时特性的工控应用来说,唤醒等待时间会更为关键。中断驱动系统的工作流程如下:

若数据处理请求为周期性的,且每次的持续时间都相同,在无须考虑数据处理等待时间的情况下,可以再尽可能低的时钟频率下运行以降低功耗。

1.3.1 Cortex-M3和Cortex-M4处理器的低功耗特点

- 低功耗设计:这两种处理器的硅片面积更小,且具有多种低功耗的优化。

- 高性能:微控制器可以运行在较低的时钟频率下,或者更快的完成处理任务以便可以在休眠模式中多待些时间。

- 高代码密度:对于同一个应用任务,可以使用具有较小Flash存储器的微控制器以降低功耗和成本。

1.4 低功耗系统特性

1.4.1 休眠模式

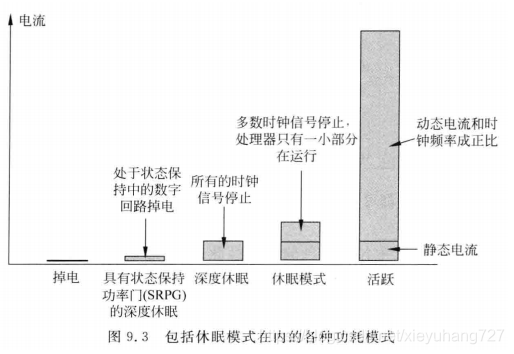

Cortex-M处理器支持两种休眠模式:休眠和深度休眠。有些情况下,深度休眠模式可利用状态保持功率门(SRPG)等高级芯片设计技术进一步降低功耗。休眠期间发生的情况取决于芯片的设计,多数情况下,可以停止部分时钟信号以降低功耗。不过芯片也可以设计为部分关掉。有些情况下,还可以将芯片全部掉电,将处于这种掉电模式下的系统唤醒的唯一方法为系统复位。不同模式的功耗对比如下:

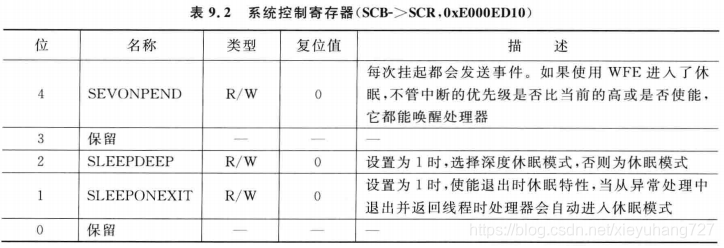

1.4.2 系统控制寄存器(SCR)

SCR => System Control Register(0xE000ED10),利用这个寄存器可以选择进入什么睡眠模式,也可以选择是不是要发送事件。具体如下:

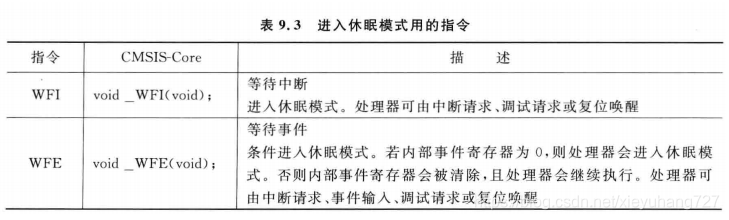

1.4.3 进入休眠模式的指令

处理器提供了两个用于进入休眠模式的指令:WFI和WFE。具体的用法如下:

WFE可由事件唤醒,其中包括事件输入信号脉冲(在处理器中名为RXEV)及之前产生的事件。在处理器内部,之前产生的事件会体现在只有一位的事件寄存器中,该事件寄存器可由下列情况置位:

- 异常进入和退出

- 在使能SEV-ON-PEND特性后,当中断挂起状态由0变为1时,事件寄存器会置位

- 片上硬件的外部事件信号(RXEV)

- SEV(发送事件)指令的执行

- 调试事件(如暂停请求)

与WFI休眠类似,在WFE休眠期间,若中断的优先级高于当前等级,该中断可以将处理器唤醒,不管其优先级是否被BASEPRI屏蔽掉,或者SEV-ON-PEND如何设置。

1.4.4 唤醒条件

多数情况下,中断(包括NMI和Systick定时中断)可以将Cortex-M3或M4从休眠模式中唤醒。不过,有些睡眠模式可能会关掉NVIC或外设的时钟信号,但是具体还是根据芯片而异,可能有的中断时无法唤醒MCU的,只有特定中断才能唤醒。WFI的具体唤醒条件如下:

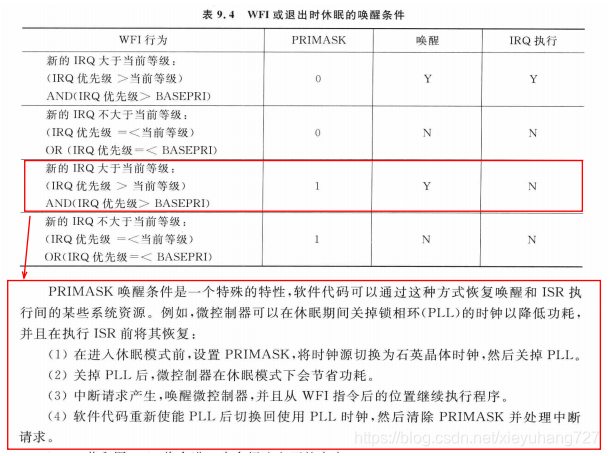

WFE的唤醒和WFI稍有不同,其中一个SEV-ON-PEND的bit位对其影响很大,如果这个bit位置位,无论什么中断产生并被挂起,都会唤醒处在WFE的MCU。具体唤醒条件如下:

注:当SEV-ON-PEND置位,只会在挂起位从0变到1的上升沿才会产生唤醒事件唤醒WFE,如果新产生的中断挂起位已经置位,那么就不会产生唤醒事件了。

本文详细探讨了Cortex-M微控制器的低功耗特性,包括低功耗的测量数据、系统特性,以及如何利用WFE和WFI指令实现低功耗。文章深入解析了休眠模式、系统控制寄存器、唤醒条件和事件通信接口,为开发低功耗应用提供了指导。

本文详细探讨了Cortex-M微控制器的低功耗特性,包括低功耗的测量数据、系统特性,以及如何利用WFE和WFI指令实现低功耗。文章深入解析了休眠模式、系统控制寄存器、唤醒条件和事件通信接口,为开发低功耗应用提供了指导。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1775

1775

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?