指导书原文

4.1 实验CPU算术逻辑单元

4.1.1、实验目的

1、掌握简单运算器的数据传送通路

2、验证运算器的组合功能

4.1.2、实验原理

算术逻辑部件的主要功能是对二进制数据进行定点算术运算、逻辑运算和各种移位操作。算术运算包括定点加减乘除运算;逻辑运算主要有逻辑与、逻辑或、逻辑异或和逻辑非操作。ALU通常有两个数据输入端A和B,一个数据输出端Y以及标志位等。

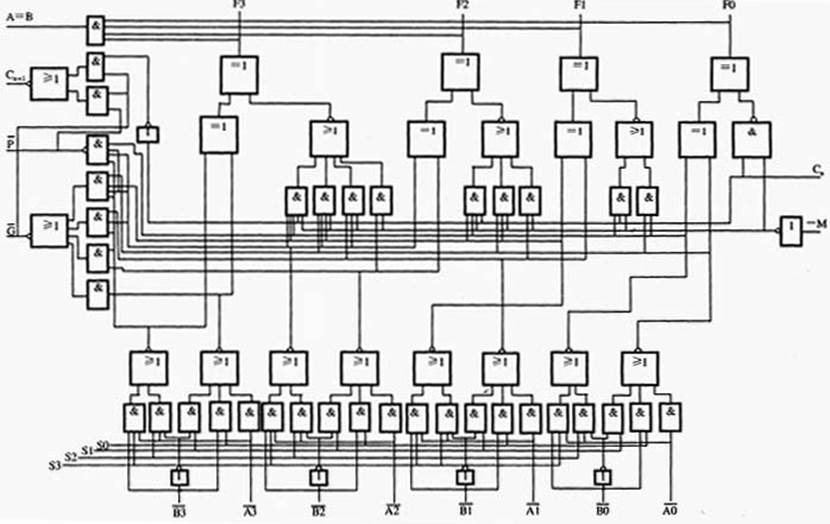

74181是一种典型的4位ALU器件。图4.1是74181的电路图。

20世纪80年代计算机中的算是逻辑单元有许多是用现成的算术逻辑器件连接起来构成的。如上面提到的74181和Am2901等就是著名的算术逻辑器件。使用这些4位的算术逻辑器件,能够构成8位、16位等长度的算术逻辑单元。现在由于超大规模器件的广泛应用,使用这种方法构成算术逻辑单元已经不多见,代之以直接用硬件描述语言设计算术逻辑单元。CPU的算术逻辑单元就是一个简单的例子 。

图4.1 74181的电路图

4.1.3、实验要求

1、实验设计目标

设计一个16位算术逻辑单元,满足以下要求。

(1)16位算术逻辑单元能够进行下列运算:加法、减法、加1、减1、与、或、非和传送。用3位运算操作码OP[210]进行运算,控制方式如表4.1所示:

| 运 算 | 对标志位Z和C的影响 | |

| resultßA+B | 影响标志位Z和C | |

| resultßA+1 | 影响标志位Z和C | |

| resultßA-B | 影响标志位Z和C | |

| resultßA-1 | 影响标志位Z和C | |

| resultßA and B | ||

| resultßA or B | ||

| resultßnot B | ||

| resultß B | 不影响标志位Z和C |

(2)设立两个标志位寄存器Z和C。当复位信号reset为低电平时,将这两个标志寄存器清零。当预算结束后,在时钟CLK的上升沿改变标志寄存器Z和C的值。运算结果改变标志寄存器C、Z的情况下:加法、减法、加1、减1、运算改变Z、C;与、或、非运算改变Z,C保持不变;传送操作保持Z、C不变。因此在运算结束时,Z、C需要两个D触发器保存。

(3)为了保存操作数A和B。设计两个16位寄存器A和B。当寄存器选择信号sel=0时。如果允许写信号write=1,则在时钟clk的上升沿将数据输入dinput送入A寄存器;当sel=1时,如果允许写信号write=1,则在时钟clk的上升沿将数据输入dinput送入B。

(4)算术逻辑单元用一个设计实体完成。

2、顶层设计实体的引脚要求

- 引脚要求对应关系如下:

- clk对应实验台上的时钟(单脉冲);

- reset对应实验台上的CPU复位信号CPU_RST;

- 数据输入dinput对应实验台开关SD15~SD0;

- 允许写信号write对应实验台开关SA5;

- OP[210]对应实验台开关SA2~SA0;

- 寄存器选择信号sel对应实验台开关SA4;

- 16位运算结果result对应实验台上的指示灯A15~A0;

- Z、C标志位对应实验台上的Z、C指示灯。

4.1.4、实验步骤及结果现象观察(根据前面的设计目标和顶层设计引脚要求)

- 连接USB通信线。

2、打开Quartus->tools->programmer,将booth_multiplier.sof下载到FPGA中。

3、在实验台上通过模式开关选择REGSEL=0、M[2:0]=“上(1)、上(1)、下(0)”、FDSEL=0。

4、实验过程中按“单脉冲”模拟主板时钟脉冲完成实验。

(1)输入A这个数:Sel=0(SA4),write=1(SA5),A数(SD15~SD0),按一下单脉冲按钮(单脉冲按钮),使之存入A寄存器;

(2)输入B这个数:Sel=1(SA4),write=1(SA5),B数(SD15~SD0),按一下单脉冲按钮(单脉冲按钮),使之存入B寄存器;

以上两步每组数据做一次。

(3)输入功能码OP[210](SA2~SA0),按一下单脉冲按钮(单脉冲按钮);

(4)观察16位运算结果result(A15~A0)及Z、C指示灯(只有操作码拨完毕并按下单脉冲按钮后才有效,中间的Z、C无效),灯亮是1,灯灭是0;

3、4步每行表格做一次。

- 复位:为了前一次运算结果不影响后一次运算结果,请按一次实验箱右下角的“CPU复位”按钮开关;

5步每组数据做一次,作用是清空A、B寄存器。

(6)重复实验步骤(1)--(5)对以下4组数据进行表4.1的8种运算,把运算结果及标志位填写在表4.2中:

注意分析:每行语句z和c标志位改变的原因和不改变的原因。

4.1.5 思考题

1、如果保持原有操作码功能不变,运算器单元加上逻辑左移、逻辑右移等操作,那该如何处理?

4.2 实验CPU 存储器

4.2.1 实验目的

(1)理解计算机的存储器分类及作用;

(2)掌握TEC-CA实验台上存储器器件的工作原理及读写方法。

4.2.2实验原理

- 存储器按存取方式分,可分为随机存储器和顺序存储器。如果存储器中的任何存储单元的内容都可随机存放,称为随机存储器,计算机中的主存储器都是随机存储器。如果存储器只能按照某种顺序存起,则称为顺序存储器,磁带是顺序存储器,磁盘是版顺序存储器,它们的特点是存储量大,存储速度慢,一般作为外部存储器使用。

- 按存储器的读写功能分,只读存储器和随机读写存储器。有些存储器的内容是固定不变的,即只能读出不能写入,这种存储器称为只读存储器(ROM);既能读出又能写入的存储器,称为随机读写存储器(RAM)。实际上正真的ROM已经基本不用了,用的是光可擦除可编程的ROM(EPROM)和电可擦除可编程的ROM(E2PROM)。E2PROM用得越来越多了,有取代EPROM之趋势。比如容量很大的闪存flash现在就用得很广泛,常说的U盘就是用Flash做的。

- 按信息的可保存性分,存储器可分为非永久性记忆存储器和永久性存储器。ROM、EPROM、E2PROM都是永久记忆存储器,它们断电后存储内容可保存。RAM则是非永久性记忆存储器,断电后存储器中存储的内容丢失。

下面主要讲述随机读写存储器:

随机存储器按其元件的类型来分,有双极存储器和MOS存储器两类。在存取速度和价格两方面,双极存储器比MOS存储器高,故双极存储器主要用于高速的小容量存储体系。在MOS存储器中,根据存储信息机构的原理不同,又分为静态随机存储器(SRAM)和动态随机存储器(DRAM)。静态随机存储器采用双稳态触发器来保存信息,只要不断电,信息就不会丢失;动态随机存储器利用记忆电容来保存信息,使用时只有不断地给电容充电才能使信息保持。静态随机存储器的集成度较低,功耗也较大;动态随机存储器的集成度较高,功耗低。现在计算机中,内存容量较大,常由动态随机存储器构成。

1、静态随机存储器SRAM

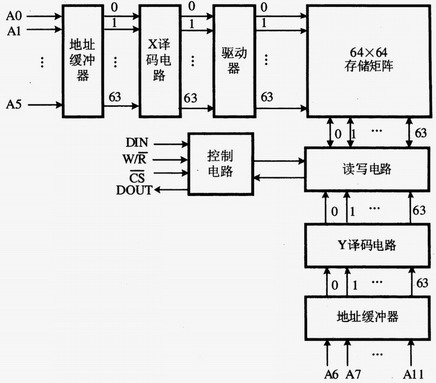

静态存储器由存储体、地址译码电路、读写电路和控制电路组成。一个4096×1位的SRAM的结构框图如图4.2所示。图中,A0~A11为地址线,用来寻址存储器中的某一个单元。DIN、DOUT为数据线,实现数据的输入、输出。W/为读写控制信号线,用来实现读写操作控制。为片选信号。

2、动态随机存储器DRAM

动态随机存储器(DRAM)和SRAM一样,也是由许多基本存储电路按照行和列来组成的。DRAM是以MOS管栅极和衬底间电容上的电荷来存储信息的。由于MOS管栅极上的电荷会因漏电而泄放,故存储单元中的信息只能保持若干秒,为此DRAM必须附加刷新逻辑电路。另外,DRAM将地址分为行地址和列地址,并分时复用以减少引脚数目。常见的4164芯片即是DRAM。

图 4.2 SRAM结构框图

4.2.3 存储器单位

计算机存储单位一般用bit、B、KB、MB、GB、TB、PB、EB、ZB、YB、BB、NB、DB……来表示,它们之间的关系是:

位 bit (比特)(Binary Digits):存放一位二进制数,即 0 或 1,最小的存储单位。[英文缩写:b(固定小写)]

字节byte:8个二进制位为一个字节(B),最常用的单位。

1 Kilo Byte(KB) = 1024 (2^10) byte

1 Mega Byte(MB) = 1024 KB

1 Giga Byte (GB)= 1024 MB

1 Tera Byte(TB)= 1024 GB

1 Peta Byte(PB) = 1024 TB

1 Exa Byte(EB) = 1024 PB

1 Zetta Byte(ZB) = 1024 EB

1Yotta Byte(YB)= 1024 ZB

1 Bronto Byte(BB) = 1024 YB

1Nona Byte(NB)=1024 BB

1 Dogga Byte(DB)=1024 NB

1 Corydon Byte(CB)=1024DB

硬盘容量,一般的制造商总是用十进制的计数。一般计算机的操作系统都是使用2进制的计数,所以你经常会发现在计算机看到的硬盘容量比硬盘上的实际可用容量要小,比如20GB的硬盘只显示有18.6GB。

4.2.4 TEC-CA实验台上的存储器器件HM6116

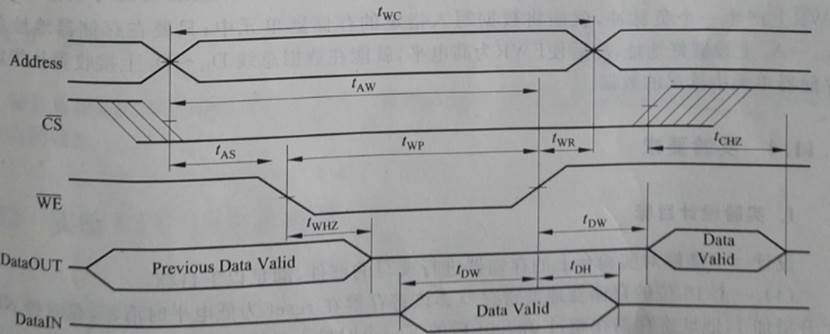

1、存储器HM6116的读写时序

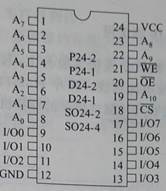

静态随机存储器器件有许多型号,分为同步和异步两大类。HM6116是一种比较常用的异步静态随机存储器器件。它是一种2K x 8bit的存储器器件。图4.3所示是HM6116器件的外形图。

图4.3 静态存储器HM外形图

在图4.3中,A10~A0是存储器地址总线,I/O7~I/O0是双向数据总线,从存储器读出的数据或者写入存储器的数据通过数据总线完成。`![]() 是片选,只有

是片选,只有![]() 为低电平时才能对存储器进行读写操作。

为低电平时才能对存储器进行读写操作。![]() 写信号,当

写信号,当![]() 为低电平时(在

为低电平时(在![]() 低电平的情况下),将数据总线I/O7~I/O0上的数据写入由地址总线A10~A0指定的存储单元中。

低电平的情况下),将数据总线I/O7~I/O0上的数据写入由地址总线A10~A0指定的存储单元中。![]() 是读信号,当

是读信号,当![]() 为低电平(在

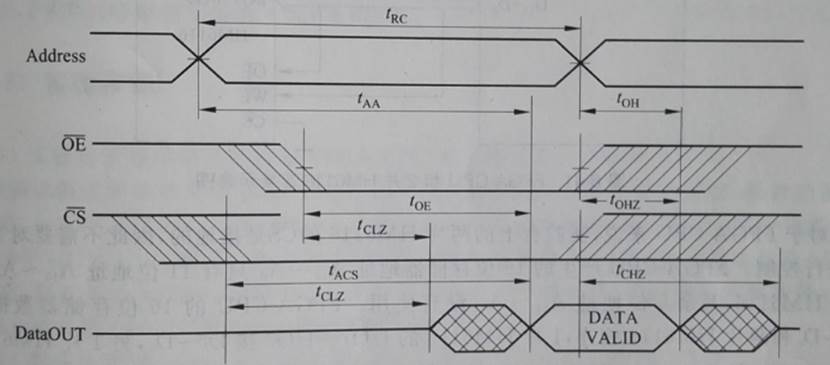

为低电平(在![]() 低电平的情况下)时,将地址总线A10~A0指定的存储单元中的数据读到数据总线I/O7~I/O0上。图4.4和4.5所示是HM6116的读写操作时序图。

低电平的情况下)时,将地址总线A10~A0指定的存储单元中的数据读到数据总线I/O7~I/O0上。图4.4和4.5所示是HM6116的读写操作时序图。

图4.4 HM6116读操作时序图

图4.5 HM6116写操作时序图

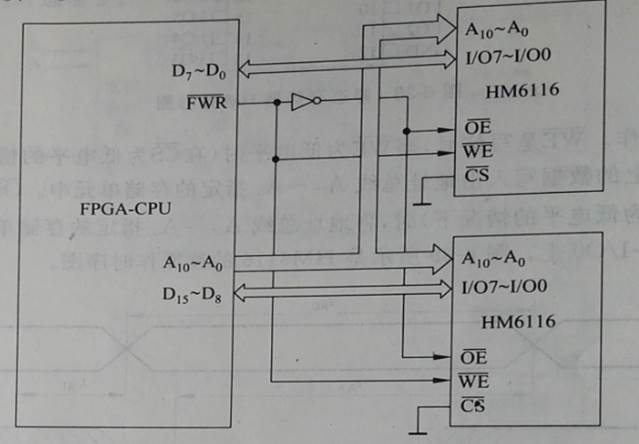

2、TEC-CA实验台上HM6116的使用

在TEC-CA开放式CPU实验教学系统实验台上,有两片静态存储器器件HM6116。HM6116有8位数据总线和11位地址总线。两片HM6116构成2K x 16bit的静态存储器,与FPGA-CPU一起构成了能够运行测试程序的计算机。图4.6 所示是FPGA-CPU和两片HM6116连接示意图。

图4.6 FPGA-CPU 和2片HM6116连接示意图

对于FPGA-CPU来说,实验台上的两片HM6116的![]() 是接地的,因此不需要对它们的

是接地的,因此不需要对它们的![]() 进行控制。FPGA-CPU产生的16位存储器地址A15~A0只有11位地址A10~A0送往两片HM6116,其余5位地址A15~A11没有使用。FPGA-CPU的16位存储器数据总线D15~D0和两片HM6116相连,1片HM6116的I/O7~I/O0接D7~D0,另1片HM6116的I/O7~I/O0接D15~D8。FPGA-CPU输出的存储器控制信号

进行控制。FPGA-CPU产生的16位存储器地址A15~A0只有11位地址A10~A0送往两片HM6116,其余5位地址A15~A11没有使用。FPGA-CPU的16位存储器数据总线D15~D0和两片HM6116相连,1片HM6116的I/O7~I/O0接D7~D0,另1片HM6116的I/O7~I/O0接D15~D8。FPGA-CPU输出的存储器控制信号![]() 直接送两片HM6116的

直接送两片HM6116的![]() ;

;![]() 在实验台经过一个反相器反相后送两片HM6116的

在实验台经过一个反相器反相后送两片HM6116的![]() 。因此FPGA-CPU只要在存储器地址总线A10~A0设置好地址,在数据总线D15~D0上送出被写数据,然后在

。因此FPGA-CPU只要在存储器地址总线A10~A0设置好地址,在数据总线D15~D0上送出被写数据,然后在![]() 上产生一个负脉冲,就能将数据写入指定的存储单元中;只有在存储器地址总线A10~A0上设置好地址,然后使

上产生一个负脉冲,就能将数据写入指定的存储单元中;只有在存储器地址总线A10~A0上设置好地址,然后使![]() 为高电平,就能在数据总线D15~D0上接收到从指定的存储器单元中读出的数据。

为高电平,就能在数据总线D15~D0上接收到从指定的存储器单元中读出的数据。

4.2.5 实验要求

1、实验设计目标

设计一个能够对实验台上的存储器进行读写的部件,满足以下目标:

- 一个16位的存储器地址寄存器。该寄存器在reset位低电平时清理,在时钟clk的上升沿加1,地址寄存器在超过0x000f后的下一个时钟上升沿回到0.

- 一个标志寄存器,在reset为低电平时复位位0,当存储器地址寄存器等于0x000f后,下一个时钟clk的上升沿标志寄存器翻转。

- 在标志寄存器为0时执行存储器的存储功能,存储器的0单元开始存16个16位数。按动一次单脉冲按钮,存一次数,存的数由内部产生,不由实验台开关输入。

- 当标志寄存器为1时,执行从存储器的0单元开始的读数功能。按动一次单脉冲按钮,读一次数,一直读16个数。读出的数据送入一个16位信号R[15…0]中暂存。

注意,当需要从存储器中读取数据时,首先将“ZZZZZZZZZZZZZZZZ”赋值给数据总线,然后才能读取存储器中的数据。

2、顶层设计实体的引脚要求

引脚要求对应关系如下:

- clk对应实验台上的时钟(单脉冲)。

- reset对应实验台上的CPU复位信号CPU_RST。

- 存储器地址总线A[15…0]对应实验台上的指示灯A15~A0。

- 存储器数据总线D[15…0]对应实验台上的数据指示灯D15~D0。

- 16位信号R[15…0]对应实验台上的指示灯R15~R0。

信号对应实验台上的

信号对应实验台上的 信号。

信号。

4.2.6 实验步骤

- 连接USB通信线。

2、打开Quartus->tools->programmer,将booth_multiplier.sof下载到FPGA中。

3、在实验台上通过模式开关选择REGSEL=0、M[2:0]=“上(1)、上(1)、下(0)”、FDSEL=0。

4、实验过程中按“单脉冲”模拟主板时钟脉冲完成实验。

5、首先按实验台上的CPU复位按钮,将存储器地址寄存器复位为0,然后按下单脉冲按钮,不断观察实验台上的指示灯,察看结果与预想的是否一致。(照几张照片,加上对每张照片处于的状态的说明,写在报告中。)

4.2.7 思考题

如果从存储器中读出数据时不首先向数据总线送出“ZZZZ ZZZZ ZZZZZZZZ”,那么会发生什么问题?送这个“ZZZZZZZZZZZZZZZZ”用处是什么?

实操Warning

这次实验卡了我的一个地方在于存储数据。

请认真阅读实验指导书:

(1)输入A这个数:Sel=0(SA4),write=1(SA5),A数(SD15~SD0),按一下单脉冲按钮(单脉冲按钮),使之存入A寄存器;

(2)输入B这个数:Sel=1(SA4),write=1(SA5),B数(SD15~SD0),按一下单脉冲按钮(单脉冲按钮),使之存入B寄存器;

存储数据A,你的SA4是0,存储数据B,你的SA4要拨成1!!!

不然你的B会把A覆盖掉了,做出来的实验结果自然就是“A怎么像B啊,A怎么没存到啊”,实际上是因为存储被覆盖了。

实验报告

实验过程

| 实验一——CPU算术逻辑单元 (一)实验步骤 1、 连接USB通信线。 2、打开Quartus->tools->programmer,将booth_multiplier.sof下载到FPGA中。 3、在实验台上通过模式开关选择REGSEL=0、M[2:0]=“上(1)、上(1)、下(0)”、FDSEL=0。 4、实验过程中按“单脉冲”模拟主板时钟脉冲完成实验。 (1)输入A这个数:Sel=0(SA4),write=1(SA5),A数(SD15~SD0),按一下单脉冲按钮(单脉冲按钮),使之存入A寄存器; (2)输入B这个数:Sel=1(SA4),write=1(SA5),B数(SD15~SD0),按一下单脉冲按钮(单脉冲按钮),使之存入B寄存器; 以上两步每组数据做一次。 (3)输入功能码OP[210](SA2~SA0),按一下单脉冲按钮(单脉冲按钮); (4)观察16位运算结果result(A15~A0)及Z、C指示灯(只有操作码拨完毕并按下单脉冲按钮后才有效,中间的Z、C无效),灯亮是1,灯灭是0; 3、4步每行表格做一次。 (5)复位:为了前一次运算结果不影响后一次运算结果,请按一次实验箱右下角的“CPU复位”按钮开关; 5步每组数据做一次,作用是清空A、B寄存器。 (6)重复实验步骤(1)--(5)对以下4组数据进行表4.1的8种运算 (二)实验结果记录

实验二——CPU 存储器 (一)实验步骤 1、 连接USB通信线。 2、打开Quartus->tools->programmer,将booth_multiplier.sof下载到FPGA中。 3、在实验台上通过模式开关选择REGSEL=0、M[2:0]=“上(1)、上(1)、下(0)”、FDSEL=0。 4、实验过程中按“单脉冲”模拟主板时钟脉冲完成实验。 5、首先按实验台上的CPU复位按钮,将存储器地址寄存器复位为0,然后按下单脉冲按钮,不断观察实验台上的指示灯,察看结果与预想的是否一致。 (二)实验结果 在进行TEC-CA实验台上的HM6116存储器操作实验时,观察到如下现象: 初始状态:当实验仪器的地址位和数据位均为0到15时,读/写指示灯处于熄灭状态。这表明在该状态下,存储器进行写入操作。 地址变化后的状态:随后,当地址位从0到15依次变化时,读/写指示灯亮起。这说明在地址位发生变化的过程中,存储器正在进行读取操作,具体操作类型需结合实验设置的读写控制信号来判断。若实验中设置为写操作,此时存储器正在将数据写入指定地址的存储单元;若设置为读操作,则存储器正在从指定地址的存储单元中读取数据。 综上所述,实验结果表明,当地址位保持不变且数据位为0到15时,存储器未进行读写操作;而当地址位发生变化时,存储器开始执行读写操作,此时读/写指示灯亮起。 例如:图1是指示灯熄灭状态,正在写入数据“2”;图2是从写到读的临界状态;图3是指示灯熄灭状态,正在读出数据“5”;图4是从读到写的临界状态;

图 1

图 2

图 3

图 4 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

思考题部分

| 分析:每行语句z和c标志位改变的原因和不改变的原因? 答:Z(零标志位)和C(进位标志位)的改变取决于不同的运算类型和运算结果: 零标志位(Z)变化原因: Z=1:当运算结果为全0时置1。例如: A=0xFFFF +1 结果为0x0000,如第2组数据 A=0x0000 and B=0x0000 结果为全0,如第2组数据 not B=0xFFFF 结果为0x0000,如第3组数据 Z=0:当运算结果不为全0时保持0。大多数运算结果都非零,所以Z保持0。 进位标志位(C)变化原因: C=1:主要发生在算术运算中: 加法运算产生进位,如第4组A+B=0x8950+0x9863=0x121B3,最高位进位 减法运算需要借位,如第3组A-B=0x0000-0xFFFF,需要借位 特殊情况:A=0xFFFF +1 产生进位,如第2组数据 C=0:当算术运算不产生进位/借位时保持0,或逻辑运算不影响C标志位 不改变的原因: 逻辑运算(AND/OR/NOT)通常不影响C标志位 当运算结果既没有进位/借位,结果也不是全0时,两个标志位都保持0 如果保持原有操作码功能不变,运算器单元加上逻辑左移、逻辑右移等操作,那该如何处理? 答:要添加移位操作而不改变原有操作码功能,可以考虑以下方法: 1.扩展操作码位数: 当前使用3位操作码(OP[2:0]),可以增加1位作为移位/算术逻辑选择位 例如:OP[3]=0时执行原有算术逻辑运算,OP[3]=1时执行移位操作 2.复用现有操作码组合: 选择当前未使用的操作码组合来代表移位操作 例如:若000-111已被使用,可以扩展为4位操作码 3.添加移位控制信号: 增加移位方向控制信号(左/右) 增加移位位数输入 4.硬件修改: 在ALU中增加移位器单元 修改控制逻辑以支持新的移位指令 确保标志位能正确反映移位操作结果(特别是C标志位可以反映移出的位) 如果从存储器中读出数据时不首先向数据总线送出“ZZZZZZZZZZZZZZZZ”,那么会发生什么问题?送这个“ZZZZZZZZZZZZZZZZ”用处是什么? 答:可能发生的问题: 总线冲突:如果存储器输出和CPU输出同时驱动总线,会导致多个驱动源竞争总线,可能损坏电路或产生不确定的逻辑电平。 数据错误:前一次操作留下的数据可能会与新读取的数据产生冲突,导致读取错误。 信号完整性问题:多个驱动源同时驱动总线可能导致信号振荡或电压电平不稳定。 "ZZZZZZZZZZZZZZZZ"的作用: 高阻态隔离:Z表示高阻态,相当于断开连接。先输出全Z确保存储器输出前总线处于无驱动状态,避免冲突。 总线释放:让前一个使用总线的设备完全释放总线控制权。 信号稳定:提供一个"安静期",让总线上的电容放电,确保新数据能够正确传输。 时序控制:作为读写转换的同步点,确保存储器有足够时间切换读写状态。 防止误操作:避免在状态切换过程中产生中间值被误认为是有效数据。 这种设计是典型的"三态总线"管理策略,在计算机系统中很常见,用于确保多设备共享总线时的可靠通信。 |

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?