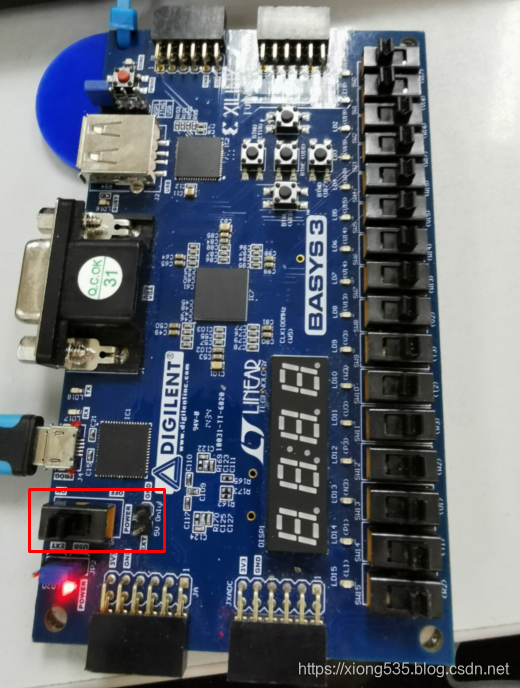

- 开发板资料在网上搜索BASYS3即可查到

- 一个很简单的项目上手(按键控制灯的亮灭),主要练习vivado的使用

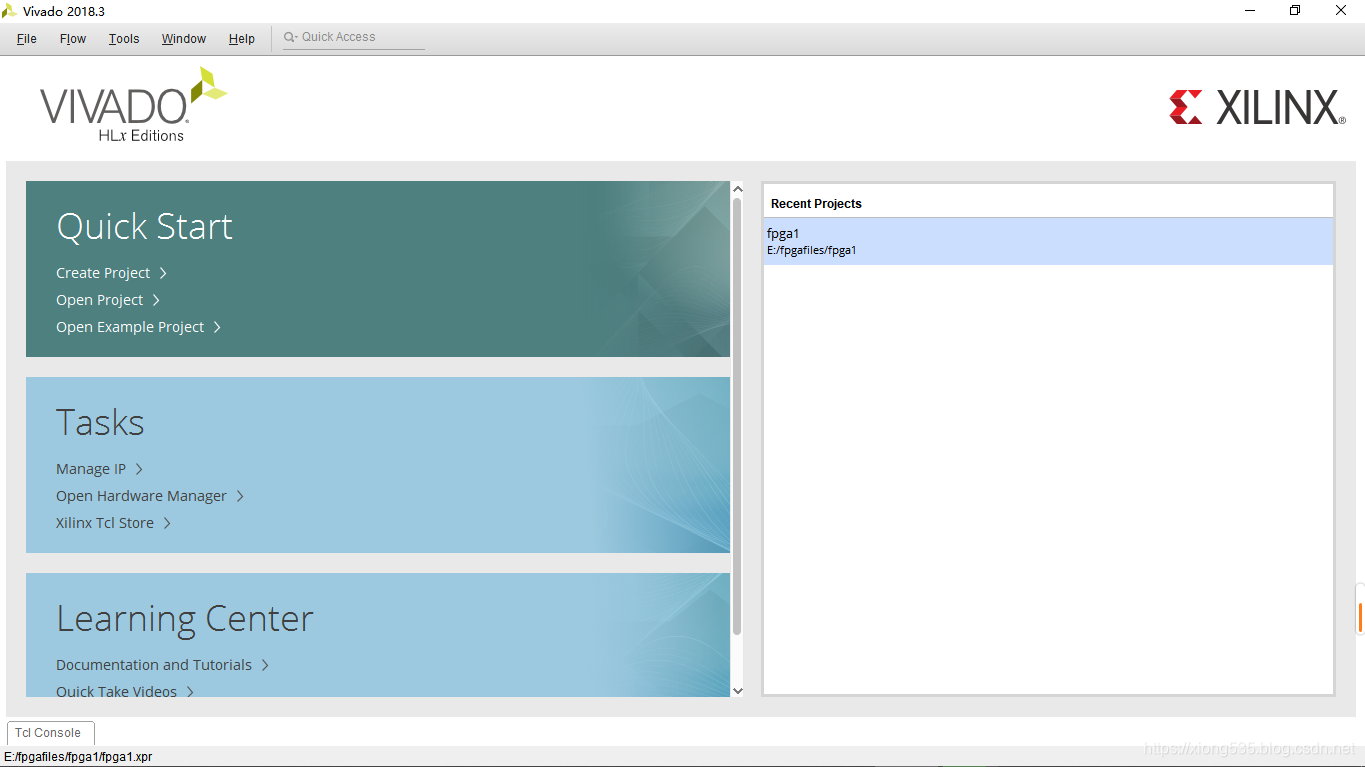

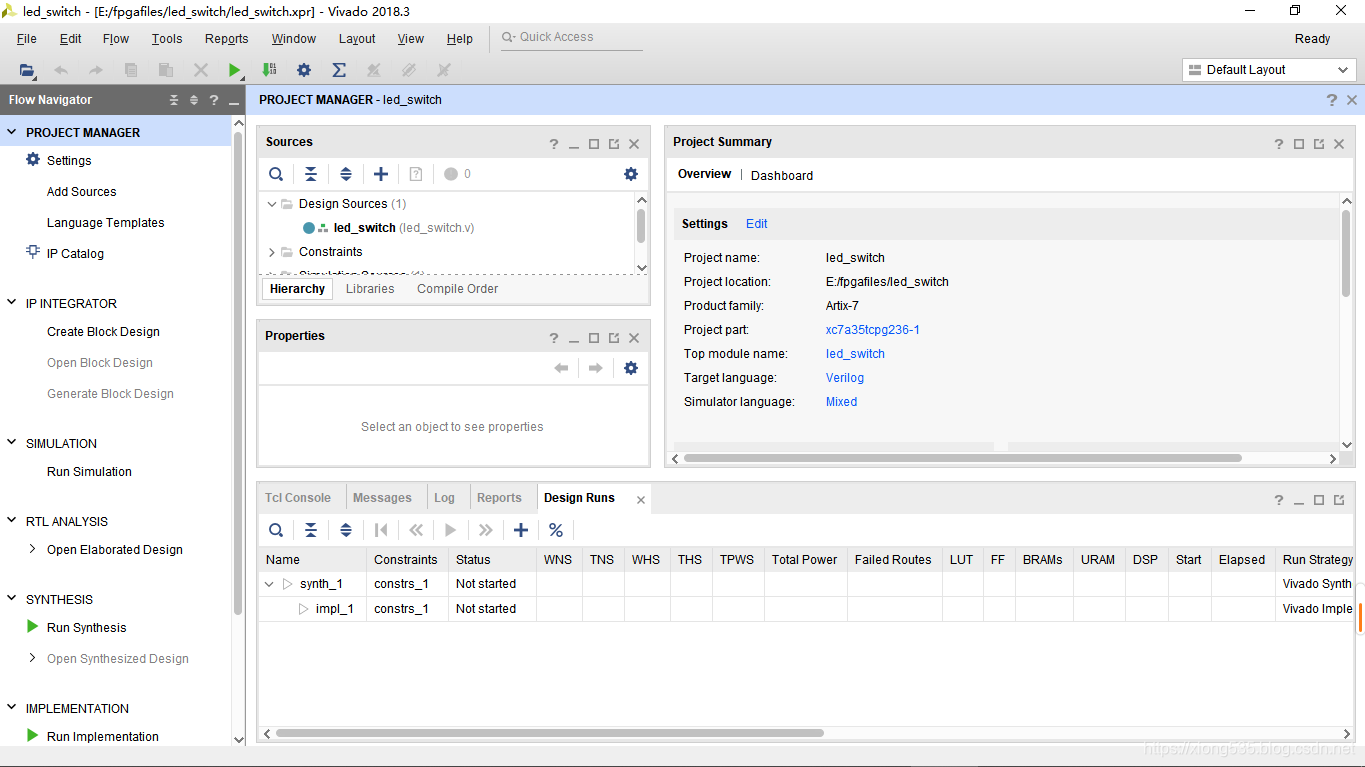

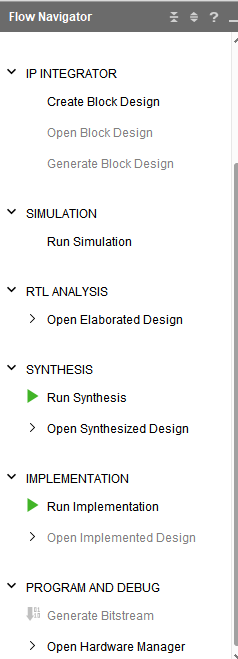

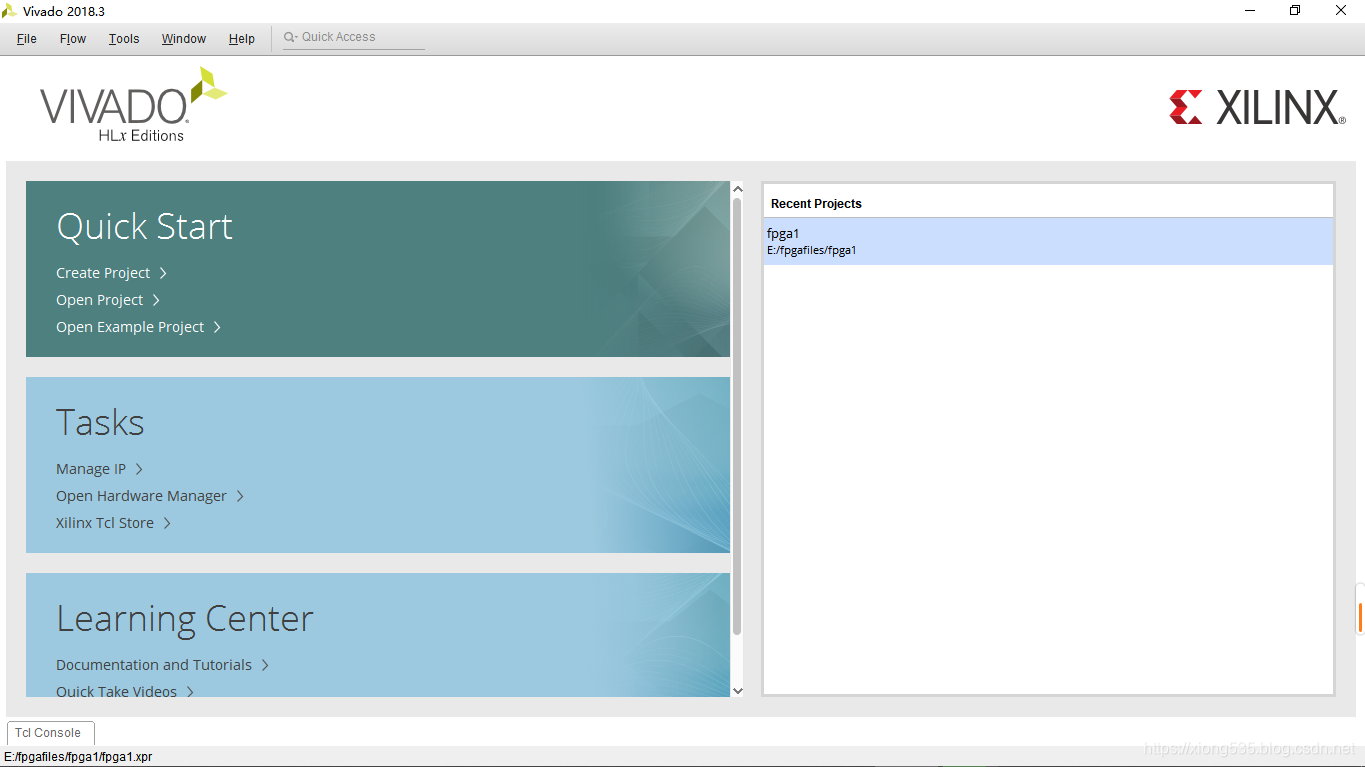

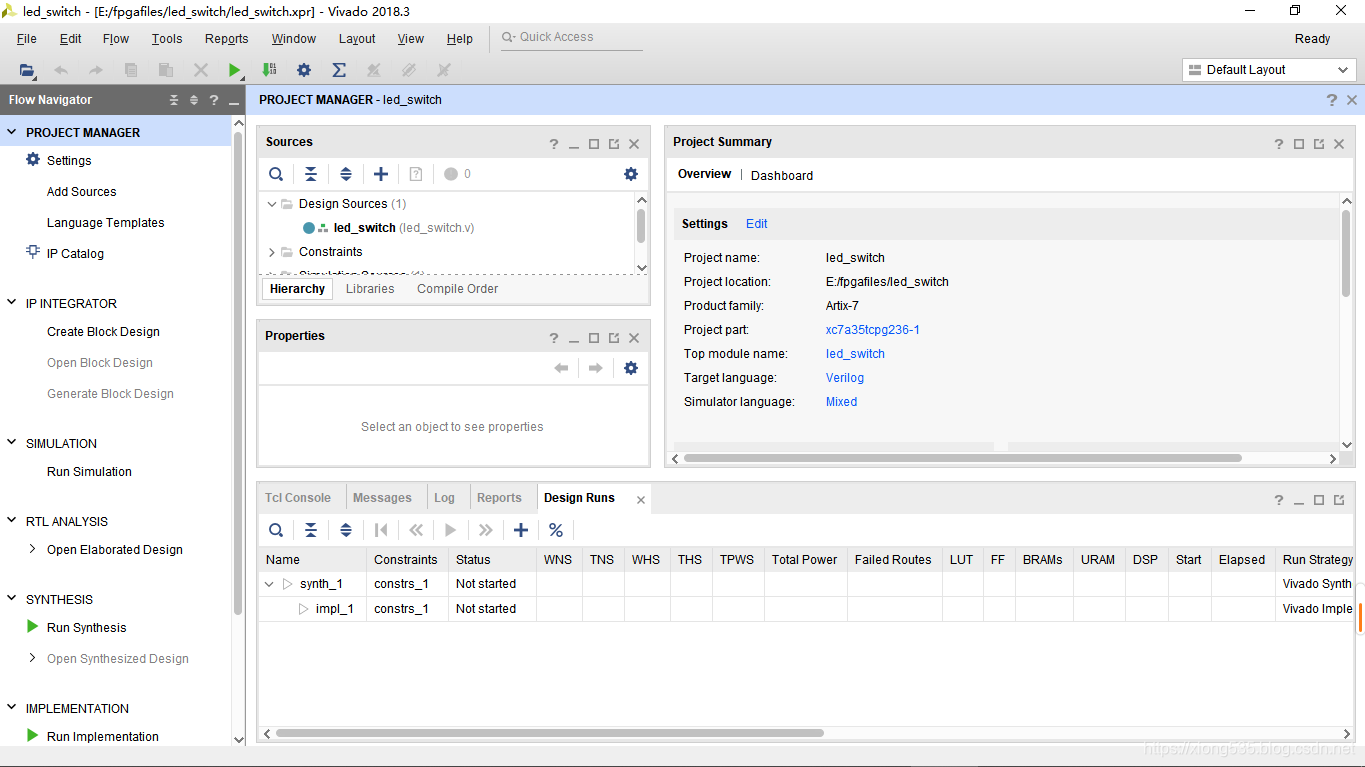

- 主界面

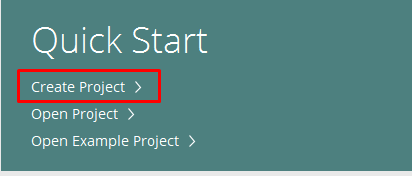

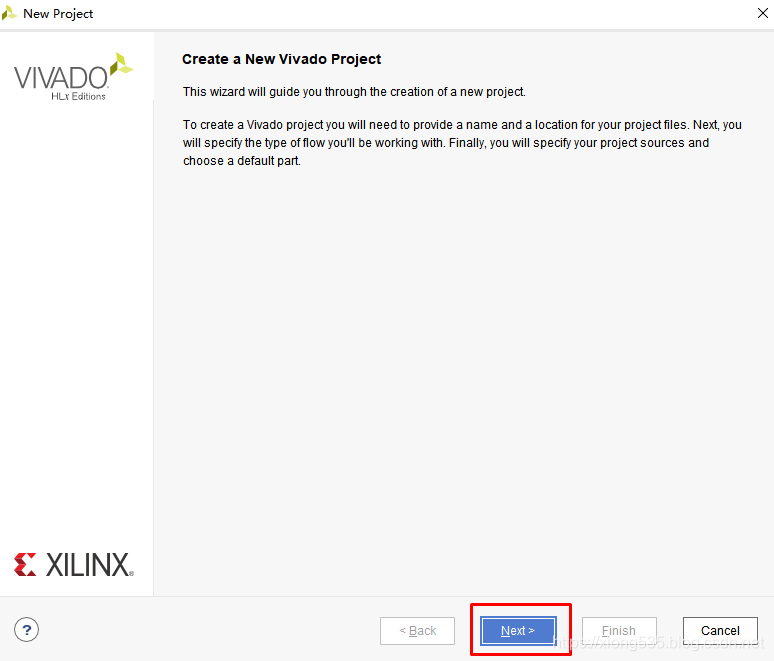

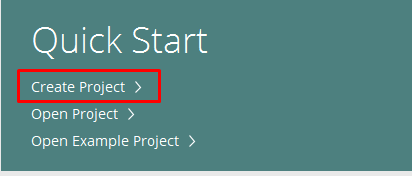

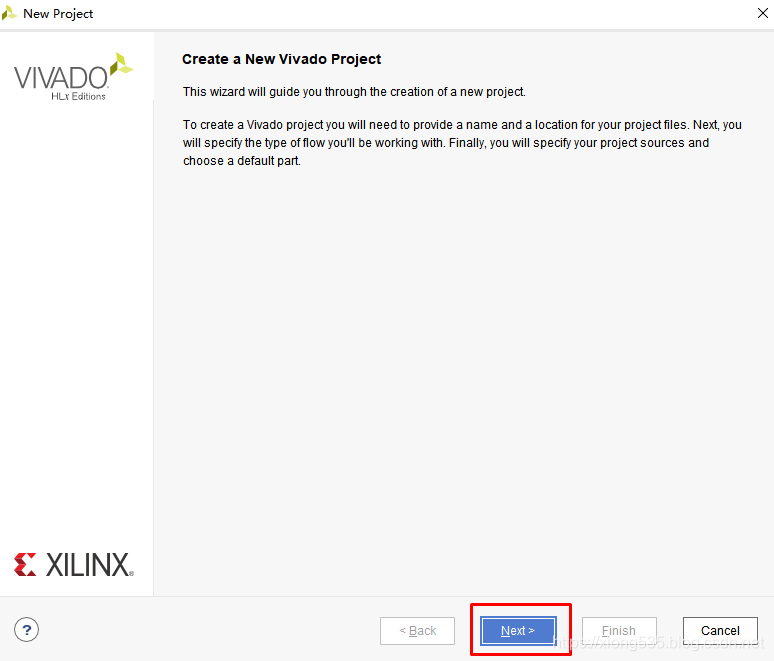

- 新建工程

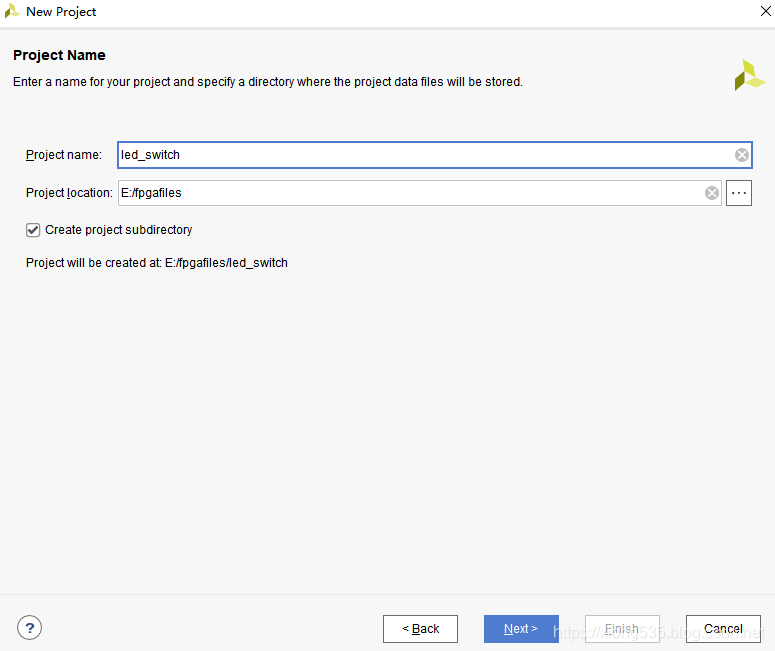

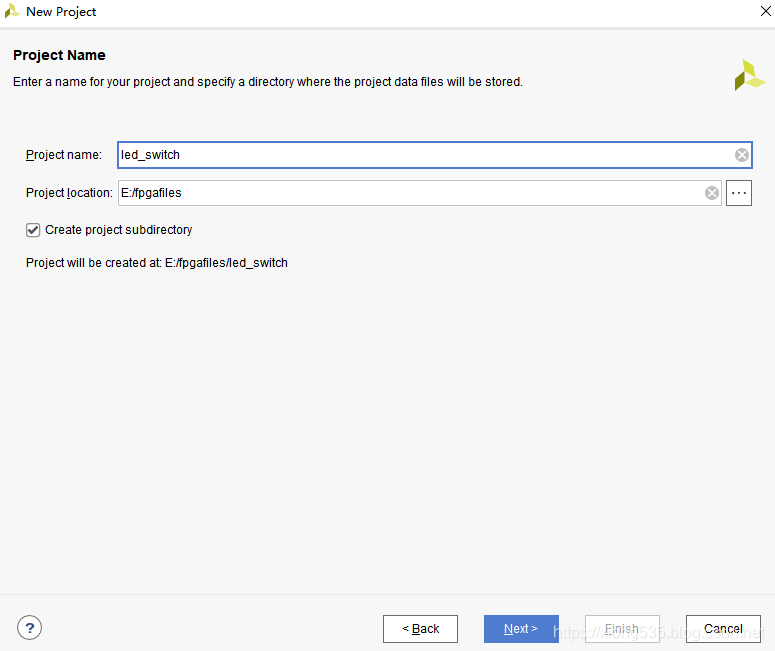

- 给工程取名,注意不要带空格,next

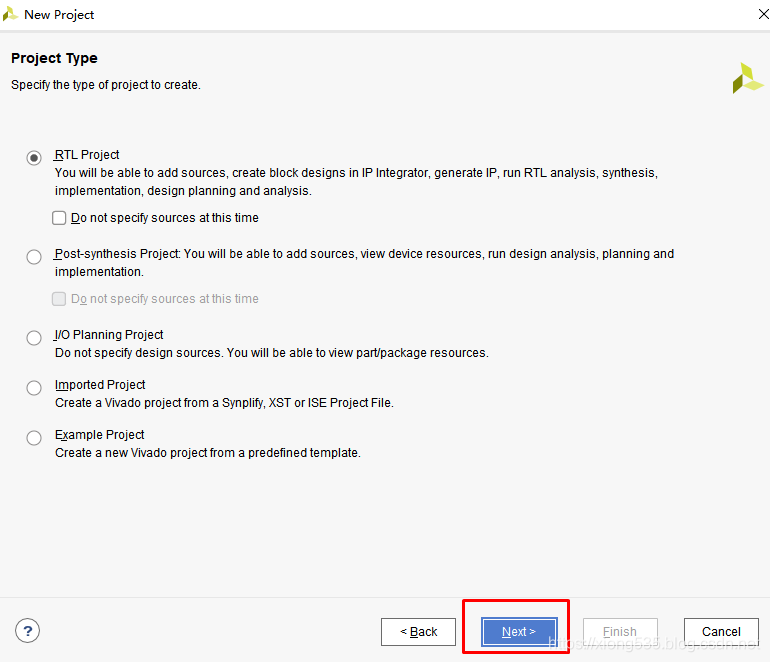

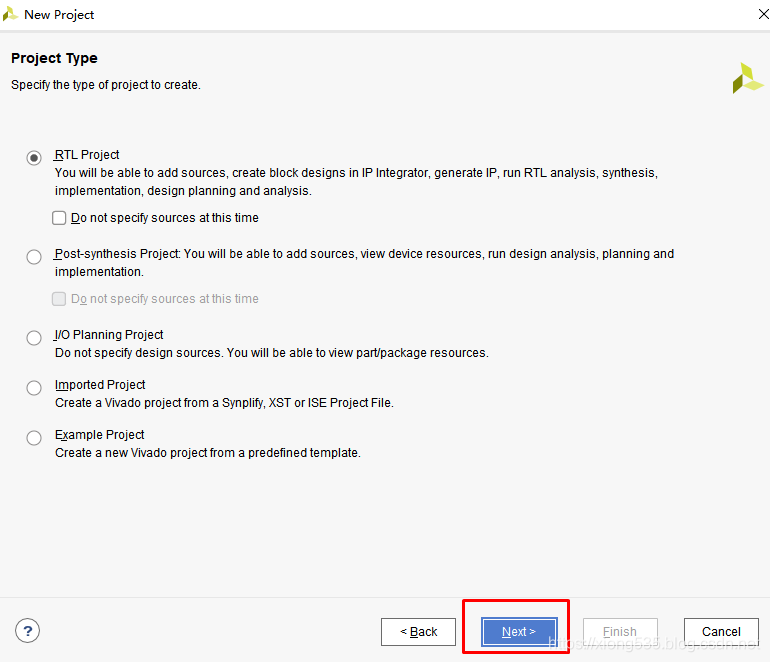

- 首选项

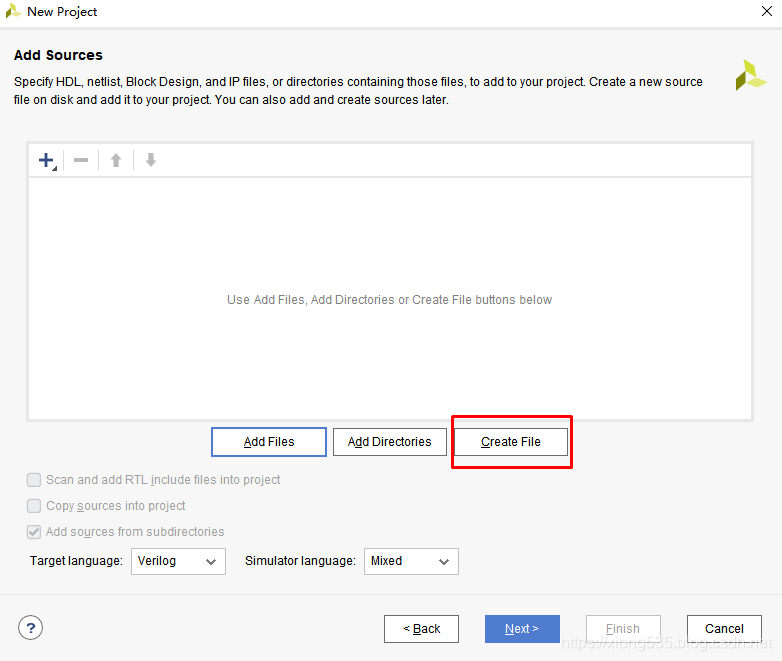

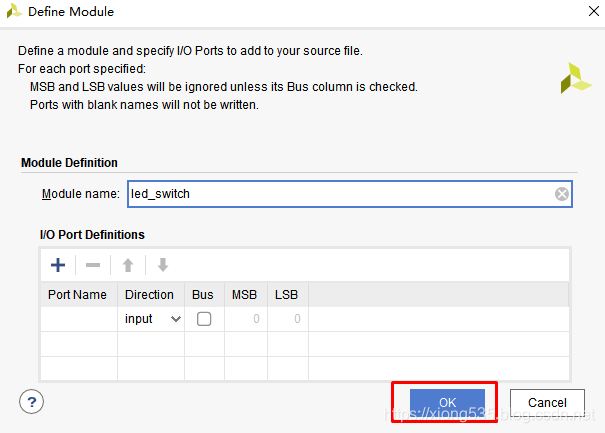

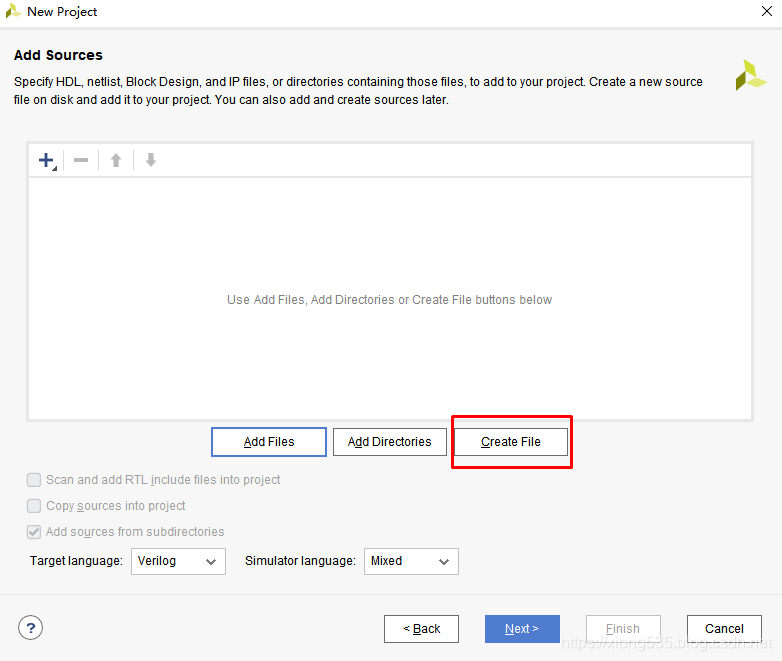

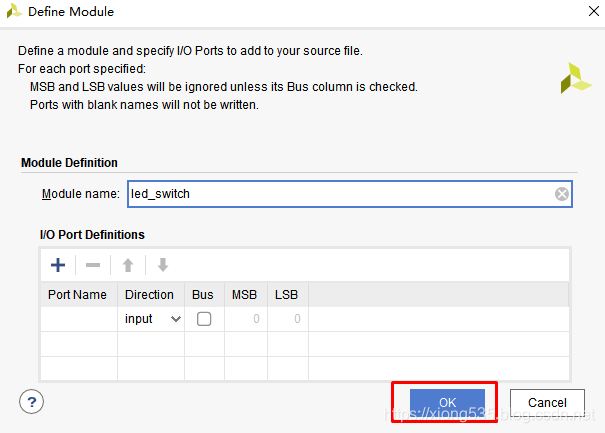

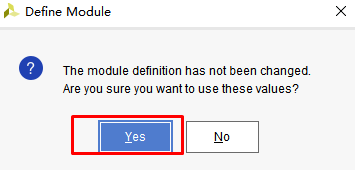

- creat file

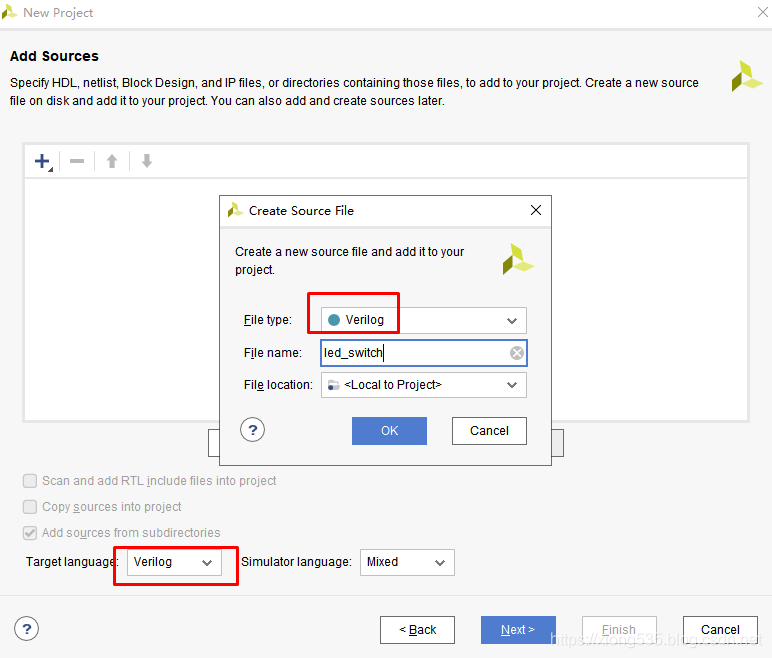

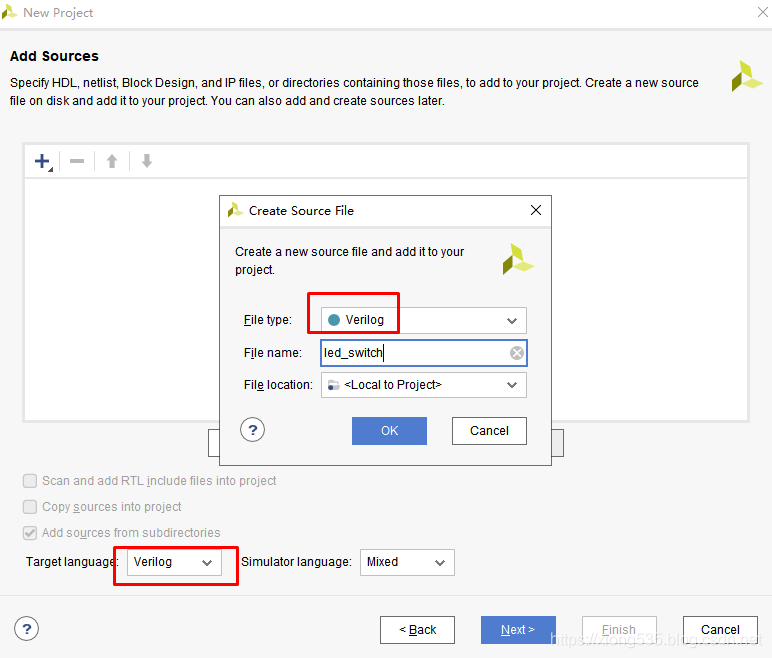

- 语言类型我们练习Veirlog

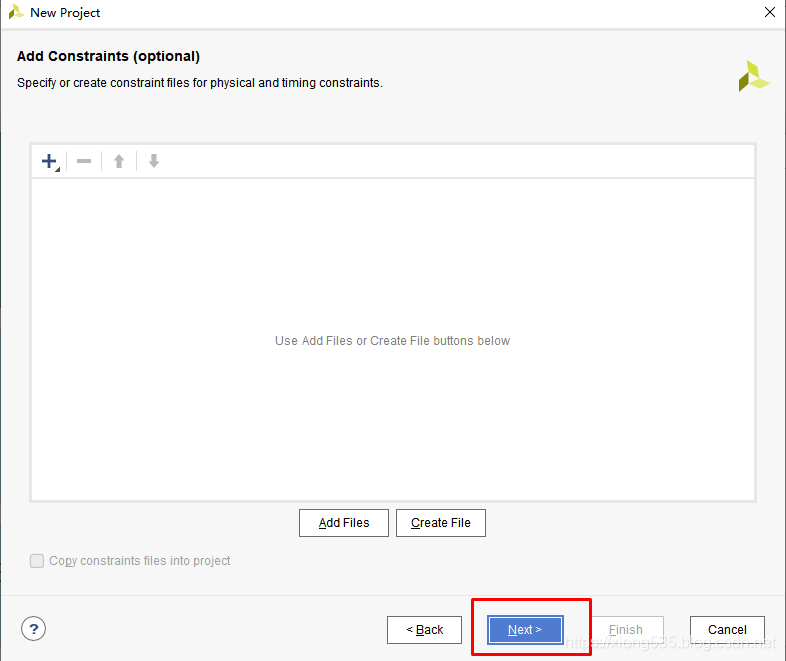

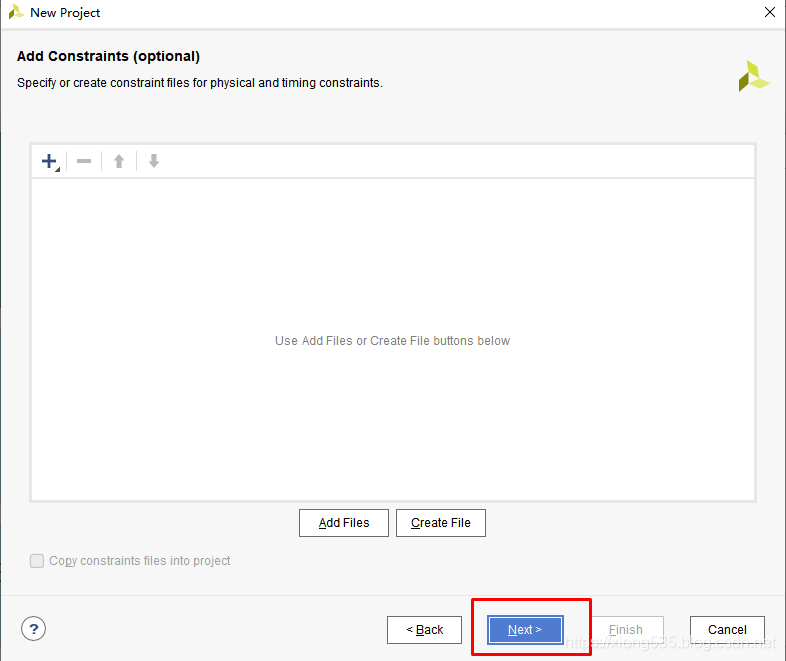

- constraits稍后添加,next

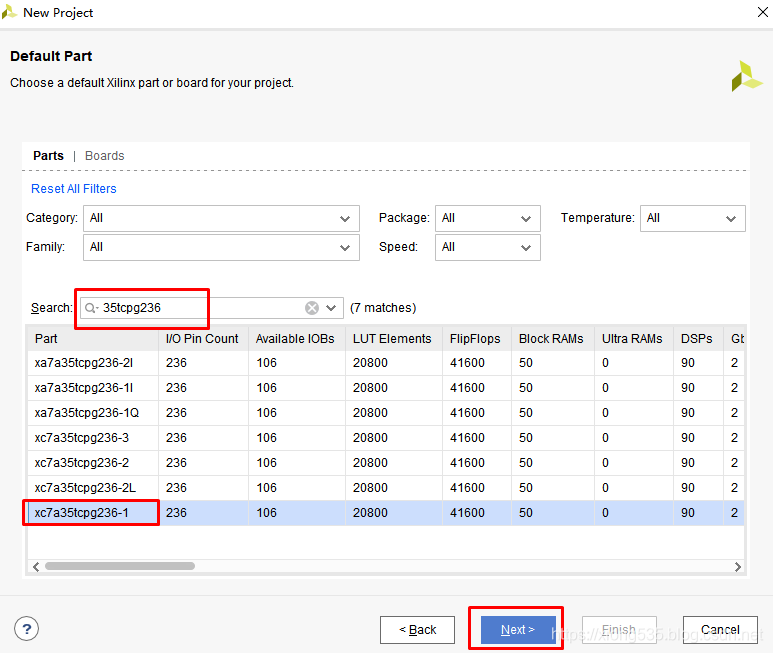

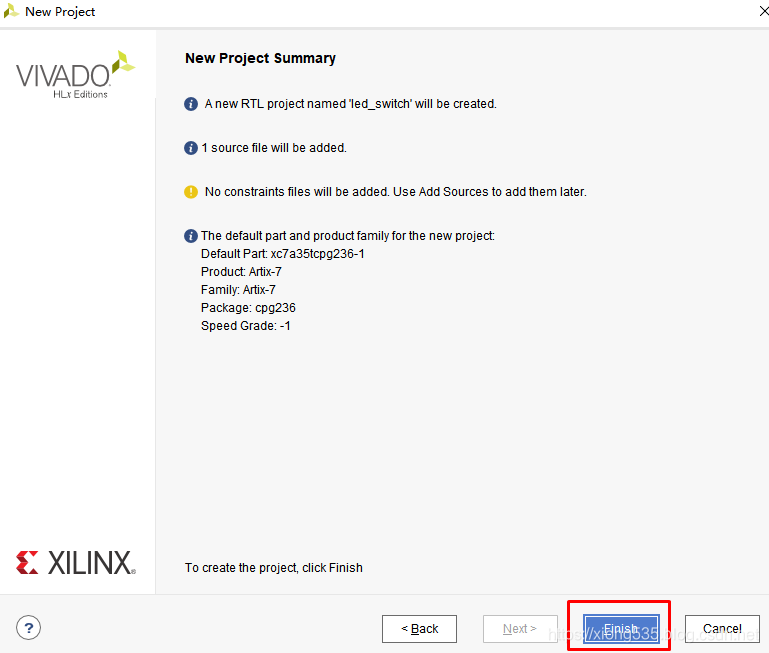

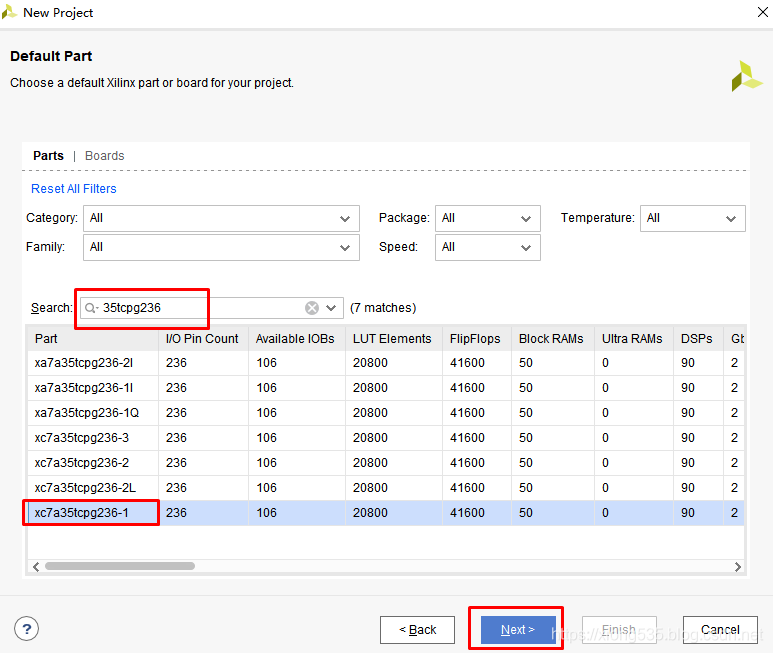

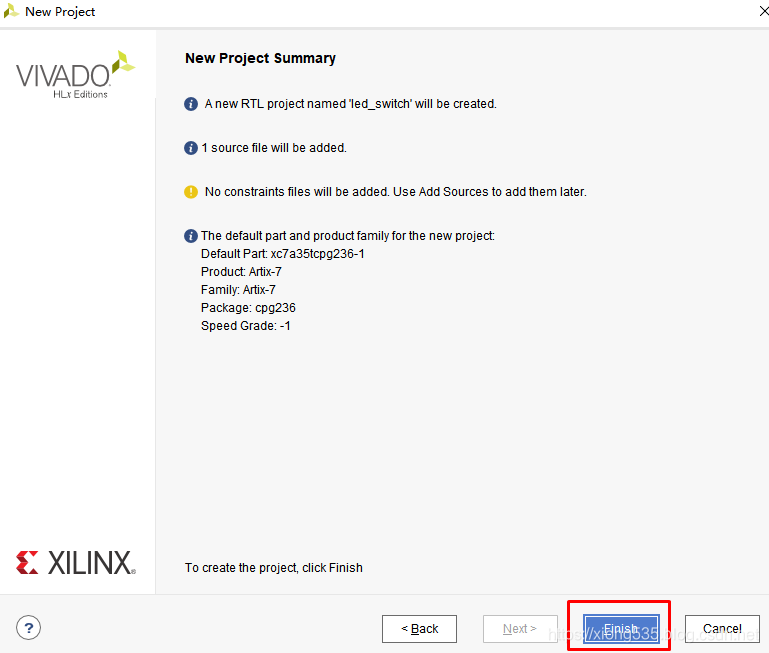

- 在搜索框搜索,选择器件,next

- 在搜索框搜索,选择器件,next

- 可以看到界面是很好看的

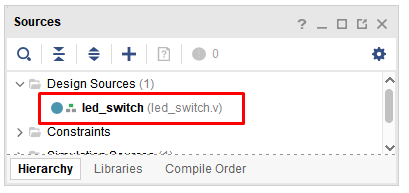

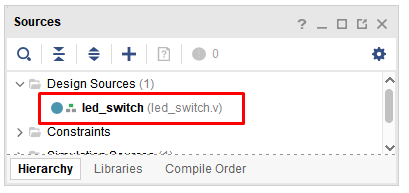

- 双击打开

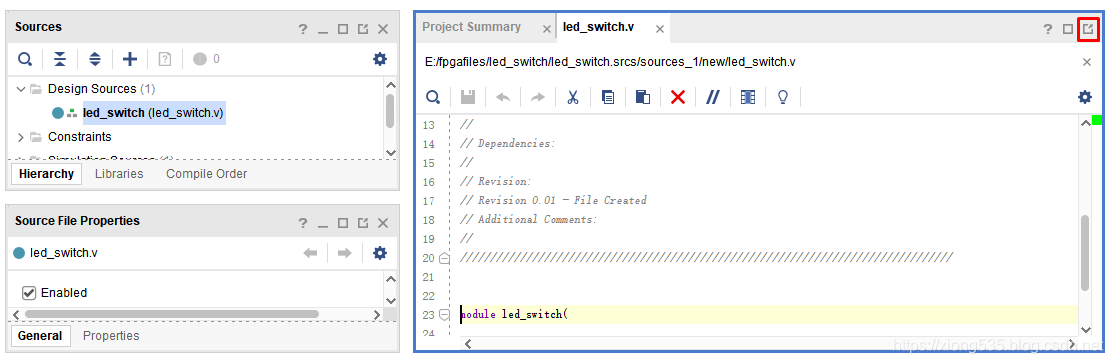

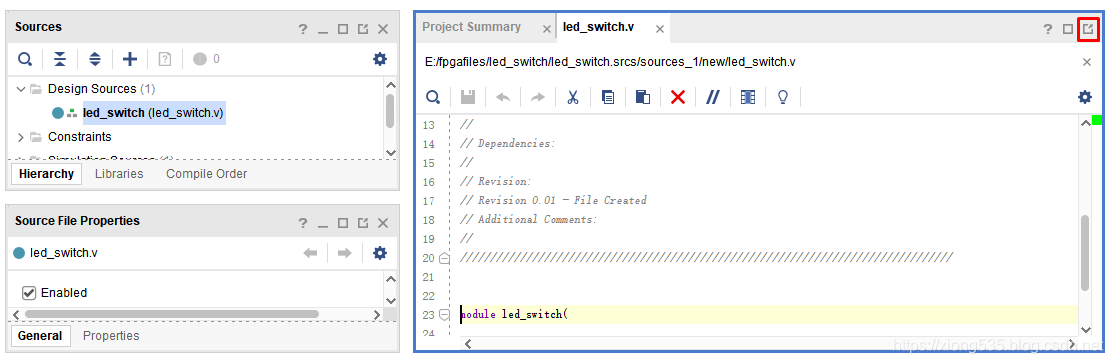

- 觉得界面太小也可以选择让窗口悬浮

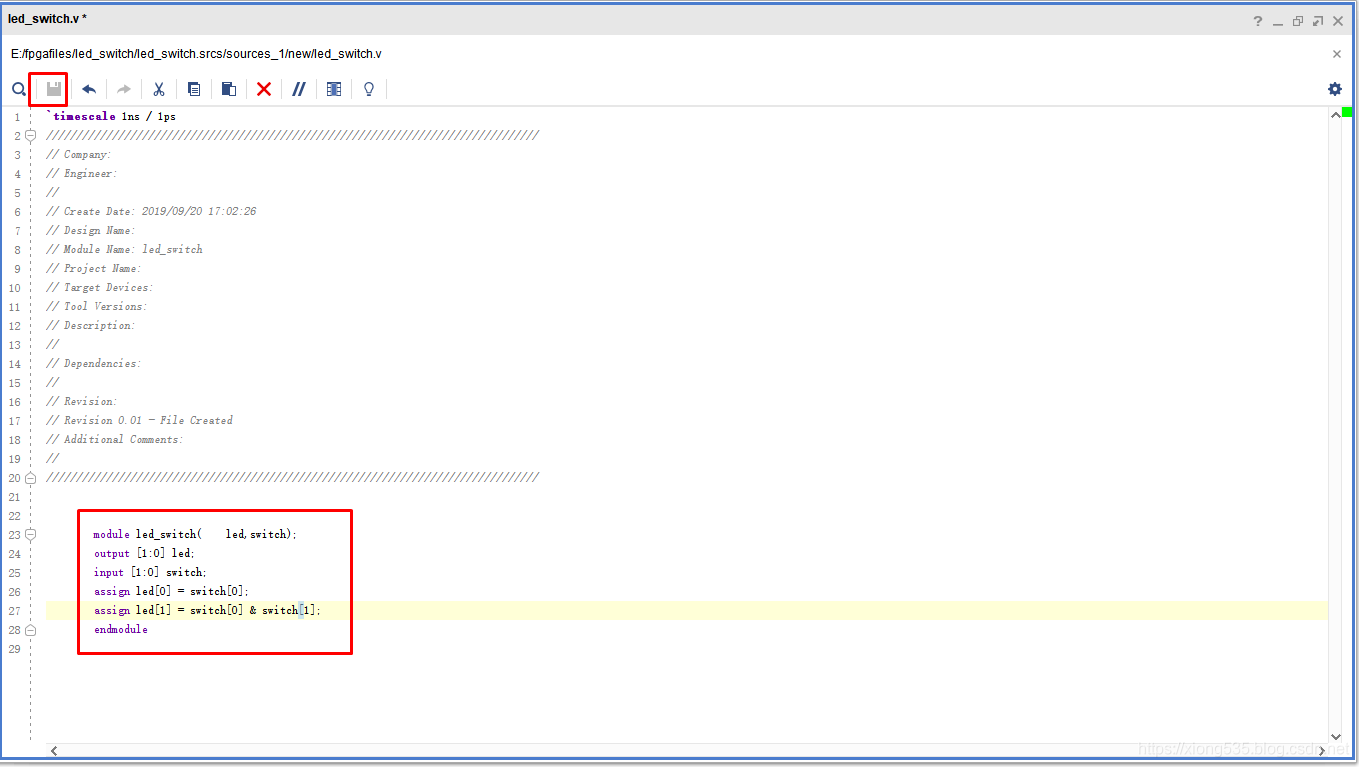

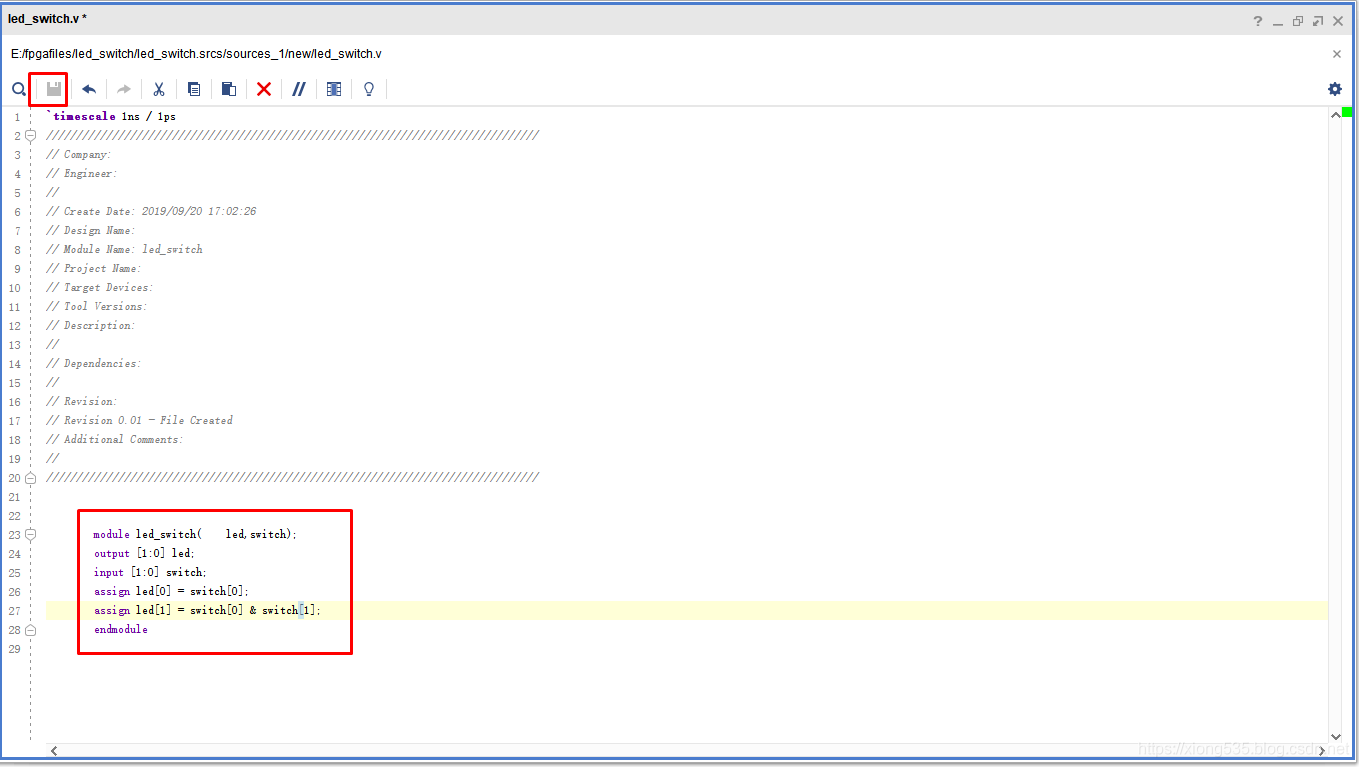

- 写代码,保存

module led_switch(led,switch);

output [1:0] led;

input [1:0] switch;

assign led[0] = switch[0];

assign led[1] = switch[0] & switch[1];

endmodule

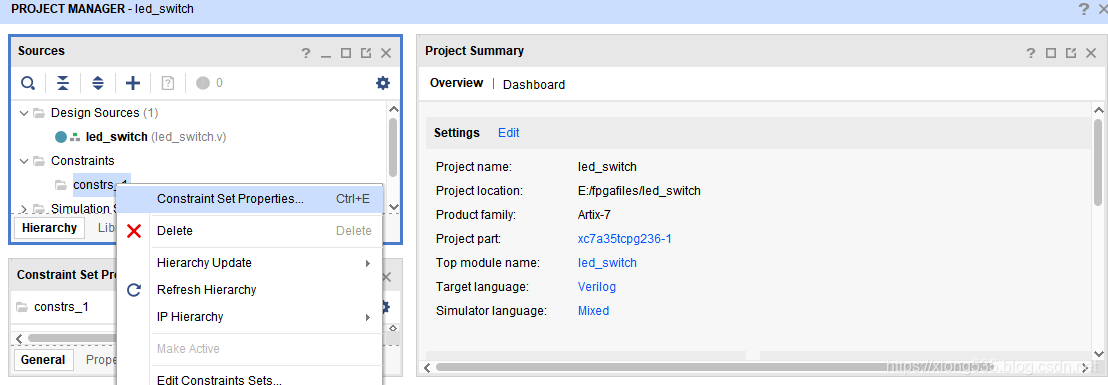

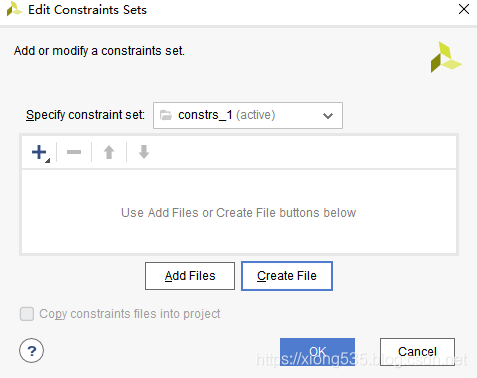

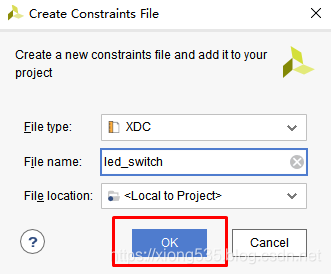

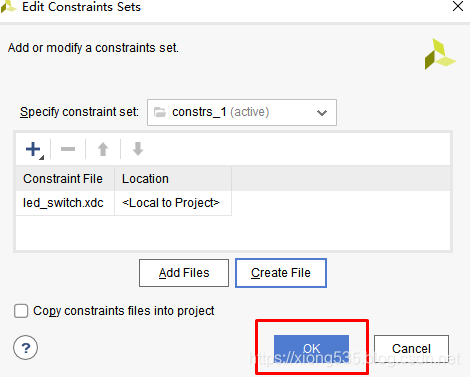

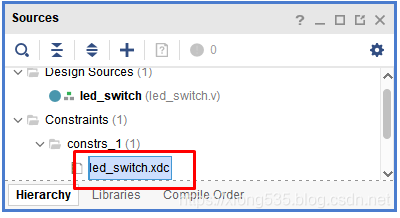

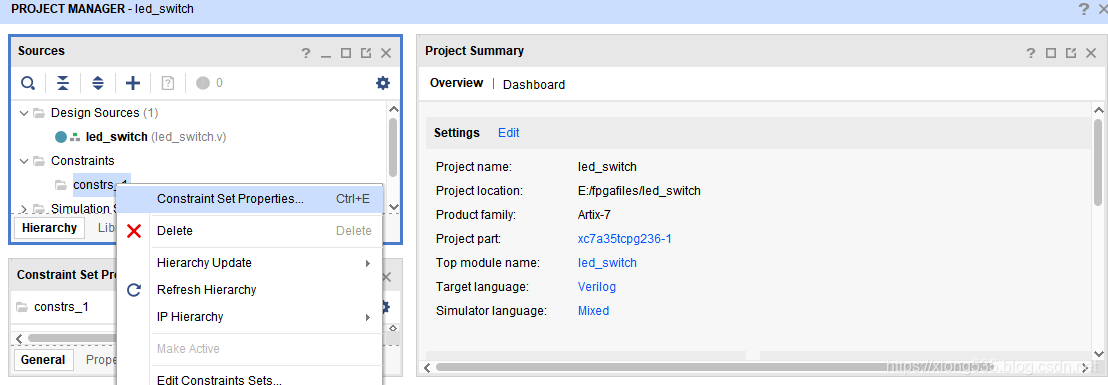

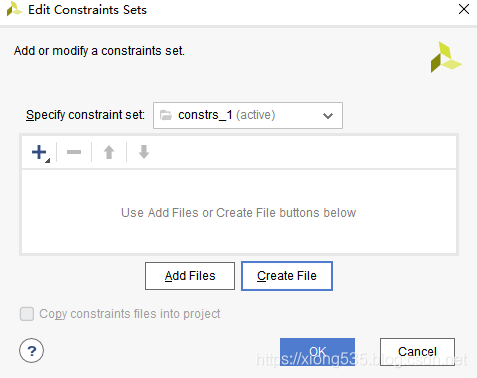

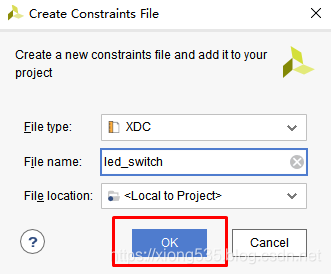

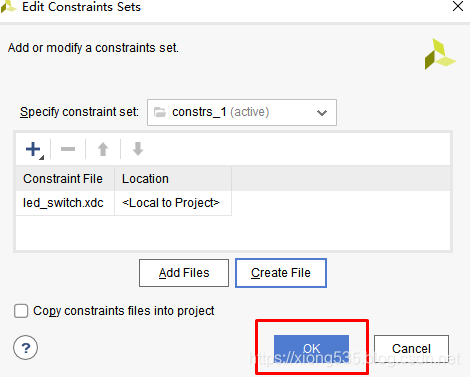

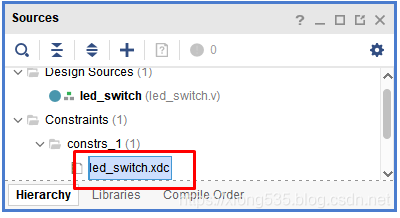

- 然后添加约束,对应到板子上的硬件

- 生成后,双击打开

- 添加约束,对应空格,注意管脚名称与板子上对应

set_property PACKAGE_PIN V17 [get_ports {switch[0]}] // switch[0]加括号{}因为switch[0]是数组

set_property IOSTANDARD LVCMOS33 [get_ports {switch[0]}] // LVCMOS代表CMOS3.3V电压

set_property PACKAGE_PIN V16 [get_ports {switch[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {switch[1]}]

set_property PACKAGE_PIN U16 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property PACKAGE_PIN E19 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

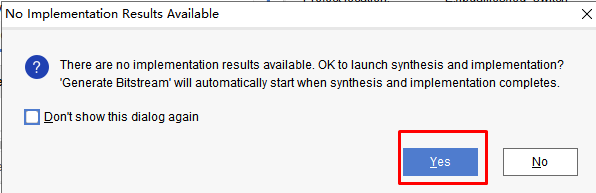

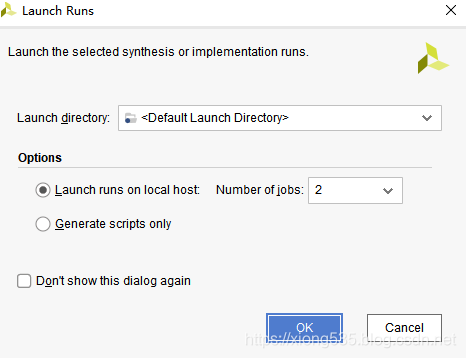

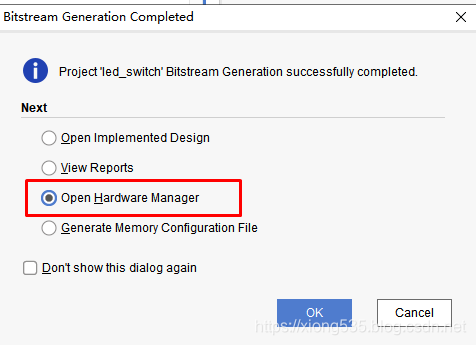

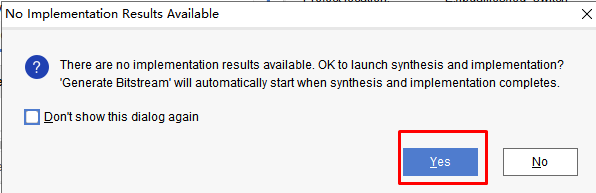

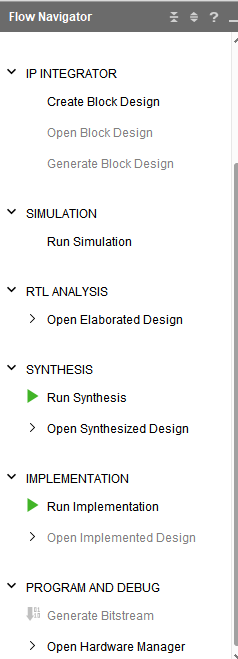

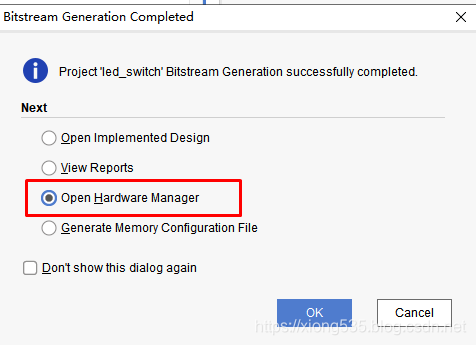

- 产生bitstream这是要写入板子的bit文件

- OK完事

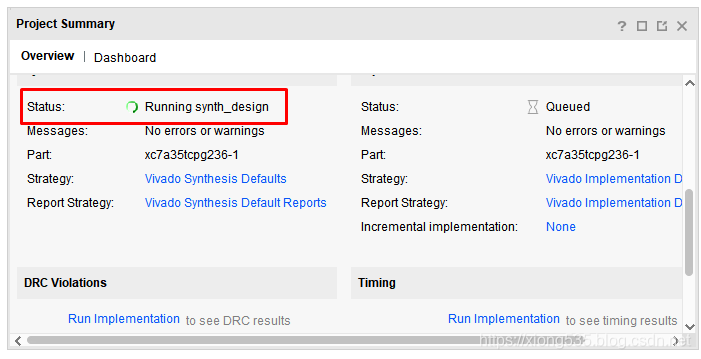

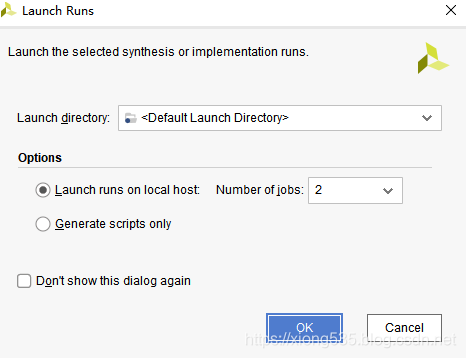

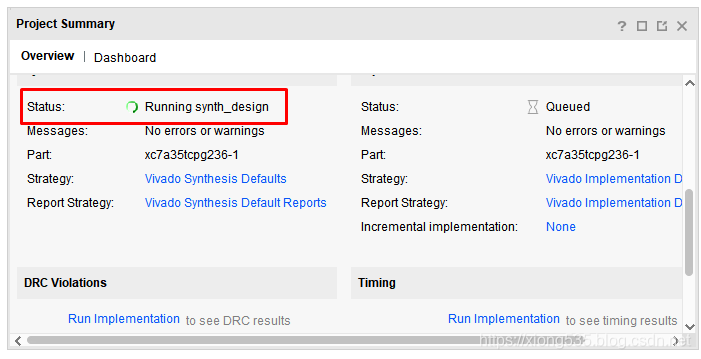

- 开始运转,速度非常慢,不得不忍受,要是报错得重新回去调试

- 他实际上按这个流程跑下来

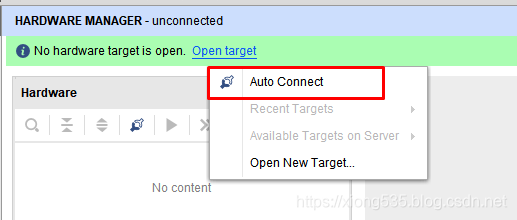

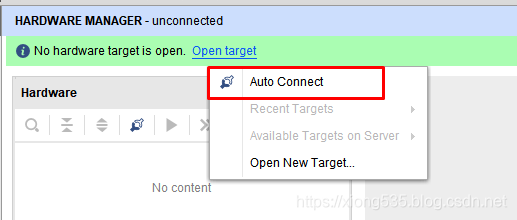

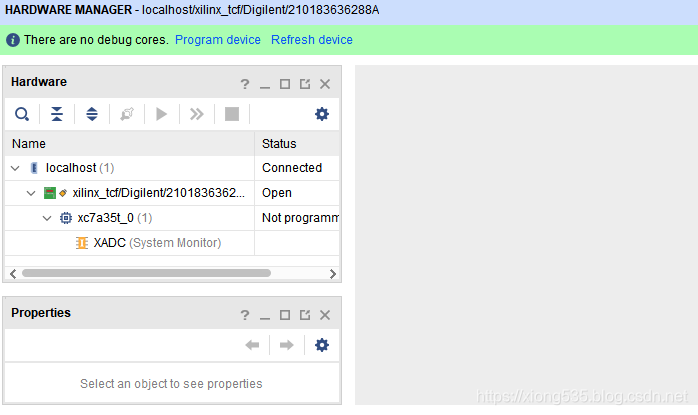

- 打开硬件管理器

- 没什么显示,别慌

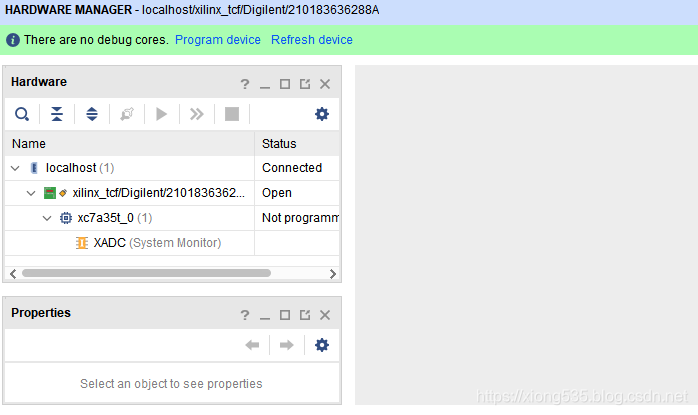

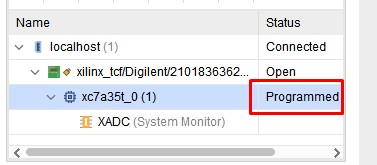

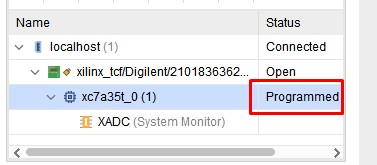

- 看板子已经连接上了,点绿条里的Program device

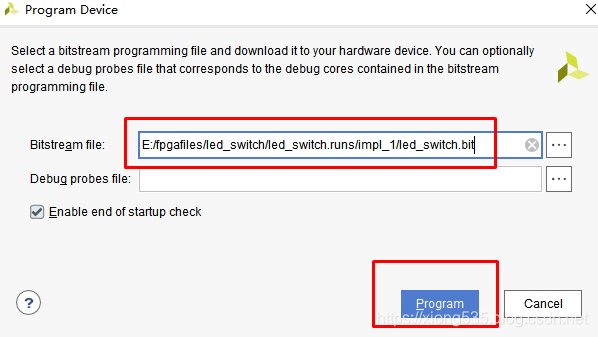

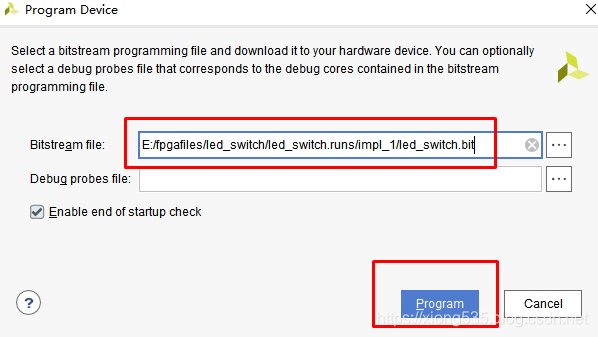

- 一般文件夹的位置在这,有的同学不是就得手动找

- 如果没有programmed得手动选择

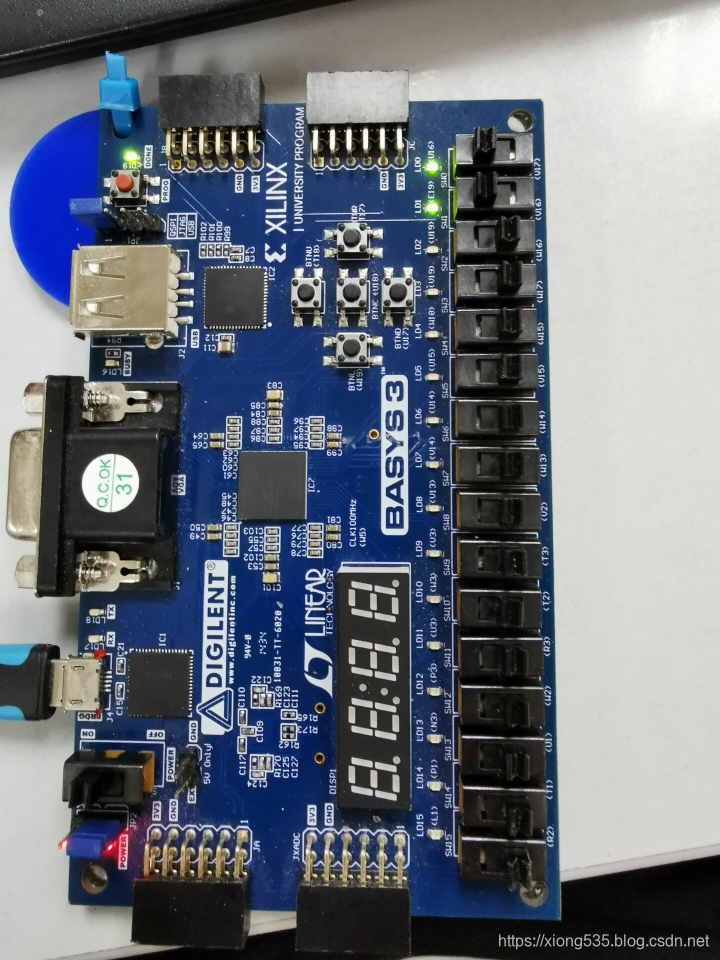

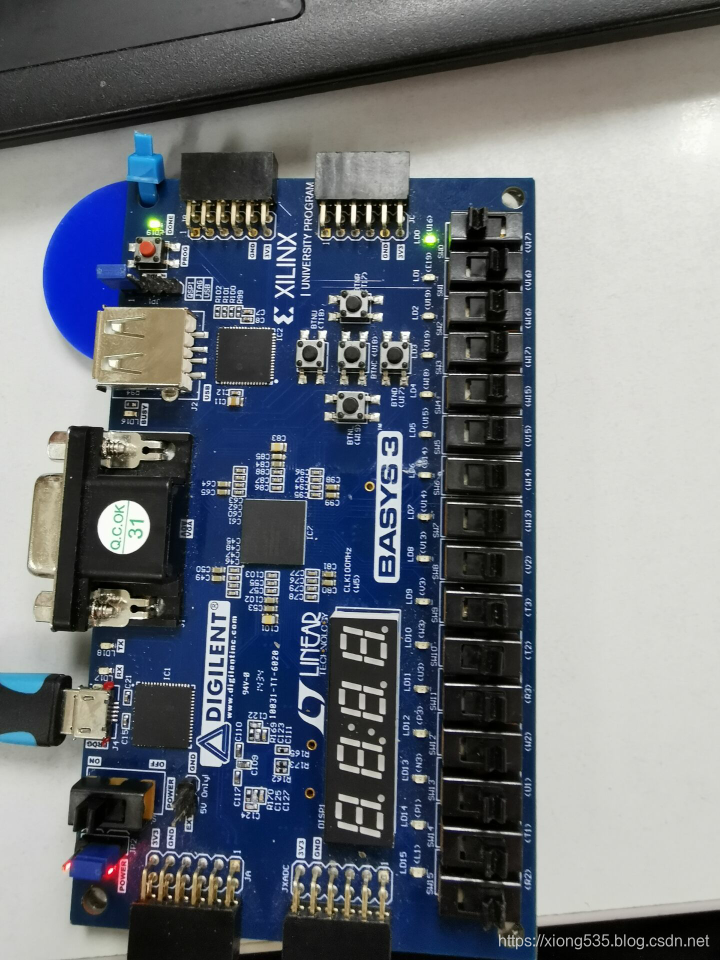

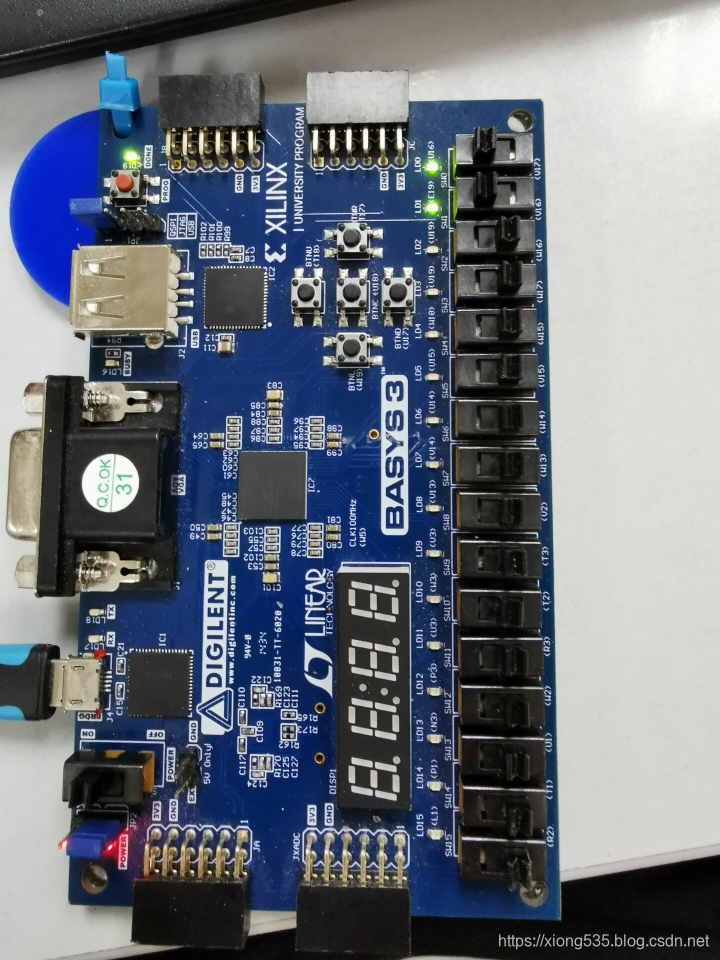

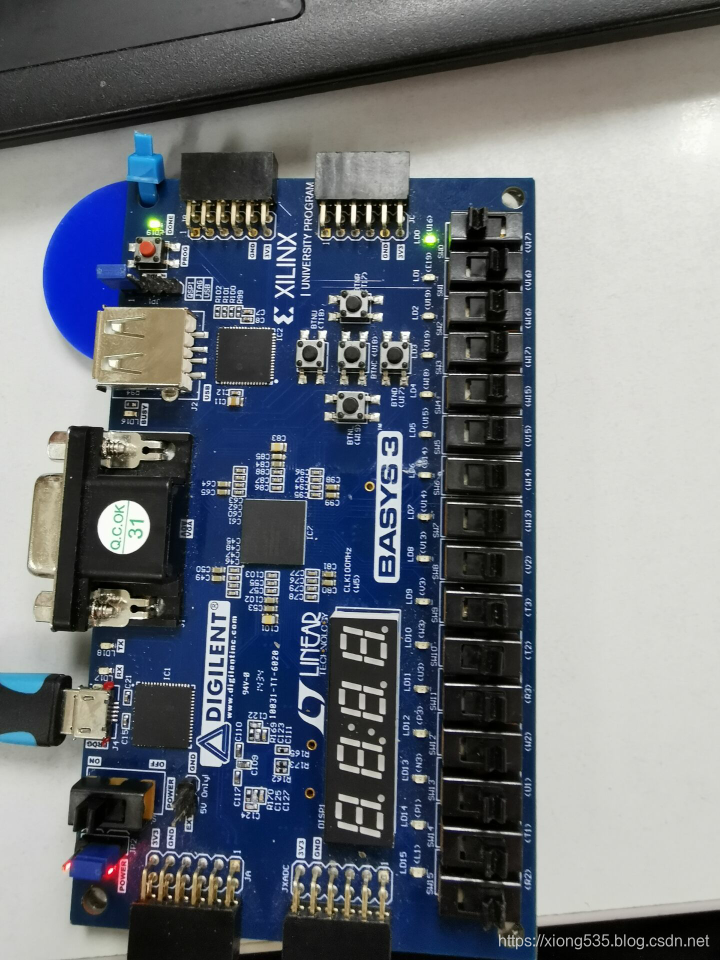

- 实验结果

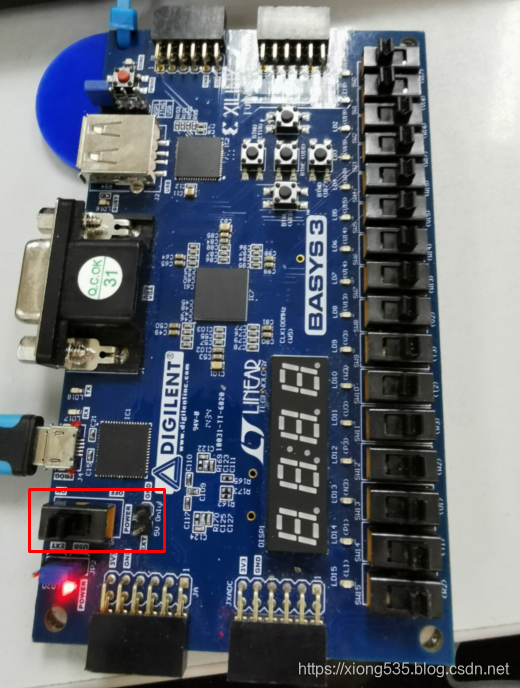

- 讲个笑话,一开始我连开机都不知道,得摁开关

- 在搜索框搜索,选择器件,next

- 在搜索框搜索,选择器件,next

2495

2495

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?