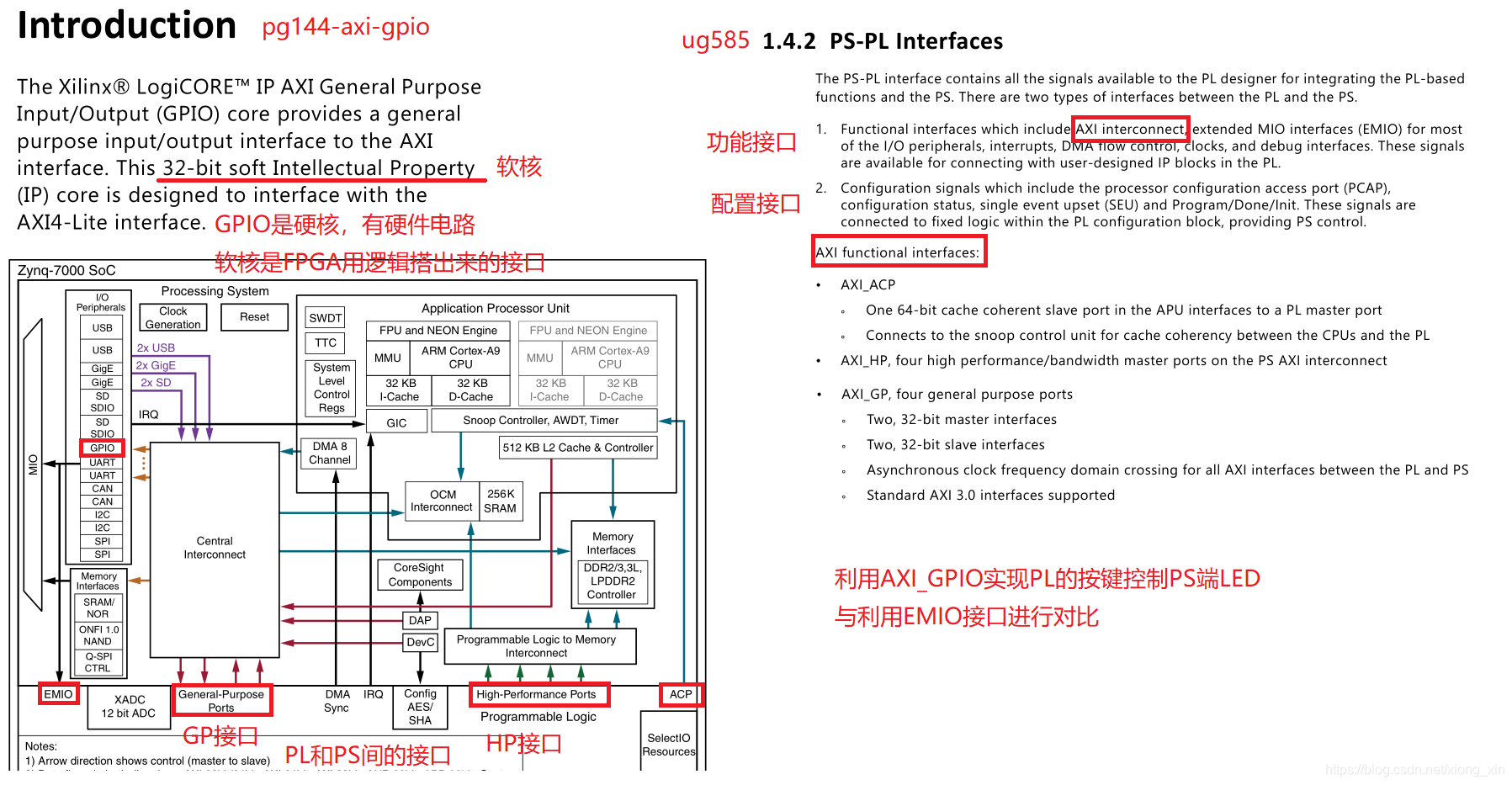

- 在pg144-axi-gpio(LogiCORE IP Product Guide)中可以看见AXI GPIO提供通用输入输出接口到AXI接口,32位软核,设计与AXI4-Lite接口进行连接。IOP中GPIO是硬核,芯片中已经实现的硬件电路,AXI GPIO是在PL端用逻辑实现的软核。在ug585的1.4.2 PS-PL interfaces中介绍了两种接口,功能接口和配置接口。AXI互联属于功能接口,功能接口又分AXI_ACP,AXI_HP和AXI_GP。在框图中均可以看见,实现了PL和PS间数据传输。

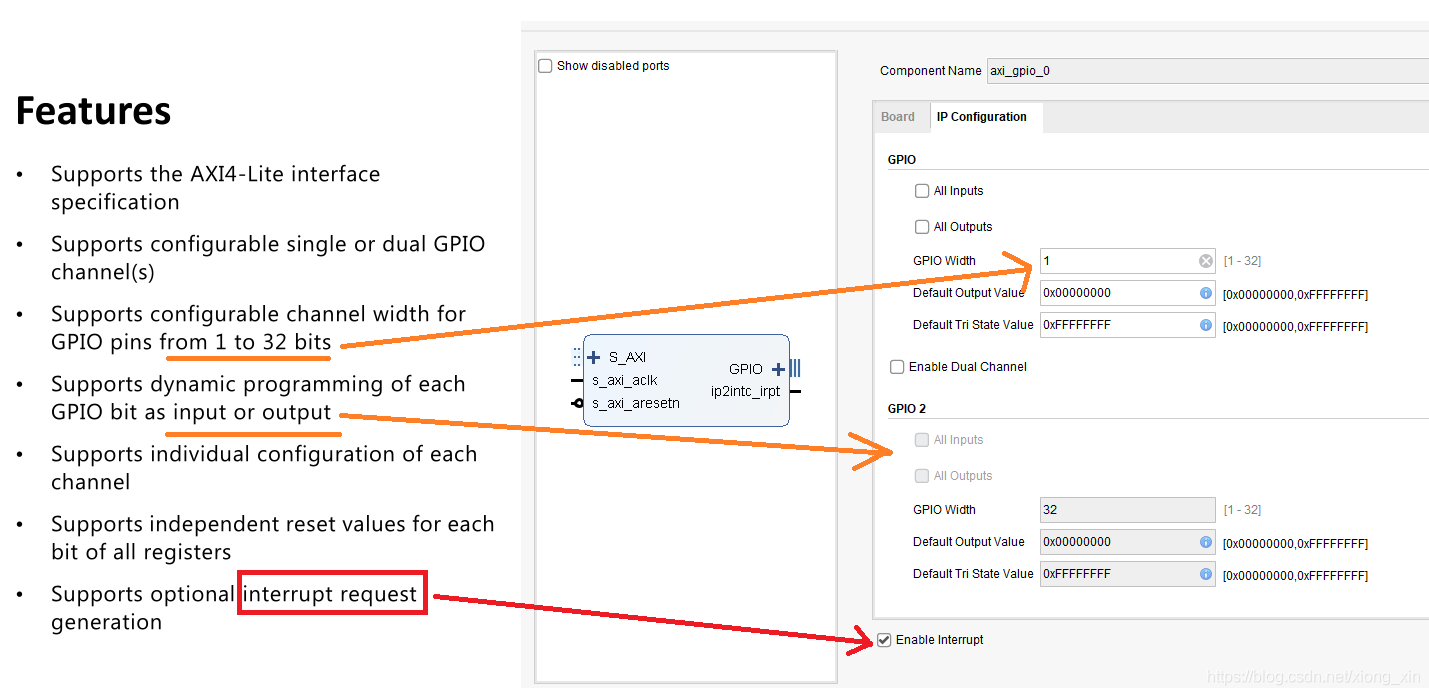

- 特性

- 支持AXI4-Lite接口

- 支持配置成单通道或双通道(配置界面两个通道选择)

- 配置通道位宽从1位到32位

- 针对GPIO每一位支持动态编程为输入或输出

- 支持每个通道的独立配置

- 复位信号

- 可选中断请求信号的生成(在Vivado下勾选Enable Interrupt)

- 功能描述

- AXI GPIO提供了一个通用的输入输出接口到AXI4-Lite接口。可以配置成单通道或双通道。每个通道可以独立进行配置。

- GPIO端口可以动态配置输入或输出通过使能或者关闭使能三态的缓冲器。每个通道可以配置成当一个转化(电平状态改变从0到1或从1到0)在输入引脚发生时产生中断信号。

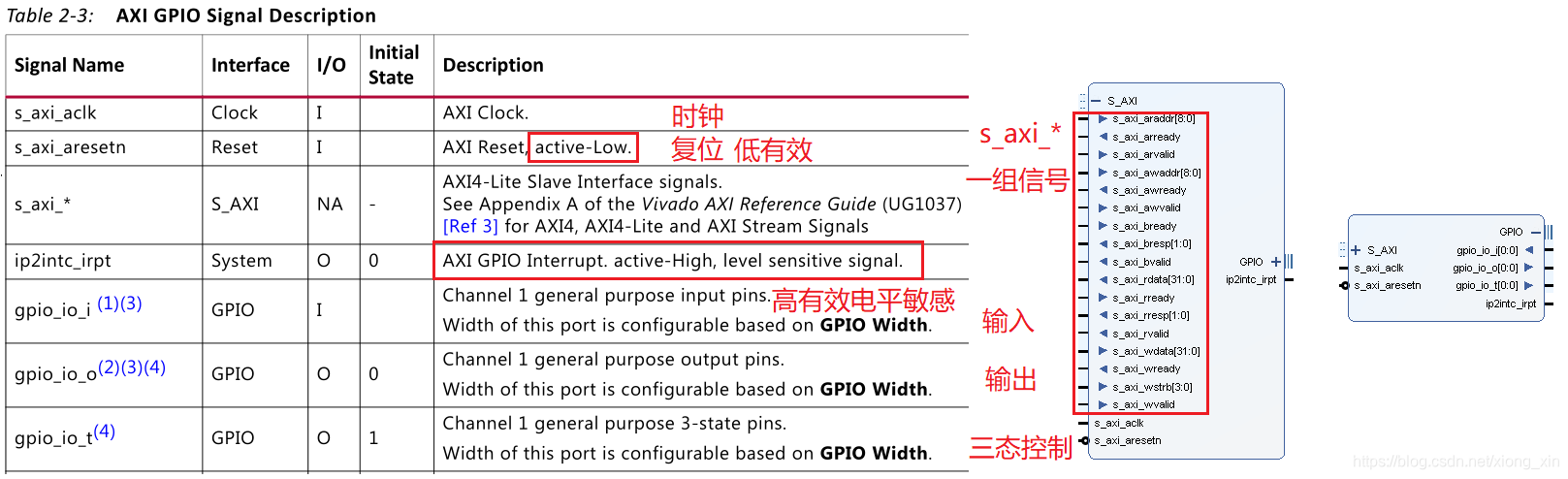

The AXI GPIO design provides a general purpose input/output interface to an AXI4-Lite interface. The AXI GPIO can be configured as either a single or a dual-channel device. The width of each channel is independently configurable.

The ports are configured dynamically for input or output by enabling or disabling the 3-state buffer. The channels can be configured to generate an interrupt when a transition on any of their inputs occurs.

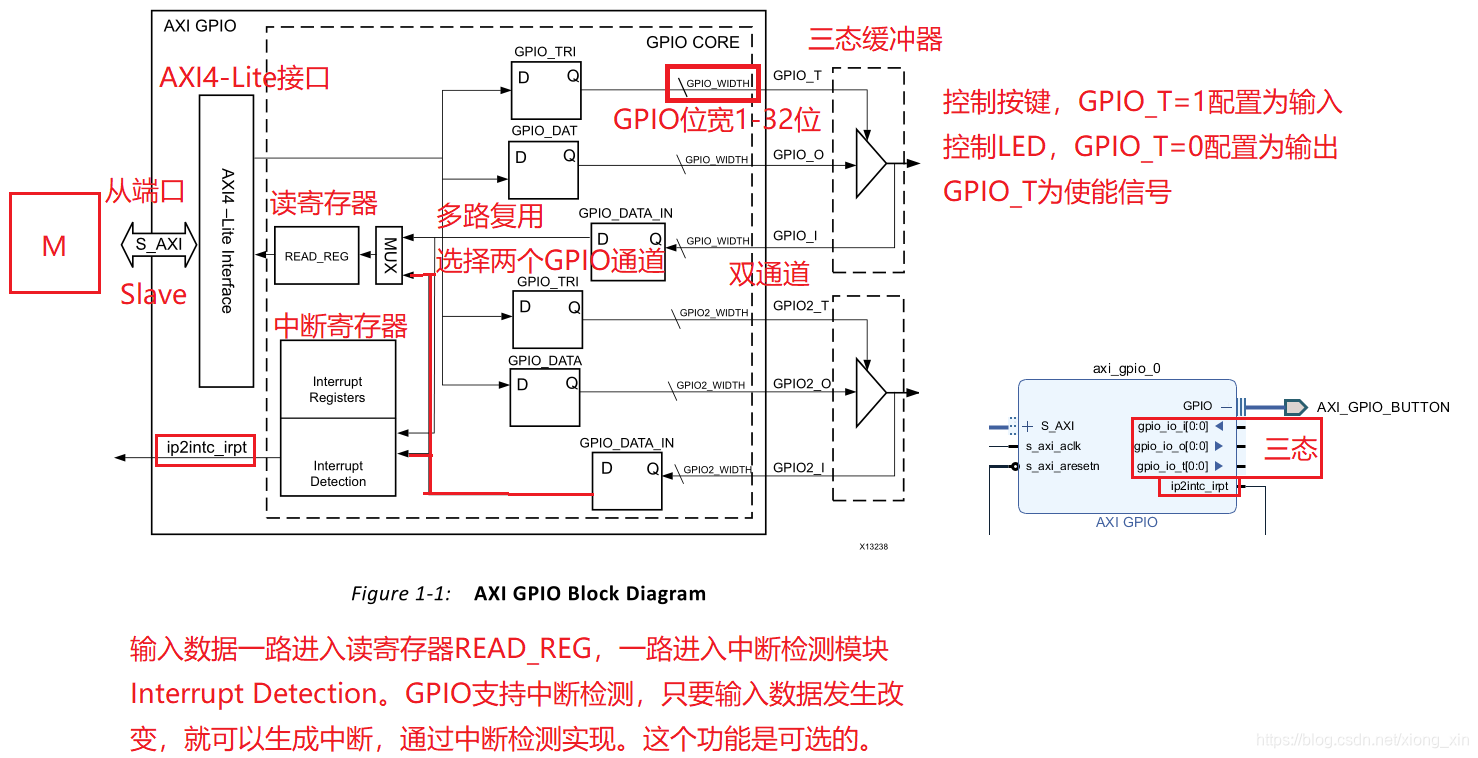

- AXI GPIO内核的顶层框图如图所示。(The top-level block diagram of AXI GPIO core is shown in Figure 1-1.)

- S_AXI中S代表slave是从端口,处理器作为Master可以控制AXI GPIO这个从器件。AXI4-Lite作为轻量级的接口可以实现简单寄存器的配置和少量的数据传输。READ_REG是读寄存器,Interrupt Registers是中断寄存器,AXI4-Lite可以实现对这两个寄存器的配置。三态缓冲器不包含在AXI GPIO里,是工具在顶层文件里自动添加的。GPIO分为两个独立的通道GPIO_T和GPIO_T。通过控制GPIO_T可以动态配置输入和输出,GPIO_T是三态的使能信号。GPIO_T=1配置为输入(in),GPIO_T=0配置为输出(out)。GPIO_WIDTH是用户指定的位宽,可以配置在1位到32位之间。

- 输入数据一方面进入READ_REG,一方面进入中断检测模块Interrupt Detection。只要输入端口数据发生改变就可以生成中断,中断检测实现该功能并通过ip2intc_irpt输出一个中断。

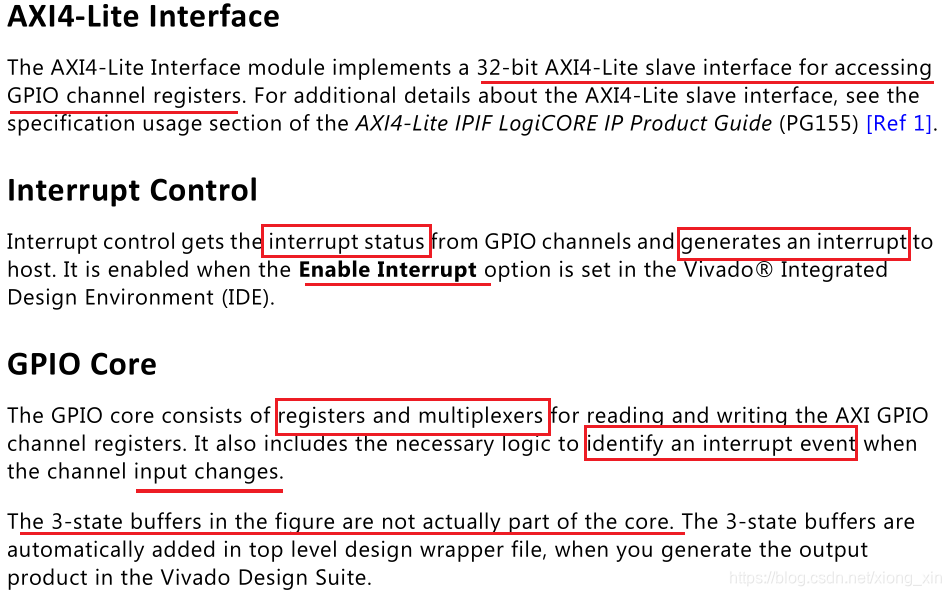

- AXI4-Lite接口

- AXI4-Lite接口模块实现32位AXI4-Lite从接口,用于访问GPIO通道寄存器。(AXI4-Lite是一种简单协议用来读写模块内的寄存器)

- 中断控制

- 从GPIO通道获取中断状态,并向主机生成中断。通过选择使能中断选项时,将启用该选项。

- GPIO核心

- GPIO内核包含寄存器(输入输出和中断)和多路复用器(选择两个GPIO的通道),用于读取和写入AXI GPIO通道寄存器。当通道输入数据改变时可以检测中断事件。

- 图中3态缓冲区实际上不是GPIO核心的一部分。在Vivado中生成输出结果时,3状态缓冲区会自动添加到顶层模块中。

- 端口描述(Port Descriptions)

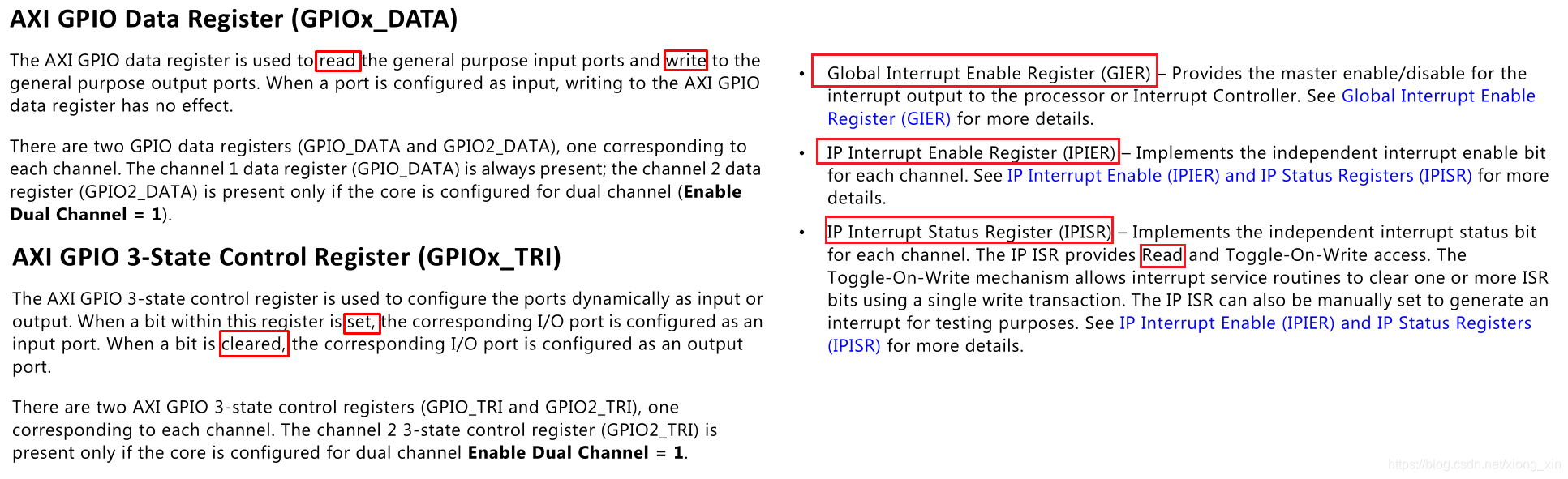

- 寄存器空间(Register Space)

- GPIO_DATA是数据寄存器(Data Register),读数据和写数据都是通过这个寄存器。

- GPIO_TRI是三态控制寄存器,控制GPIO引脚作为输入还是输出

- GIER是全局使能中断寄存器(Global Interrupt Enable Register)的缩写。(总开关控制全局使能信号,总开关打开以后内部两个通道的中断信号才有肯可能使能,具体通道的使能通过子开关IP IER实现)

- IP IER,打开某一个通道的中断功能

- IP ISR,通道状态寄存器

- GPIO_DATA可以读和写端口即读用作输入,写用作输出

- GPIO_TRI被置为1时,用作输入;被清除为0时用作输出

- set 1 in

- clear 0 out

- GIER打开全局中断

- IP IER打开各通道独立的中断

- IP ISR状态寄存器可以读取当前中断状态

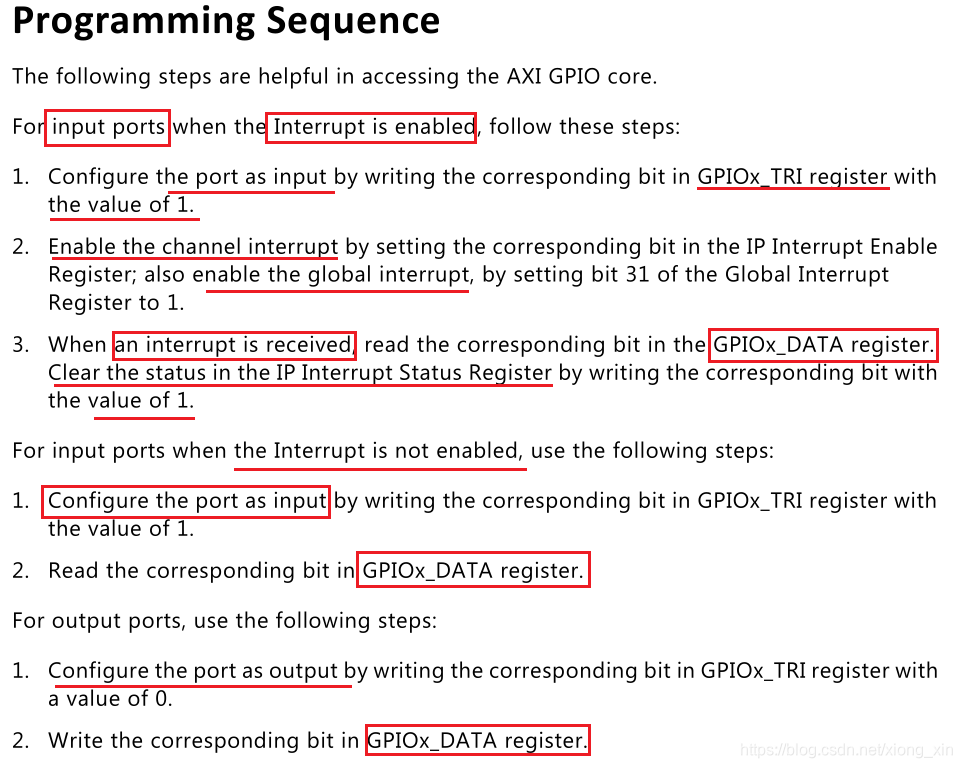

- 编程指导(ch3 Programming Sequence)

- 作为输入打开中断(大概意思没有逐字翻译)

- 把三态控制寄存器GPIO_TRI写1配置成输入

- 打开通道的中断,同时打开全局中断

- 当接受到中断时(说明输入引脚电平发生变化),从GPIO_DATA读取输入数据,对应位写1清除中断状态寄存器IP ISR(清除中断状态方便检测下次中断的产生)

- 不使用中断作为输入

- 配置成输入

- 从GPIO_DATA读数据

- 输出

- 把端口配置成输出

- 往端口写数据

563

563

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?