现象描述:

- 可以使用vivado 烧录整个flash,无任何报错。

- 修改fsbl打开调试日志开关,切换到qspi启动模式,上电无法启动,串口也无任何打印消息。

- 通过vitis调试工具直接将uboot载入内存中运行无任何问题,sf probe 也能读取到flash型号”SF: Detected mx25l12805d with page size 256 Bytes, erase size 64 KiB, total 16 MiB“

- 使用vitis调试fsbl也能正常输出日志

综上所述:开始怀疑是兆易创新 GigaDevice 的FLASH(GD25Q128)不兼容MPSOC,但更换旺宏(MX25L128) 效果依然依旧。在fsbl中打开调试日志开关,系统切换到qspi模式依然无任何输出,因此怀疑是bootrom未能成功读取FLASH中的数据至OCM中,导致fsbl调试信息都没输出。

通过jtag调试实锤:

- 查看(ug1085-zynq-ultrascale-trm.pdf)第251页,关于”CSU BootROM Error Codes“相关描述;确定可以通过”CSU_BR_ERR“寄存器,读取到BootROM启动报错的相关信息。

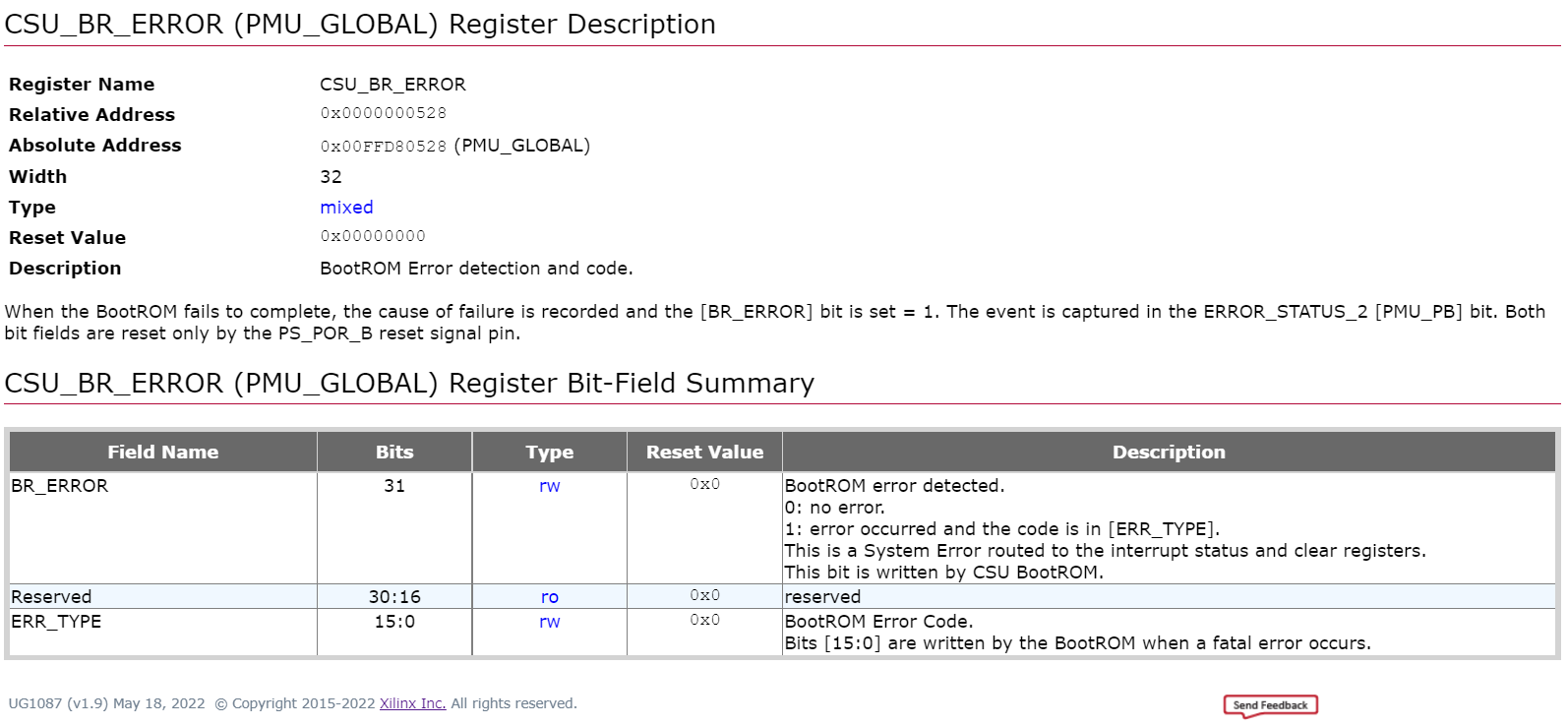

- 查看寄存器手册:”Zynq UltraScale+ Devices Register Reference(UG1087)“

- 可以知道"0x00FFD80528"为”CSU_BR_ERR“寄存器地址。Bits [15:0]为BootROM Error Code.

- 通过连接jtag到单板,使用xsct.bat连接;读取相应寄存器值(0x80002400)。

xsct% connect

tcfchan#0

xsct% source D:/Xilinx/Vitis/2022.2/scripts/vitis/util/zynqmp_utils.tcl

xsct% targets

1 PS TAP

2 PMU

3 PL

4 xcku5p

5 PSU

6 RPU (Reset)

7 Cortex-R5 #0 (RPU Reset)

8 Cortex-R5 #1 (RPU Reset)

9 APU (L2 Cache Reset)

10 Cortex-A53 #0 (APU Reset)

11 Cortex-A53 #1 (APU Reset)

12 Cortex-A53 #2 (APU Reset)

13 Cortex-A53 #3 (APU Reset)

xsct% targets -set -nocase -filter {name =~ "*A53*#0"}

xsct% rst -processor

Info: Cortex-A53 #0 (target 10) Stopped at 0xffff0000 (Reset Catch)

xsct% mrd 0x00FFD80528

FFD80528: 80002400

xsct%

- 可以看到bit 31 位被置位,表明BootRom启动遇到了错误;BootROM Error Code为0x2400.

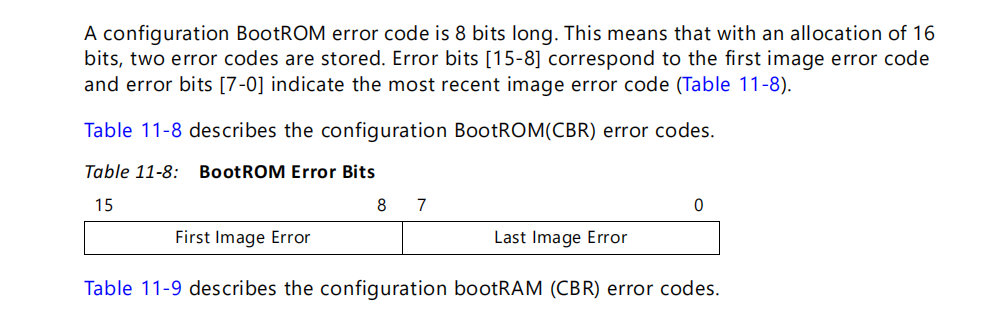

- 通过Table 11‐8: BootROM Error Bits 可知,First Image Error 为0x24.

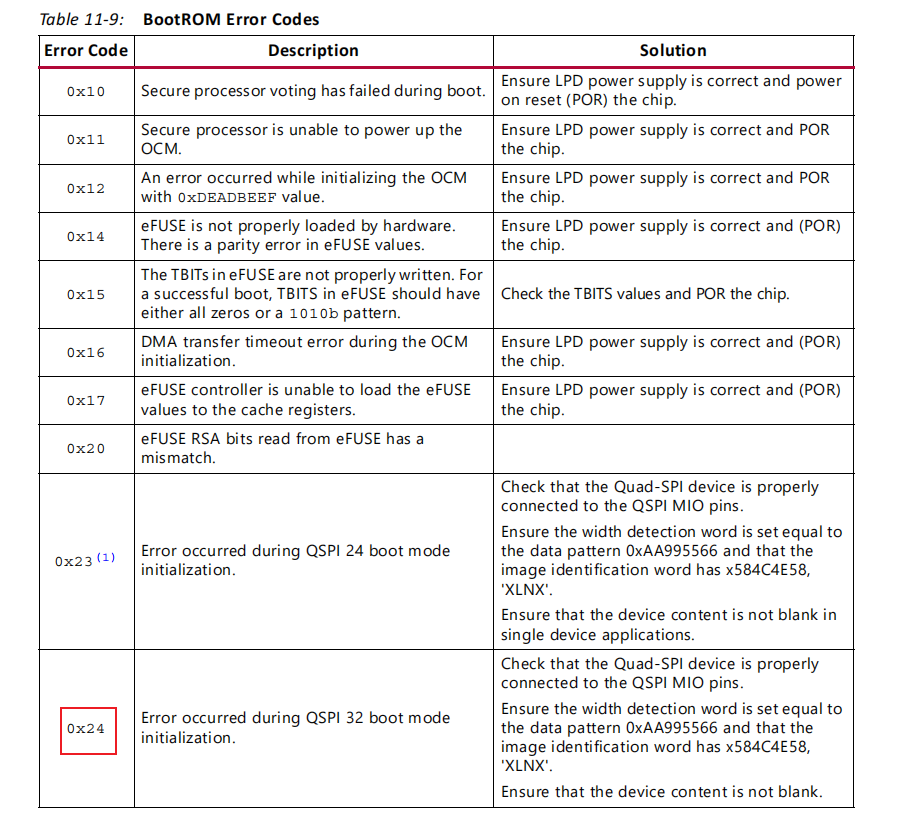

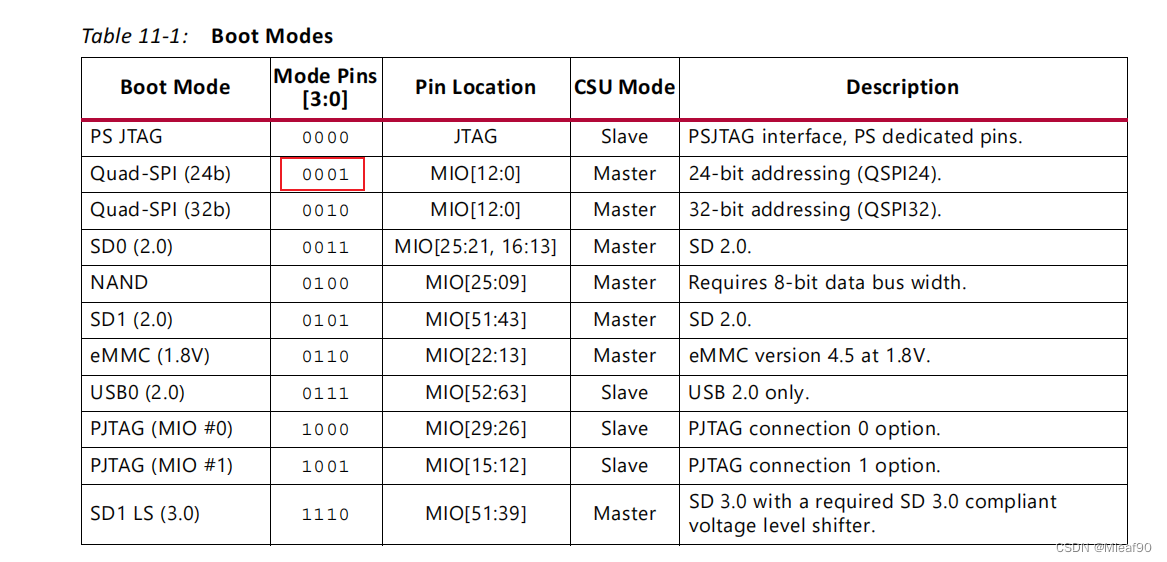

- 查表可知0x24对应的是(Error occurred during QSPI 32 boot mode initialization.)

问题总结:

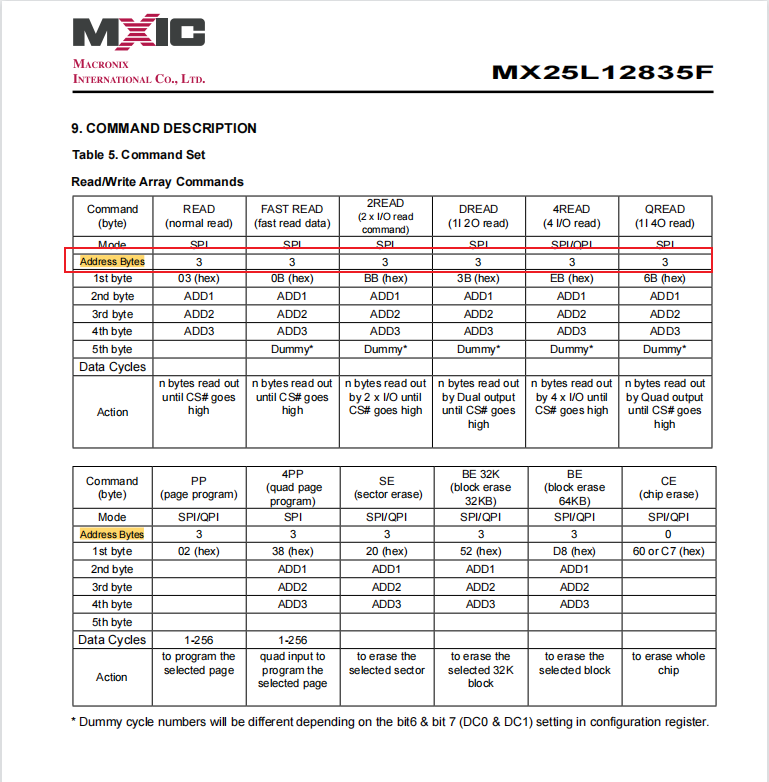

- 因flash(MX25L12835F)读写不支持Quad-SPI (32b)模式,导致使用Quad-SPI (32b)模式下,BootROM无法读取到数据,导致启动失败。

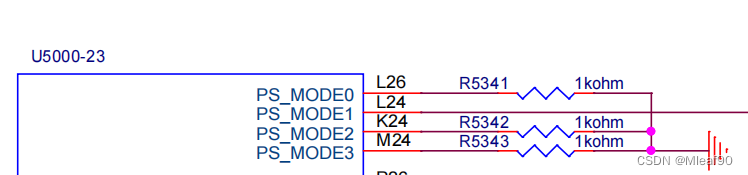

- 硬件默认设计的时候只预留了Quad-SPI (32b)模式。

最终解决:

-

修改zynqmp启动模式为Quad-SPI (24b),修改Mode Pins[3:0]引脚的电平分别为0001(因硬件默认将PS_MODE0通过1k电阻接地了,当然只能飞线了),上电后成功启动。

-

可以看到fsbl打印消息”QSPI 24bit Boot Mode “。

-

至此完美解决问题。

Xilinx Zynq MP First Stage Boot Loader

Release 2021.2 Oct 13 2021 - 07:15:53

MultiBootOffset: 0x0

Reset Mode : System Reset

Platform: Silicon (4.0), Cluster ID 0x80000000

Running on A53-0 (64-bit) Processor, Device Name: XCZU15EG

Processor Initialization Done

================= In Stage 2 ============

QSPI 24bit Boot Mode

QSPI is in single flash connection

QSPI is using 4 bit bus

FlashID=0xC2 0x20 0x18

MACRONIX 128M Bits

Multiboot Reg : 0x0

QSPI Reading Src 0x0, Dest FFFF0040, Length EC0

.QSPI Read Src 0x0, Dest FFFF0040, Length EC0

Image Header Table Offset 0x8C0

QSPI Reading Src 0x8C0, Dest FFFDA0A8, Length 40

.QSPI Read Src 0x8C0, Dest FFFDA0A8, Length 40

*****Image Header Table Details********

Boot Gen Ver: 0x1020000

No of Partitions: 0x5

Partition Header Address: 0x440

Partition Present Device: 0x0

QSPI Reading Src 0x1100, Dest FFFDA0E8, Length 40

.QSPI Read Src 0x1100, Dest FFFDA0E8, Length 40

QSPI Reading Src 0x1140, Dest FFFDA128, Length 40

.QSPI Read Src 0x1140, Dest FFFDA128, Length 40

QSPI Reading Src 0x1180, Dest FFFDA168, Length 40

.QSPI Read Src 0x1180, Dest FFFDA168, Length 40

QSPI Reading Src 0x11C0, Dest FFFDA1A8, Length 40

.QSPI Read Src 0x11C0, Dest FFFDA1A8, Length 40

QSPI Reading Src 0x1200, Dest FFFDA1E8, Length 40

.QSPI Read Src 0x1200, Dest FFFDA1E8, Length 40

Initialization Success

======= In Stage 3, Partition No:1 =======

UnEncrypted data Length: 0x31E8

Data word offset: 0x31E8

Total Data word length: 0x31E8

Destination Load Address: 0xFFFEA000

Execution Address: 0xFFFEA000

Data word offset: 0xF540

Partition Attributes: 0x117

QSPI Reading Src 0x3D500, Dest FFFEA000, Length C7A0

.QSPI Read Src 0x3D500, Dest FFFEA000, Length C7A0

Partition 1 Load Success

======= In Stage 3, Partition No:2 =======

UnEncrypted data Length: 0x37F99

Data word offset: 0x37F99

Total Data word length: 0x37F99

Destination Load Address: 0x8000000

Execution Address: 0x8000000

Data word offset: 0x12730

Partition Attributes: 0x114

QSPI Reading Src 0x49CC0, Dest 8000000, Length DFE64

.QSPI Read Src 0x49CC0, Dest 8000000, Length DFE64

Partition 2 Load Success

======= In Stage 3, Partition No:3 =======

UnEncrypted data Length: 0x8000

Data word offset: 0x8000

Total Data word length: 0x8000

Destination Load Address: 0x0

Execution Address: 0x0

Data word offset: 0x80000

Partition Attributes: 0x116

QSPI Reading Src 0x200000, Dest 0, Length 20000

.QSPI Read Src 0x200000, Dest 0, Length 20000

Partition 3 Load Success

======= In Stage 3, Partition No:4 =======

UnEncrypted data Length: 0x118

Data word offset: 0x118

Total Data word length: 0x118

Destination Load Address: 0x0

Execution Address: 0x0

Data word offset: 0x88000

Partition Attributes: 0x116

QSPI Reading Src 0x220000, Dest 0, Length 460

.QSPI Read Src 0x220000, Dest 0, Length 460

Partition 4 Load Success

All Partitions Loaded

================= In Stage 4 ============

PM Init Success

Protection configuration applied

Running ÿNOTICE: BL31: v2.4(release):xlnx_rebase_v2.4_2021.1_update1-23-g9188496b9

NOTICE: BL31: Built : 07:41:24, Oct 13 2021

U-Boot 2021.01 (Jun 20 2022 - 11:02:21 +0000)

CPU: ZynqMP

Silicon: v3

Board: Xilinx ZynqMP

DRAM: 1023 MiB

PMUFW: v1.1

EL Level: EL2

Chip ID: zu67dr

WDT: Started with servicing (60s timeout)

MMC: mmc@ff160000: 0

Loading Environment from SPIFlash... SF: Detected mx25l12805d with page size 256 Bytes, erase size 64 KiB, total 16 MiB

OK

In: serial

Out: serial

Err: serial

Bootmode: QSPI_MODE

Reset reason: EXTERNAL

Net:

ZYNQ GEM: ff0b0000, mdio bus ff0b0000, phyaddr 1, interface sgmii

mii bus: eth0 phy_mask: 2 devad: -1 get_phy_id:0x4f51e91a

Get yt8521S mode: 2, poll or utp

find phy drv name: YT8531S Ethernet

hw_strap_mode: 0x3

Warning: ethernet@ff0b0000 MAC addresses don't match:

Address in DT is 00:0a:35:00:57:ae

Address in environment is 00:0a:35:00:1a:8b

eth0: ethernet@ff0b0000AXI EMAC: a1020000, phyaddr 0, interface mii

, eth1: ethernet@a1020000AXI EMAC: a1030000, phyaddr 0, interface mii

, eth2: ethernet@a1030000

Hit any key to stop autoboot: 0

MPSOC>

结尾寄语

- 下一篇我们讲解如何驱动fsbl默认不支持的flash,例如上面提到的GD25Q128。

- 作者才疏学浅,文中难免有纰漏的地方,希望读者可以指出,您的点击和评论都是博主码字的动力,感谢大家支持。

本文介绍了在Zynq MPSoC中遇到使用GD25Q128/MX25L128等低容量SPI FLASH无法启动的问题。通过现象描述、JTAG调试及错误代码分析,发现原因是由于Flash不支持Quad-SPI (32b)模式。最终,通过修改启动模式为Quad-SPI (24b)解决了启动失败的故障。下一步将探讨驱动不支持的flash方法。

本文介绍了在Zynq MPSoC中遇到使用GD25Q128/MX25L128等低容量SPI FLASH无法启动的问题。通过现象描述、JTAG调试及错误代码分析,发现原因是由于Flash不支持Quad-SPI (32b)模式。最终,通过修改启动模式为Quad-SPI (24b)解决了启动失败的故障。下一步将探讨驱动不支持的flash方法。

1678

1678

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?