NAND FLASH 基础

-

https://baike.baidu.com/item/Nand%20flash/4883033?fr=aladdin

-

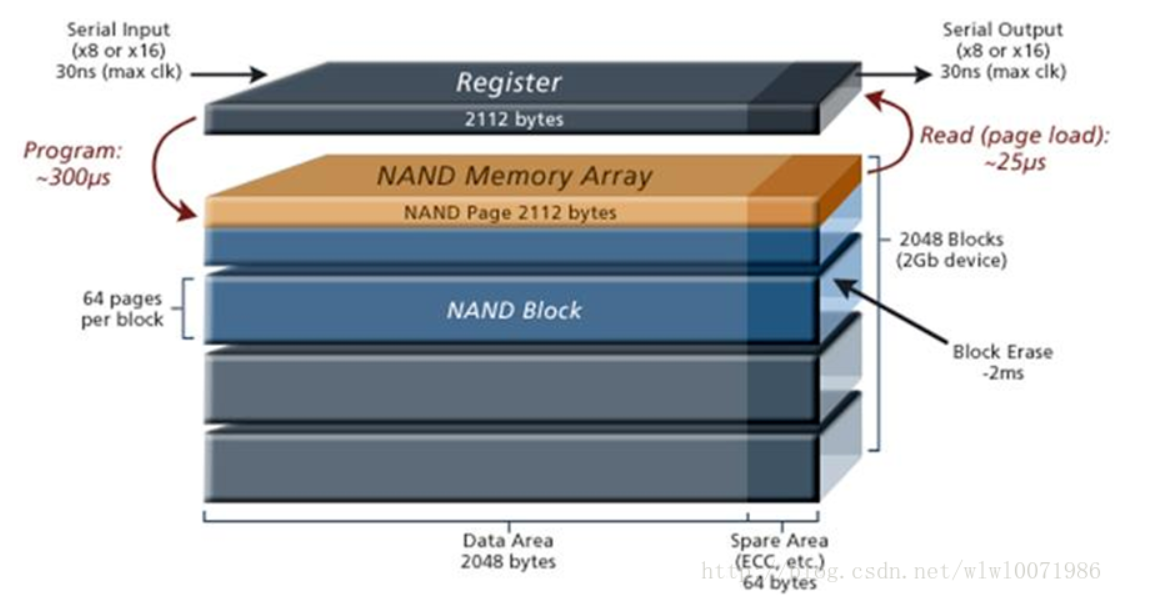

物理构成

NAND Flash 的数据是以bit的方式保存在memory cell,一个cell 中只能存储一个bit。这些cell 以8个或者16个为单位,连成bit line,形成所谓的byte(x8)/word(x16),这就是NAND Device的位宽。这些Line会再组成Page,(NAND Flash 有多种结构,我使用的NAND Flash 是K9F1208,下面内容针对三星的K9F1208U0M),每页528Bytes(512byte(Main Area)+16byte(Spare Area)),每32个page形成一个Block(32528B)。具体一片flash上有多少个Block视需要所定。我所使用的三星k9f1208U0M具有4096个block,故总容量为4096(32*528B)=66MB,但是其中的2MB是用来保存ECC校验码等额外数据的,故实际中可使用的为64MB。

NAND flash以页为单位读写数据,而以块为单位擦除数据。按照这样的组织方式可以形成所谓的三类地址:

Column Address:Starting Address of the Register. 翻成中文为列地址,地址的低8位

Page Address :页地址

Block Address :块地址

对于NAND Flash来讲,地址和命令只能在I/O[7:0]上传递,数据宽度是8位。

NAND型闪存以块为单位进行擦除操作。闪存的写入操作必须在空白区域进行,如果目标区域已经有数据,必须先擦除后写入,因此擦除操作是闪存的基本操作。

-

-

https://blog.csdn.net/qq_40155300/article/details/109385812

NAND Flash是一种非易失性随机访问存储介质

-

nand flash 结构

NAND Flash的容量结构从大到小可以分为Device、Target、LUN、Plane、Block、Page、Cell。

一个Device有若干个Die(或者叫LUN),每个Die有若干个Plane,每个Plane有若干个Block,每个Block有若干个Page,每个Page对应着一个Wordline。

-

-

https://blog.csdn.net/wlwl0071986/article/details/40051755?spm=1001.2101.3001.6650.1&utm_medium=distribute.pc_relevant.none-task-blog-2%7Edefault%7ECTRLIST%7ERate-1.pc_relevant_paycolumn_v3&depth_1-utm_source=distribute.pc_relevant.none-task-blog-2%7Edefault%7ECTRLIST%7ERate-1.pc_relevant_paycolumn_v3&utm_relevant_index=2

-

引脚介绍

引脚名称 引脚功能 CLE 命令锁存功能 ALE 地址锁存功能 /CE 芯片使能 /RE 读使能 /WE 写使能 /WP 写保护 R/B 就绪/忙输出信号 Vcc 电源 Vss 地 N.C 不接 IO0~IO7 传输数据、命令、地址 1. 命令、地址、数据都通过8个I/O口传输 2. 写命令、地址、数据时,都需要将WE、CE信号同时拉低 3. 数据在WE信号的上升沿被NAND Flash锁存 4. 命令锁存信号CLE和地址锁存信号ALE用来分辨、锁存命令或地址 5. CLE为高电平时有效,在WE信号的上升沿命令被锁存 6. ALE为高电平时有效,在WE信号的上升沿地址被锁存 -

存储组织形式

plane是NAND能够根据读、写、擦除等命令进行操作的最小单位

一个plane就是一个存储矩阵,包含若干个BlockBlock是NANDFlash的最小擦除单位,一个Block包含了若干个Page

Page是NANDFlash的最小读写单位,一个Page包含若干个Byte- OOB/Spare Area

每一个页,对应还有一块区域,叫做空闲区域(SpareArea)。在Linux系统中,一般叫做OOB(Out of Band)。

数据在读写的时候相对容易错误,所以为了保证数据的正确性,必须要有对应的检测和纠正机制,此机制叫做ECC/EDC,所以设计了多余的区域,用于存放数据的校验值。

OOB的读写是随着随着页的操作一起完成的。

OOB的具体用途包括以下几个方面:

► 标记所处的block是否为坏块

► 存储ECC数据

► 存储一些和文件系统相关的数据。如jaffs2就会用到这些空间存储一些特定信息,而yaffs2文件系统,会在oob中存放很多和自己文件系统相关的信息

坏块

Nand Flash 中,一个块中含有1 个或多个位是坏的,就称为其为坏块Bad Block。坏块的稳定性是无法保证 的,也就是说,不能保证你写入的数据是对的,或者写入对了,读出来也不一定对的。与此对应的正常的块,肯定是写入读出都是正常的。

- OOB/Spare Area

-

-

http://www.longsto.com/news/27.html?bd_vid=11446947306832031779

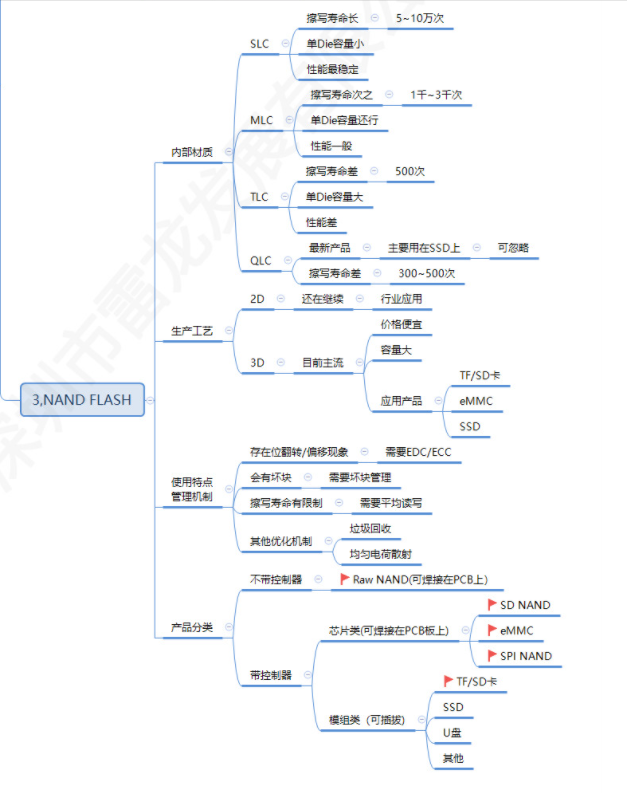

- 使用特点和管理机制

NAND Flash产品本身存在一定的特性,要正常使用,必须配备对应的管理机制。主要有:

1,NAND Flash存在位翻转和位偏移。本来存储的是0101的数据,有一定概率会变成1010。这个时候就需要配备EDC/ECC机制;

2,NAND Flash出厂时会有坏块(不用惊讶,原厂出厂的时候都会标识出来,而且比例是很低),在使用当中也可能产生坏块。因此需要配备 动态和静态坏块管理机制;

3,NAND Flash有写入寿命的限制。每个块都有擦写寿命。因此需要配备 平均读写机制。让整体的块能够均衡的被使用到;

4,NAND Flash是先擦后写,集中擦写的强电流会对周边块有影响等。需要配备 垃圾回收,均衡电荷散射机制等。

-

http://blog.coderhuo.tech/2020/07/18/flash_basics/

-

主要介绍 flash 的结构和 组成

- 读写的操作对象是page,通常是512字节或者2KB

- 擦除的对象是block,通常包含32或64个page(16KB或64KB)

- 每个block在写入前需要先擦除

- block擦除前,需要保证本block上所有page中都不包含有效数据(如果有些page包含有效数据,需要先搬移到其他地方)

-

-

https://blog.51cto.com/u_11934066/2795272

-

根据NAND FLASH的芯片手册,一般的过程是:

发出命令

发出地址

发出数据/读数据NAND FLASH S3C2440

发命令 选中芯片

CLE设为高电平 NFCMMD=命令值

在DATA0~DATA7上输出命令值

发出一个写脉冲发地址 选中芯片 NFADDR=地址值

ALE设为高电平

在DATA0~DATA7上输出地址值

发出一个写脉冲发数据 选中芯片 NFDATA=数据值

ALE,CLE设为低电平

在DATA0~DATA7上输出数据值

发出一个写脉冲读数据 选中芯片 val=NFDATA

发出读脉冲

读DATA0~DATA7的数据

-

-

https://blog.51cto.com/u_15127582/4735925?b=totalstatistic

- nand flash 的驱动参考

-

https://blog.csdn.net/qq543716996/article/details/107980379?spm=1001.2101.3001.6650.1&utm_medium=distribute.pc_relevant.none-task-blog-2%7Edefault%7ECTRLIST%7Edefault-1.pc_relevant_default&depth_1-utm_source=distribute.pc_relevant.none-task-blog-2%7Edefault%7ECTRLIST%7Edefault-1.pc_relevant_default&utm_relevant_index=2

-

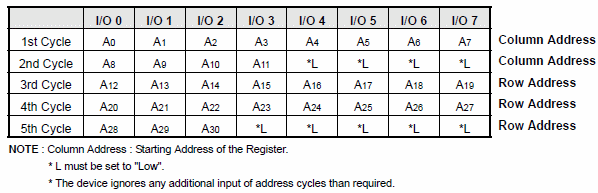

行地址与页地址相关介绍

以K9K8G08U0A为例,此Nand Flash,一共有8192个块,每个块内有64页,每个页是2K+64 Bytes。

假设,我们要访问其中的第7000个块中的第64页中的1208字节处的地址,此时,我们就要先把具体的地址算出来:

物理地址

=块大小×块号 + 页大小×页号 + 页内地址

=128K×7000 + 2K×64 + 1208

=0x36B204B8

nand flash 的地址周期组成 – 从对应的datasheet中获取,不同的芯片地址周期组成不同

Nand Flash地址周期共有5个,2个列(Column)周期,3个行(Row)周期。

-

对应地,列地址A0~A10,就是页内地址,地址范围是从0到2047。

细心的读者可能注意到了,为何此处多出来个A11呢?

这样从A0到A11,一共就是12位,可以表示的范围就是0212,即04096了。

实际上,由于我们访问页内地址,可能会访问到oob的位置,即2048-2111这64个字节的范围内,所以,此处实际上只用到了2048~2111,用于表示页内的oob区域,其大小是64字节。

-

对应地,A12~A30,称作页号,页的号码,可以定位到具体是哪一个页。

A18~A30,表示对应的块号,即属于哪个块。

我们就是要访问第7000个块中的第64页中的1208字节处,对应着

页内地址

=1208

=0x4B8

页号

=块数×页数/块 + 块内的页号

= 7000×(128K/2K) + 64

= 7000×64 + 64

= 448064

=0x6D640

也就是,我们要访问0x6D640页内的0x4B8地址,这样很好理解吧,_。

然后对应的:

页内地址=0x4B8

分成两个对应的列地址,就变成

0x4B8 :列地址1=0xB8,列地址2=0x04

页号=0x6D640,分成三个行号就是:

0x6D640:行号1=0x40,行号2=0xD6,行号3=0x06

再回头看看上面的计算方法,

最开始计算出来的:

列地址1=0xB8

列地址2=0x04

行号1=0x20

行号2=0x6B

行号3=0x03

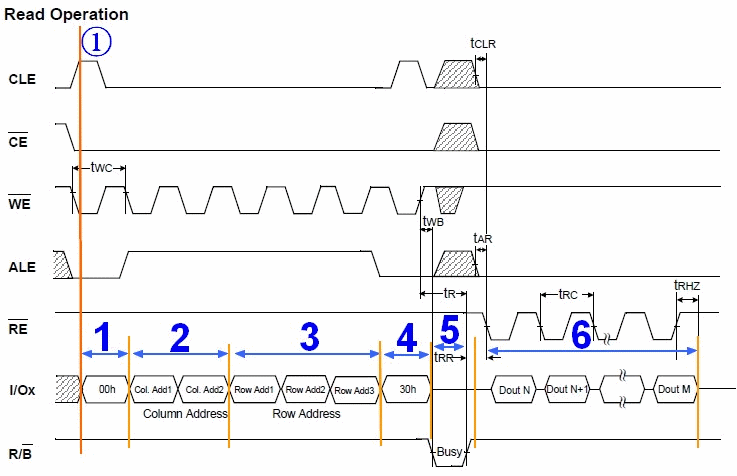

Nand Flash 数据读取操作时序图

在图中的特意标注的①边上的黄色竖线。黄色竖线所处的时刻,是在发送读操作的第一个周期的命令0x00之前的那一刻。

- 黄色竖线穿过的第一行,是CLE。还记得前面介绍命令锁存使能(CLE)那个引脚吧?CLE,将CLE置1,就说明你将要通过I/O复用端口发送进入Nand Flash的,是命令,而不是地址或者其他类型的数据。只有这样将CLE置1,使其有效,才能去通知了内部硬件逻辑,你接下来将收到的是命令,内部硬件逻辑,才会将受到的命令,放到命令寄存器中,才能实现后面正确的操作,否则,不去将CLE置1使其有效,硬件会无所适从,不知道你传入的到底是数据还是命令了。

- 而第二行,是CE#,那一刻的值是0。这个道理很简单,你既然要向Nand Flash发命令,那么先要选中它,所以,要保证CE#为低电平,使其有效,也就是片选有效。

- 第三行是WE#,意思是写使能。因为接下来是往Nand Flash里面写命令,所以,要使得WE#有效,所以设为低电平。

- 第四行,是ALE是低电平,而ALE是高电平有效,此时意思就是使其无效。而对应地,前面介绍的,使CLE有效,因为将要数据的是命令(此时是发送图示所示的读命令第二周期的0x30),而不是地址。如果在其他某些场合,比如接下来的要输入地址的时候,就要使其有效,而使CLE无效了。

- 第五行,RE#,此时是高电平,无效。可以看到,知道后面低6阶段,才变成低电平,才有效,因为那时候,要发生读取命令,去读取数据。

- 第六行,就是我们重点要介绍的,复用的输入输出I/O端口了,此刻,还没有输入数据,接下来,在不同的阶段,会输入或输出不同的数据/地址。

- 第七行,R/B#,高电平,表示R(Ready)/就绪,因为到了后面的第5阶段,硬件内部,在第四阶段,接受了外界的读取命令后,把该页的数据一点点送到页寄存器中,这段时间,属于系统在忙着干活,属于忙的阶段,所以,R/B#才变成低,表示Busy忙的状态的。

-

-

1677

1677

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?