25.1 Introduction

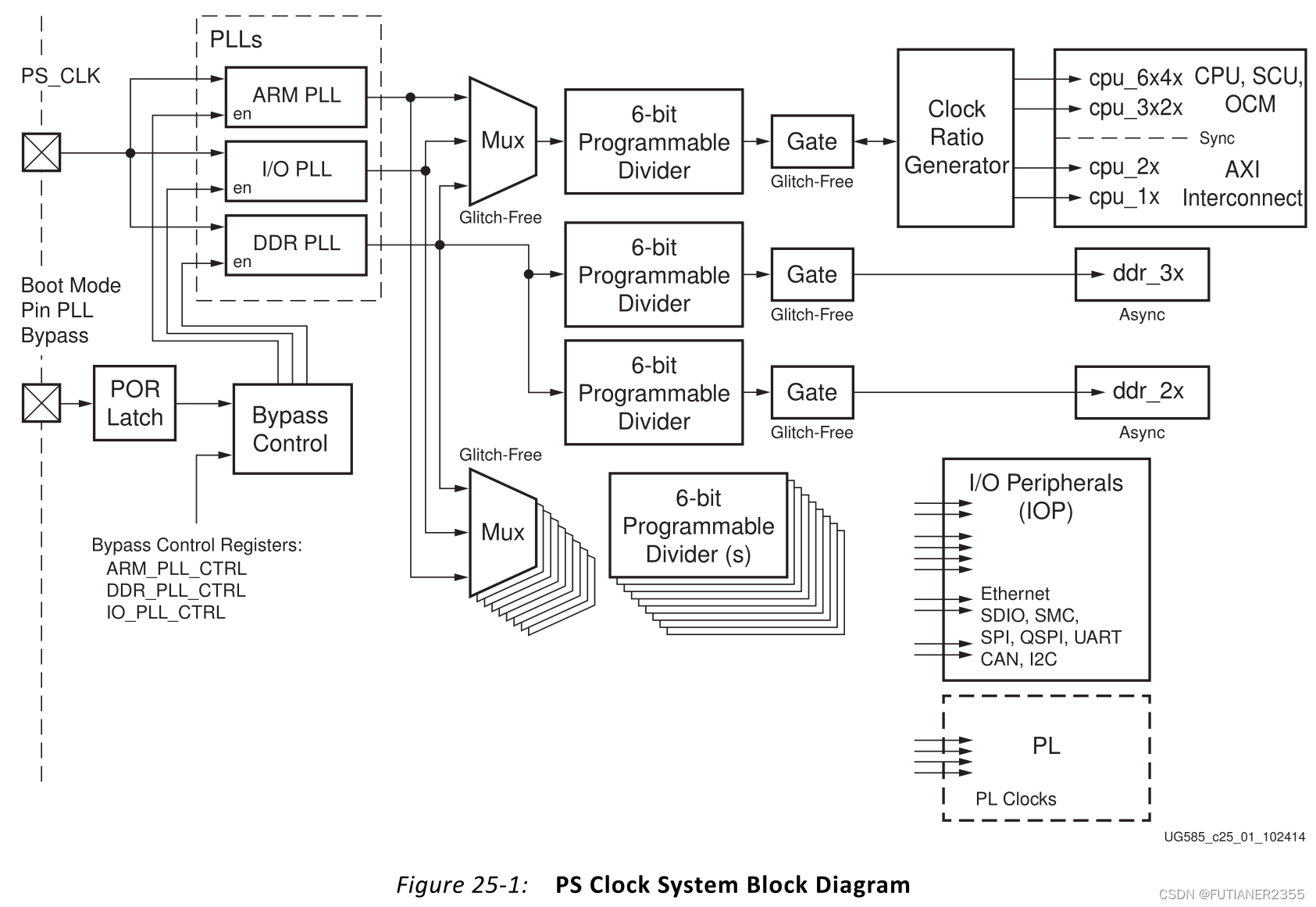

PS时钟子系统产生的所有时钟都来自于三个可编程锁相环中的一个: CPU、DDR和I/O。每一个锁相环与CPU、DDR和外设的时钟松耦合。(Each of these PLLs is loosely associated with the clocks in the CPU, DDR and peripheral subsystems.)

25.1.1系统框图(System Block Diagram)

时钟子系统的主要组成部分如下图所示

25.1.2时钟产生(Clock Generation)

在正常工作时,锁相环被使能enable,由PS_CLK由时钟管脚驱动。在bypass模式下,PS_CLK管脚上的时钟信号为各种时钟发生器提供源,而不是锁相环。

当PS_POR复位信号消失时,锁相环的bypass启动模式的管脚被采样,选择锁相环bypass模式或者锁相环enable模式。bypass模式下系统运行速度明显慢于正常模式,但是对低功耗应用程序和调试有用。在启动程序后,代码正常运行的时候,每个锁相环的bypass模式和输出频率可以通过软件单独控制。

时钟生成路径包括glitch-free multiplexers和glitch-free clock gates,以支持动态时钟控制。

三个可编程锁相环

- 单个外部参考时钟输入全部三个锁相环

ARM PLL:CPU和互连的推荐时钟

DDR PLL:DDR DRAM控制器和AXI_HP接口的推荐时钟

I/O PLL :I/O外设的推荐时钟 - 单独锁相环bypass控制和频率设计

- 压控振荡器VCOs的共享带隙参考电压电路

时钟树

- 6bit可编程分频器

- 大多数时钟电路的动态开关

- PL的四个时钟发生器

复位

时钟子系统是PS的一个组成部分,只有在整个系统复位时才会复位。

系统复位时,控制时钟模块的所有寄存器返回到它们的重置值。

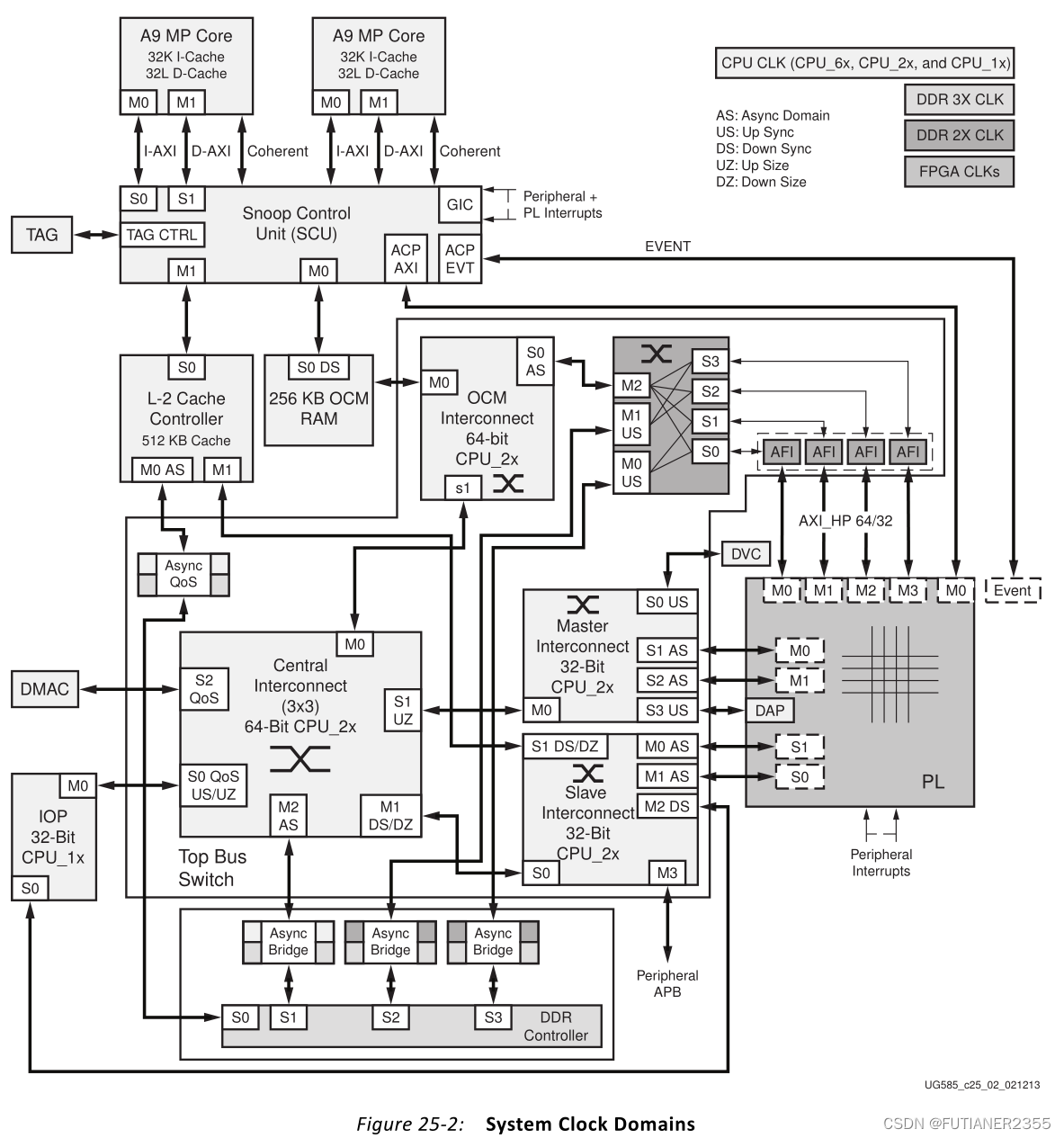

25.1.3 System ViewpointClock Generation

CPU时钟用于大多数内部时钟,DMAC和PL之间的异步DMA外设请求接口不在图25-2中。此外,PL的AXI通道(AXI_HP、AXI_ACP和AXI_GP)在PS和PL之间具有异步接口。发生时钟域交叉的同步位于PS内部。因此,由PL向PS提供接口时钟。上述每个接口都可以在PL中使用唯一的时钟。

25.1.4 电源管理(Power Management)

时钟产生子系统便于时钟去使能和频率控制,从而影响功耗。

锁相环功耗与锁相环输出频率直接相关。功耗可以通过使用较低的锁相环输出频率来降低。如果不需要一个或两个锁相环,功率也可以降低。例如,如果所有时钟发生器都可以由DDR锁相环驱动,那么可以禁用ARM和I/O锁相环以降低功耗。DDR锁相环是唯一可以驱动所有时钟发生器的单元。

每个时钟可以在不使用时单独禁用。在某些情况下,单个子系统包含额外的时钟禁用和其他功耗降低功能。

中央互连时钟禁用(Central Interconnect Clock Disable)

通过设置TOPSW_CLK_CTRL[0]位为1,可以停止中央互连(CPU_2x和CPU_1x)的CPU时钟。当设置此位时,时钟控制器等待到L2-cache和SCU的AXI接口变为空闲状态,并等待来自PL的FPGAIDLEN信号置为有效,然后才会关闭中央互连时钟。对于其他接口,系统软件必须确保接口处于空闲状态后,才能关闭对接时钟。只要PS检测到L2-cache或SCU上的流量,或者FPGAIDLEN无效,时钟就会重新启用。

5569

5569

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?