后附的资源中文件夹内LCD程序使用“睿智FPGA Ⅳ助学板”+“特权FPGA套件LCD模块”。LCD模块中液晶屏型号是LQ035NC111,并且IF0、IF1和IF2都接地,即使用并口RGB数据模式。手册中该模式下操作频率为6.5MHz。

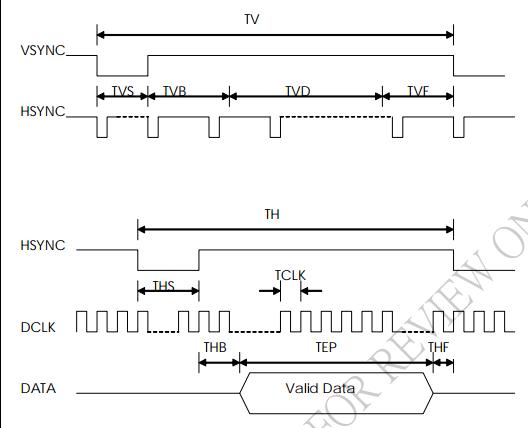

LQ035NC111并口模式下的时序要求如下

典型的分辨率为320*240(60Hz)。因此得到如下编程数据:

| 320×240×60Hz | 屏幕,一行320个像素点,共240行。每秒钟显示60帧画面。

a段和o段 为低电平,其它段是高电平。 一个列像素是最小单位(一个脉冲),则每秒钟需要的脉冲数: 408×262×60=6413760,即一个脉冲占156ns,约6.4MHz | ||||||||||||||||||||||||

| HSYNC列信号计数 | 0~29: a段,低电平 (从0起计数) 68~387:c段,320列像素有效计数 0~407:共408个计数 | ||||||||||||||||||||||||

| VSYNC行信号计数 | 0~2:o段,低电平 (从0起计数) 18~257:q段,240行扫频有效计数 0~261:共262个计数 |

当使用PLL提供lcd_clk时,lcd_clk的引脚从PIN_55改为PIN_43.

资源地址: http://download.csdn.net/detail/yangqiwei2012/6615423

7654

7654

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?