视频讲解地址:

B站讲解视频https://www.bilibili.com/video/BV1DL4y1p7Hu/ https://www.bilibili.com/video/BV1DL4y1p7Hu/

https://www.bilibili.com/video/BV1DL4y1p7Hu/

- 1.SRAM及工作原理介绍

- 2.DSP6713的LocalBus

- 3.FPGA对EMIF的时序译码

- 4.DSP6713的操作外设1

- 5.DSP6713的操作外设2

- 6.FPGA在LocalBus总线上扩片选应用

- 7.实现对FPGA内部逻辑块的控制

- 1.SRAM及工作原理介绍

sram是英文static ram的缩写,它是一种具有静止存取功能的内存,不需要刷新电路即能保存它内部存储的数据。

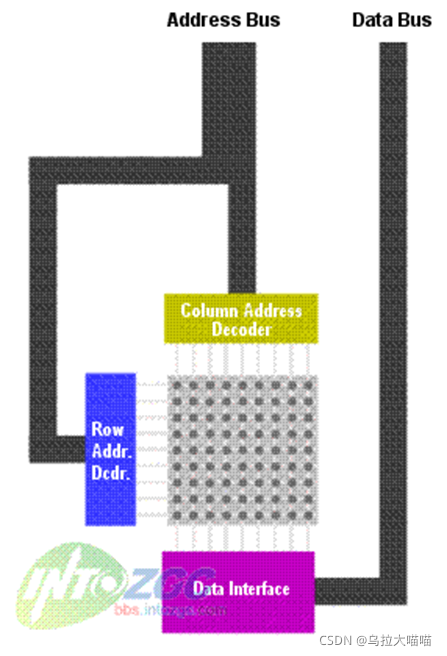

对于处理器。它通过地址总线发出一个具有22位二进制数字的地址编码--当中11位是行地址,另外11位是列地址,这是通过RAM地址接口进行分离的。行地址解码器(row decoder)将会首先确定行地址,然后列地址解码器(column decoder)将会确定列地址,这样就能确定唯一的存储数据的位置,然后该数据就会通过RAM数据接口将数据传到数据总线。

另外,须要注意的是,RAM内部存储信息的矩阵并非一个正方形的,也就是行和列的数目不是同样的。

引用网址:FPGA第一篇:SRAM工作原理 - yjbjingcha - 博客园

以cypress公司的静态存储器CY7C1041B为例:

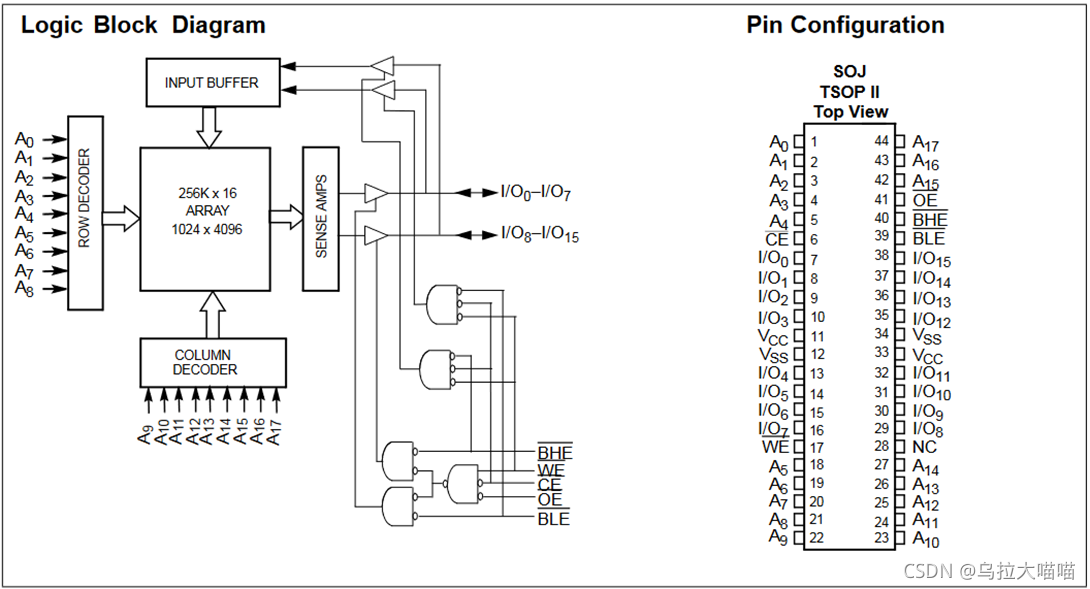

内部的逻辑框图:

其中I/O0~15是通常意义上的数据总线DATA0~15。

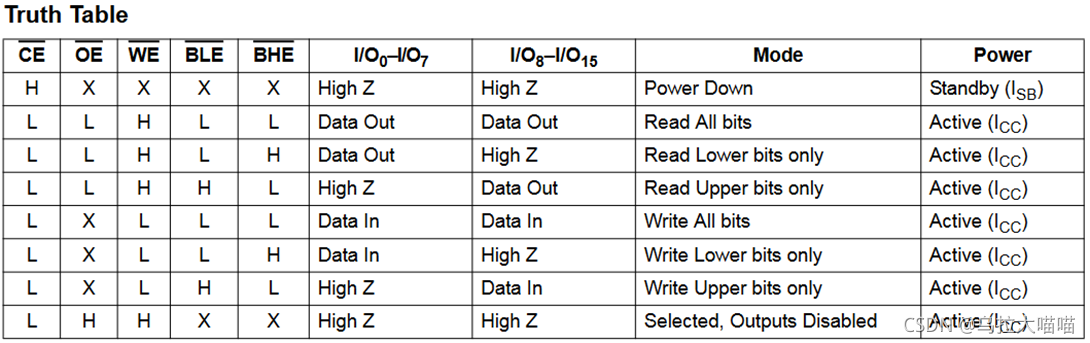

真值表

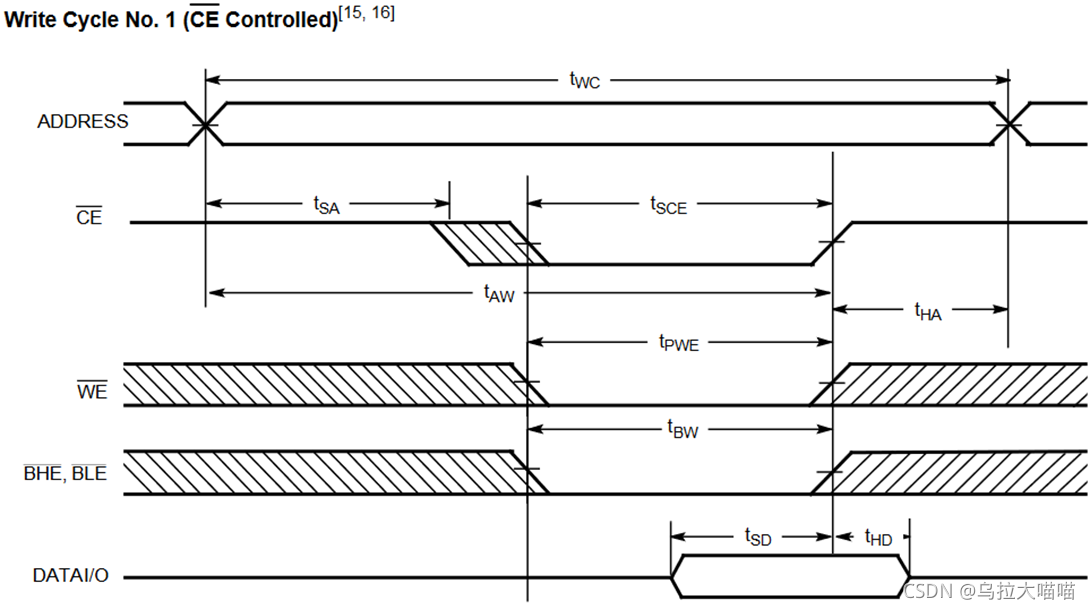

写时序:

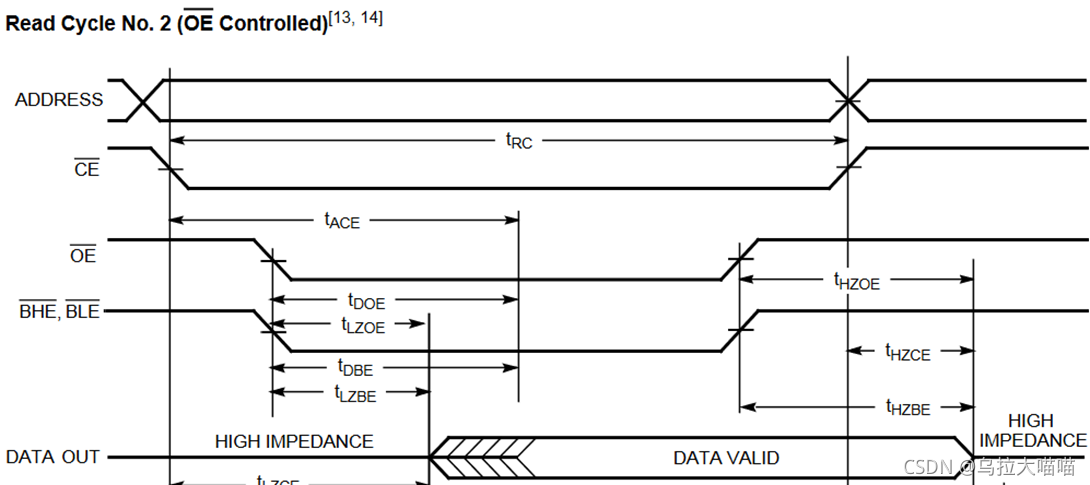

读时序:

- 2.DSP6713的LocalBus

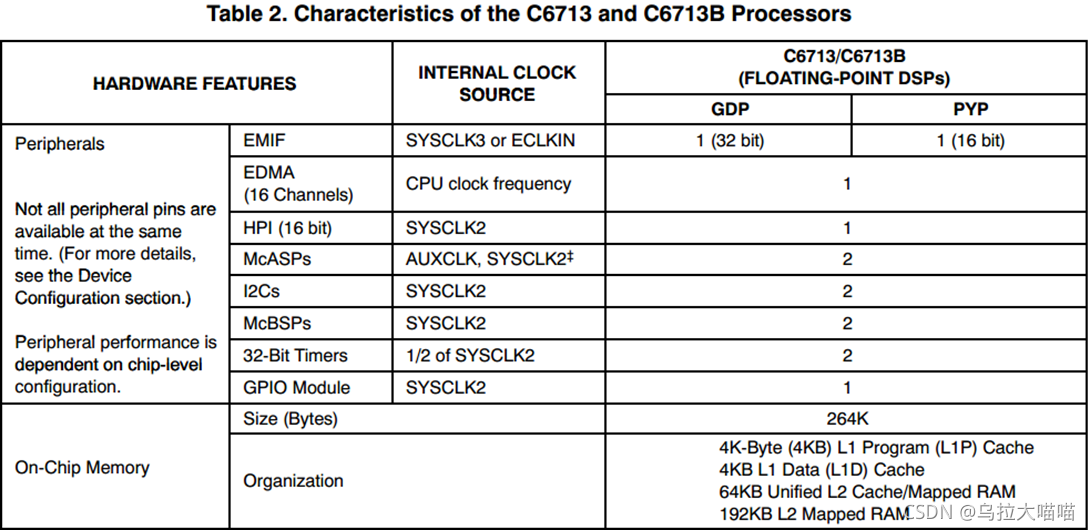

TMS320C6713 DSP是美国TI推出的C6000系列DSP芯片的一款,它是32位高速浮点型DSP,时钟最高频率为200MHz。

外设资源为:

由于外设资源较少,且McxSP的接口有些时序并不标准,故多采用DSP6713+FPGA的方式扩展外设接口。

本文介绍了通过FPGA扩展TMS320C6713 DSP的LocalBus总线,实现外设接口扩展。详细讲述了SRAM的工作原理,DSP6713的LocalBus特性,以及FPGA如何对接EMIF时序进行译码,同时展示了如何利用FPGA解决片选不足的问题,并实现对FPGA内部逻辑块的控制。

本文介绍了通过FPGA扩展TMS320C6713 DSP的LocalBus总线,实现外设接口扩展。详细讲述了SRAM的工作原理,DSP6713的LocalBus特性,以及FPGA如何对接EMIF时序进行译码,同时展示了如何利用FPGA解决片选不足的问题,并实现对FPGA内部逻辑块的控制。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

845

845

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?