计算机的发展与应用

没什么好记的,了解一下就行

计算机的应用和展望

总线

总线的基本概念

总线式连接各个部件的信息传输线,是各个部件共享的传输介质

总线上信息的传送

串行

并行

单总线结构框图

问题:只要有I/O设备输入,CPU的工作就会停止等

改进:面向CPU的双总线结构

问题:当主存想要与I/O设备发生关系时又会...

改进:以存储器为中心的双总线结构框图

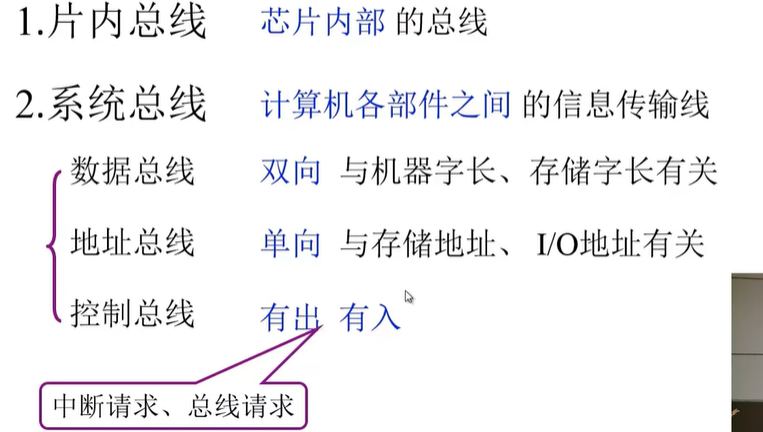

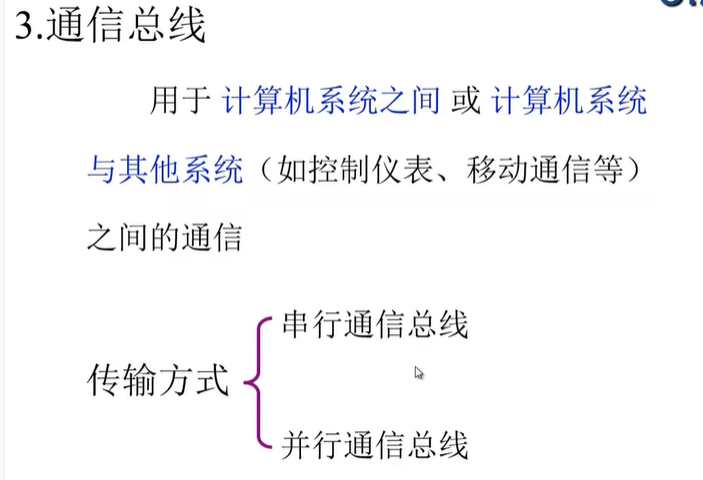

总线的分类

总线特性及性能指标

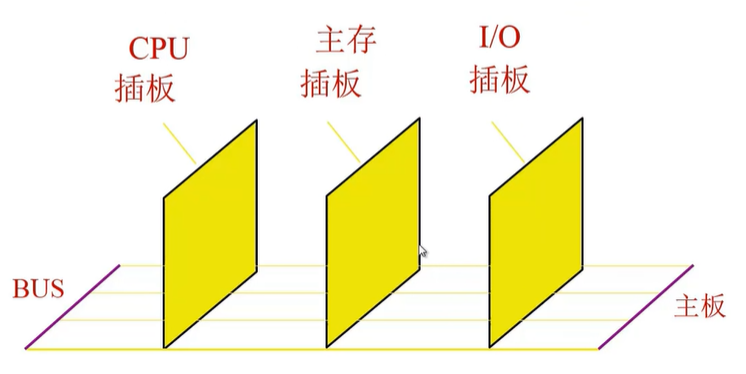

总线物理实现

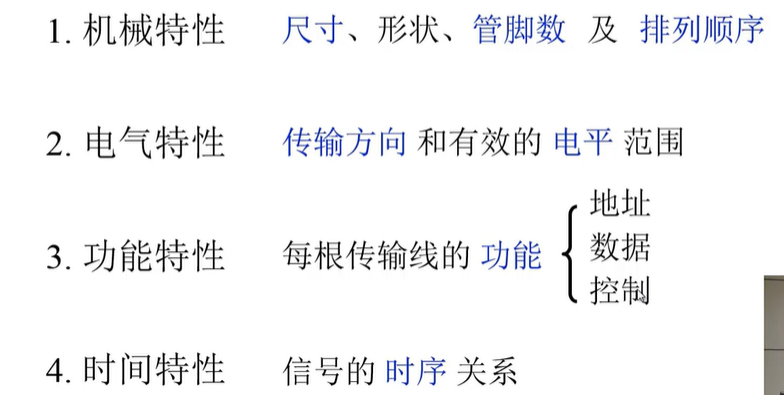

总线特性

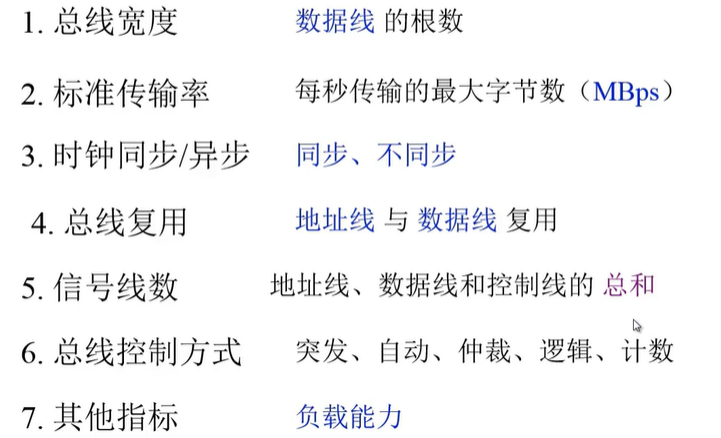

总线性能指标

总线结构

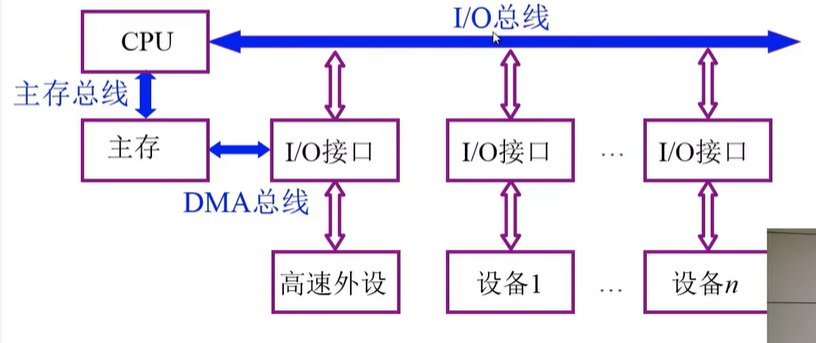

三总线结构

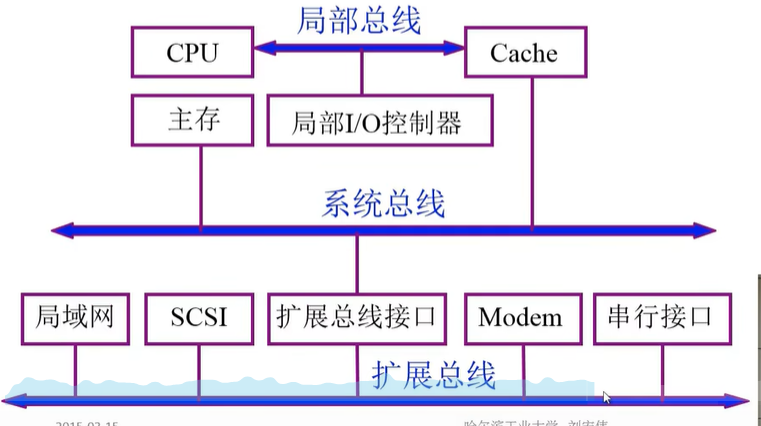

另外一种形式

四总线结构

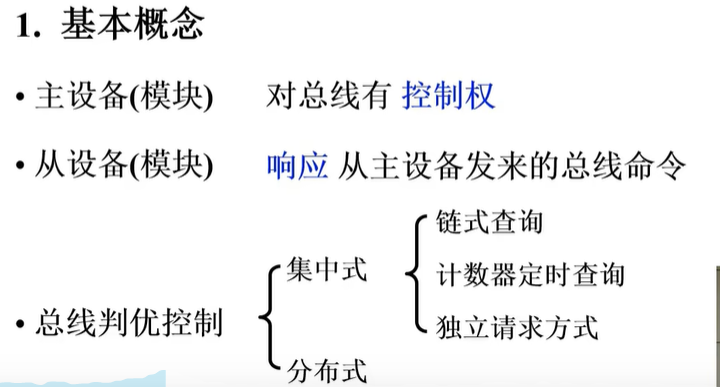

总线控制

总线判优控制

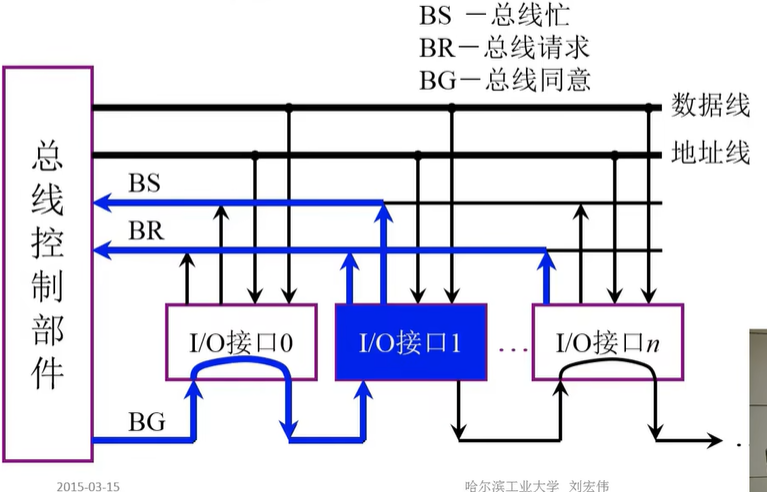

链式查询方式

接口有总线请求时利用BR线发起请求,如果总线控制部件同意该请求

则从BG线发起查询,依次询问接口是否发起请求

当查到发起请求的接口时该接口在BS线上表明总线忙的信息

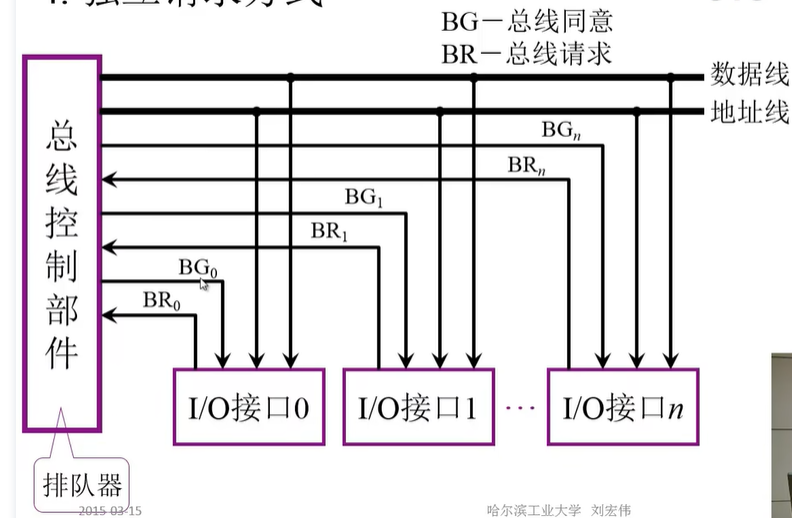

计数器定时查询

计数器可以设置,所以有一定程度的自由

独立请求方式

总线通信控制

目的 解决通信双方协调配合问题

总线传输周期

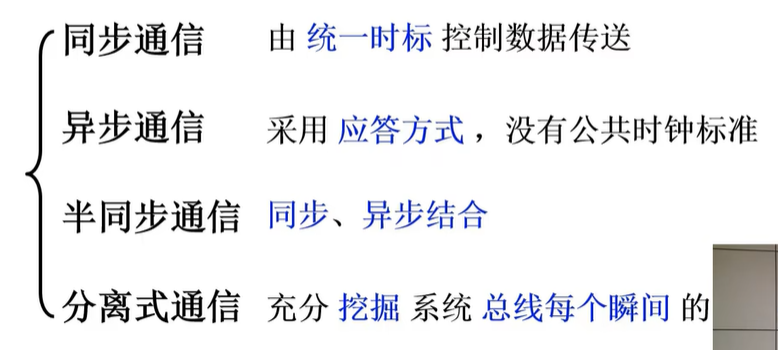

总线通信的四种方式

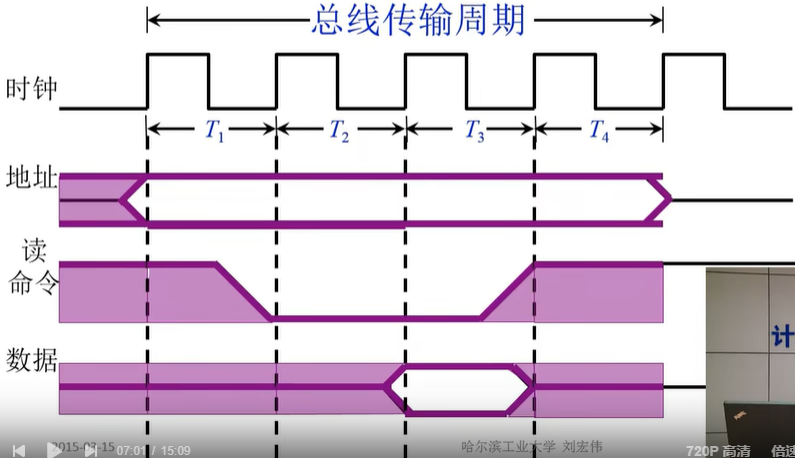

同步式数据输入

时钟信号改变时改变相应控制信号

固定的时间点上给出固定的操作

第一个上升,给出地址,就是之前PC发出命令,然后T1时间段内完成,PC到MAR到存储体到MDR到IR,T2上升就是IR接收到读命令并发出那一瞬间

T2的上升沿,IR给出读命令信号,T2时钟周期内,主设备告诉从设备,主设备要从从设备读入数据

T3的上升沿,从设备通过数据总线给出数据信号,T3时钟周期内,从从设备读取数据

同步式数据输出

例如写命令在T2上升沿变成了低电平,低电平有效,写命令就开启了,

等到T4上升沿,写命令高电平,失效

看最顶部的时钟,一个周期的上升沿就是最左边的竖线,下降沿就是中间的竖线

同步方式对任何两个设备之间的通信都给予同样的时间安排。就总线长度来讲,

必须按距离最长的两个设备的传输延迟来设计公共时钟。但是总线长了势必降低传输频率。

异步通信

不互锁

发送方不管接收方是否接收到请求信号,过一段时间就会撤销请求信号

接收方不管发送方是否接收到回答信号,过一段时间就会撤销回答信号

半互锁

发送方接收到接收方的应答之后再撤销请求信息

可能出现的问题:因为主设备没有收到应答,而从设备又关闭了信号发送,则主设备始终处于高电平状态里

全互锁

在半互锁的基础上,请求放在接收到发送方撤销请求信息的信息时才会撤销自己的回答信息

这种模式可以实现可靠的数据传输

如果发现数据出错,半互锁和全互锁可以要求从设备重新发送数据信息

异步通信就是通过请求和回答这两个握手信号来完成通信联络的

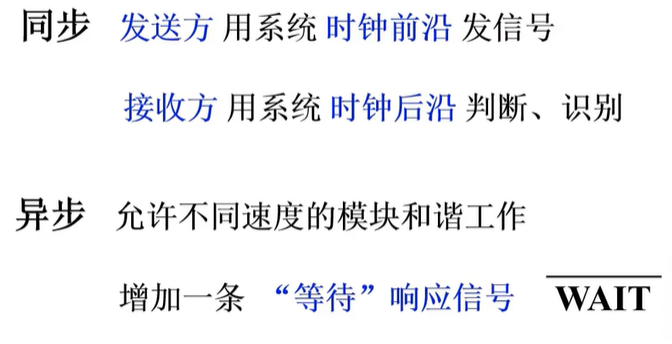

半同步通信(同步,异步结合)

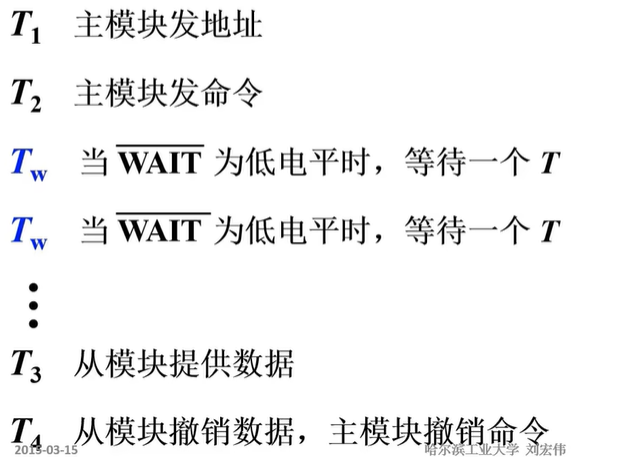

以输入数据为例的半同步通信时序

这时候就需要从模块发出wait信号,让主模块等等他,一次等一个时钟周期,在下个时钟周期开始前检测wait,低电平继续等,高电平说明准备好数据了,拿就完事

简单来说就是主从模块速度不匹配,一个快一个慢,那么主模块发送读命令后,t3读数据,但是从模块没来得及把数据放到数据总线

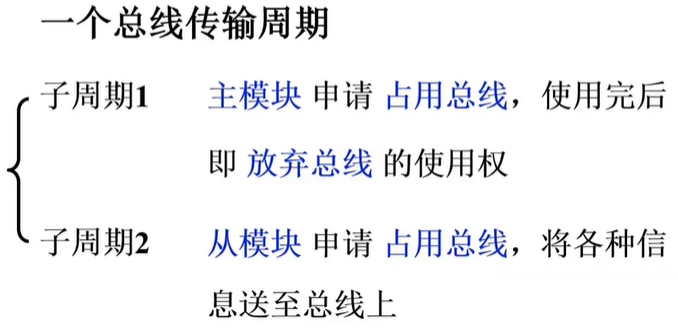

总线传输周期

上述三种通信的共同点

分离式通信

充分挖掘系统总线每个瞬间的潜力

区别在于分离式,主模块发送完地址和请求之后就不占用总线了,

而半同步式主模块会在总线上继续await到从模块准备完成

分离式通信特点

各模块有权申请占用总线

采用同步方式通信,不等对方回答

各模块准备数据时,不占用总线

总线被占用时,无空闲

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?