memory consistency model

定义了对于programmer和implementor来说,访问shared memory system的行为;

对于programmer而言,他知道期望值是什么, 知道会返回什么样的数据;;

对于implementro而言,他知道应该取怎么实现,知道需要提供什么样的数据;

shared memory的访问,会带来什么问题?

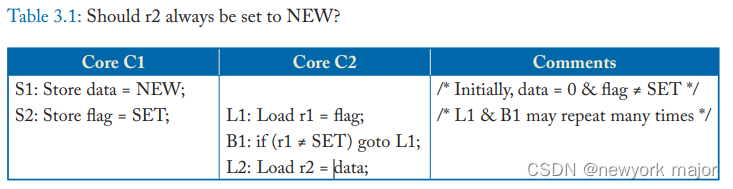

本意是,想要在flag==SET时,获取r2的内容为NEW;

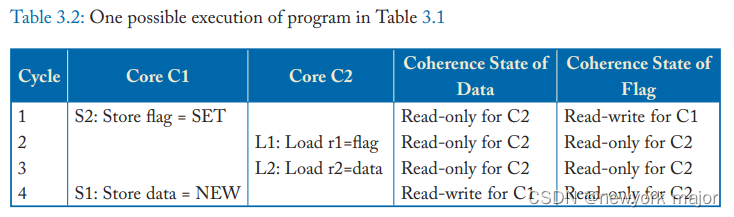

但是如果core1 进行reorder, S2先执行,S1后执行,则可能拿到的数据为0(初始值);

因为core可以进行重排序,因此,如果core c1先执行S2(有可能,因为两个store地址不同),则可能会拿到r2=0, 而不是预期的new;

有哪些reorder memory access的方式?

- store-store reordering

如果一个core的write buffer不是fifo结构的,则两个store可能会被重排序;

例如:

如果第一个store在cache中是miss的,第二个是hit的;

或者第二个store可以与更早的进行merge;

所以,即使core是按照po的顺序来执行的,reorder也可能发生;

对于单个thread而言,究竟以什么顺序执行无所谓,但是多余多线程,如上图所示,其执行的顺序,就会影响程序预期的结果;

- load-load reordering

现代的动态调度的core, 可能执行顺序与po不同。例如,在上面的例子中,Core C2, 可能会先执行L1, 再执行L2, 抑或相反;

对于单线程而言,这种乱序,不会有影响,因为其地址是不同的;

对于多线程而言,如果两个core之间,存在相同地址的访问,则可能出现如图所示的各种执行顺序,对程序的执行结果,也会有相应影响;

- Load-store and store-load reordering.

对于不同地址的store和load,也会发生乱序;

考虑load,xxx, store, 乱序后,可能会有各种问题,例如load/store本来是受lock保护的,store是release lock, 如果交换了顺序,此load不再受保护;

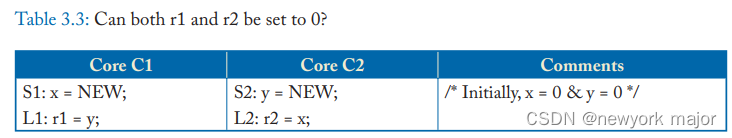

考虑store, xxx, load,如下图所示:

store-load reorder, 会导致r1/r2的值,都读到0;

这个例子,也是满足SWMR Invariant的,所以造成这个的原因,与coherence没关系;

需要注意的是,store-load reordering, 可能也是因为FIFO write buffer的local bypassing造成的,所以,即使core是按照PO的顺序来执行,也可能导致程序未按照预期执行;

这些例子都引出一个问题:对于一段特定的programm order的程序,其具体的执行结果,是不确定的;Thus, we must consider non-determinism when defining shared memory behavior(因此,在定义共享内存行为时,我们必须考虑不确定性。)

什么是memory consistency model?

上面的例子说明了,share memory的具体行为是微妙的,所以这就使得解决:

- programmer可以预期怎样的行为;

- implementors可以做什么样的优化;

这两个问题有了意义;

memory consistency model就是为了解决这两个问题;

- 它是定义了多线程访问share memory的一种规范;

- 对于多线程,如果给定了输入数据,它定义了load可能返回的值;

- 不同于单线程,多线程通常有多个正确的行为;

通常情况下, memory consistency model(MC)定义的rule支持两种规则:

- 需要服从MC的partiion

- 以及不需要服从MC的partition;

memory consistency model VS memery coherence

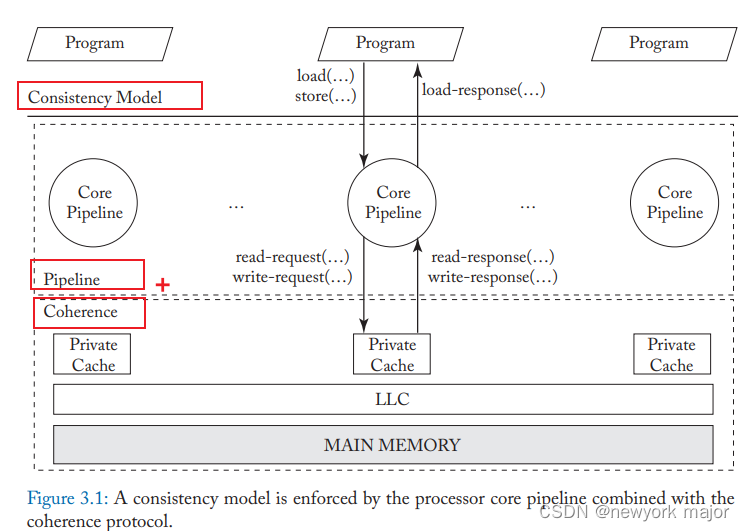

- coherence只是简单的提供给处理器piple一个抽象的memory system;

- 它自己并不能决定shared memory behavior, 而是要受pipeline的影响;

- 例如,pipeline对memory operation进行了reorder, coherence即使工作正确,对share memory的操作也是错误的;

- In summary:

- Cache coherence does not equal memory consistency.

- A memory consistency implementation can use cache coherence as a useful “black box.”

- consistency model由core pipeline与一致性协议相结合来实现;

565

565

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?