前提:sensor总数据量* (1+20%) < Lane数*Mipi速率

sensor总数据量 = sensor有效像素 * 色彩深度(raw位数) * 帧率

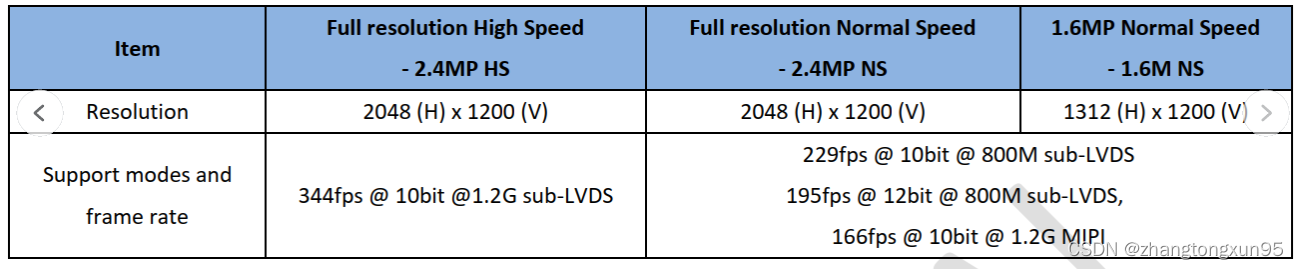

以下图为例,mipi输出166帧1080P10bit的数据总量为1920*1080*10*166*1.2 = 4.13 Gbps,输出为1.2Gbps

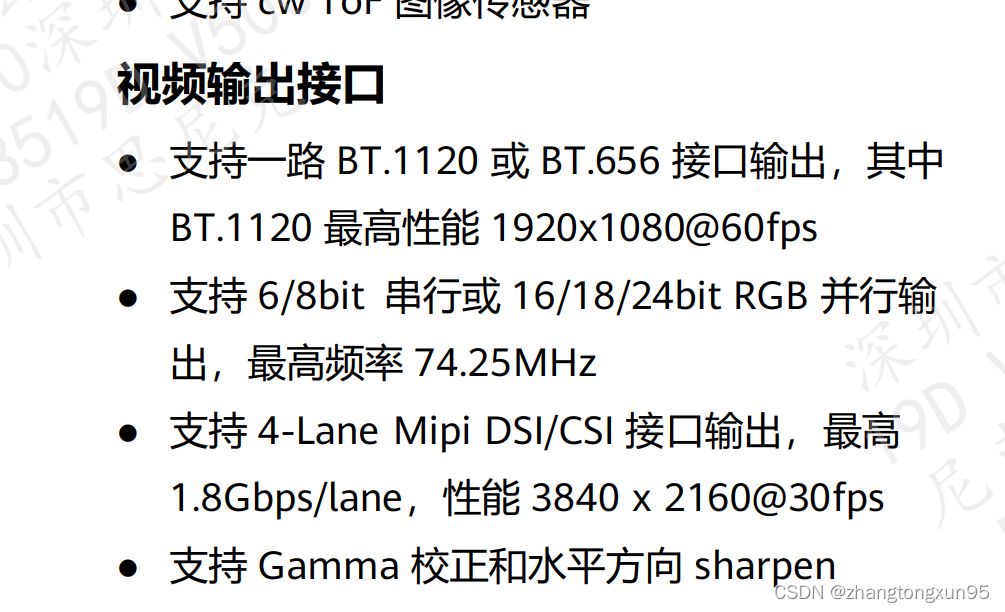

从SOC手册中可以看到最高速率1.8Gpbs,个人理解每lane的最低速率以sensor和soc二者之间小的为准。总数据量为4.13,单lane最小1.2,所以最小lane数为4。

备注:

关于总数据量*1.2的解释

1、降额设计,留20%的余量;

2、mipi协议并不是只传帧数据,还有帧头帧尾,控制信号等等 ,所以实际配置的mlk一定会留有一定余地的。

3、video 会有horizontal blanking 和 vertical blanking,算mipi 速率的时候把这些也得考虑进去,不然时序会崩掉。

关于lane数量的解释(来源于网络,侵删)

在MIPI CSI-2规范中,Lane的数量决定了传输的带宽,因此,理论上,增加Lane的数量可以提供更高的峰值带宽。

对于是否越多越好的问题,可以从以下几个方面来分析:

-

带宽需求:应用对带宽的需求越高,使用更多的Lanes就越有必要。例如,高分辨率或高帧率的视频传输需要更大的带宽,因此可能需要更多的Lanes来避免高时钟频率带来的信号完整性问题。

-

信号完整性:多条Lane可以通过降低每条Lane上的时钟频率来减少信号完整性问题,从而在保持数据速率的同时提高信号的稳定性。

-

功耗考量:更多的Lane可能会增加功耗,因为每个Lane都需要额外的物理层逻辑单元和传输电路。然而,较低的时钟频率可能有助于降低每条Lane的功耗。

-

成本与设计:从硬件设计的角度来看,增加Lane的数量会增加设计的复杂性和成本。同时,需要考虑PCB布线和终端设备的设计空间。

-

兼容性问题:当发送器和接收器之间存在不匹配的Lane数量时,可能需要通过CCI进行重配置以确保兼容性。如果发送器的Lane数量多于接收器,可能会有性能损失。

-

数据传输效率:由于可能存在有效数据的总字节数不是Lane数量的整数倍的情况,一条或多条Lane可能会提前完成传输并发送EoT。这意味着并不是所有情况下增加Lane都能带来线性增长的效率。

-

编码与解码:MIPI规范并没有要求特定的线路编码方式,但是数据的序列化和反序列化是由PHY层处理的,这一层不会关注进出数据的特定含义、值或顺序等信息。

-

传输速率限制:MIPI CSI的最高传输速率为2.5Gbps/lane,某些低版本为1.5Gbps/lane。在连接image sensor时,需要根据实际的传输速率和所需的带宽进行评估。

此外,在选择Lane数量时,应考虑以下几点:

- 根据应用的带宽需求选择合适的Lane数量;

- 考虑到信号完整性和功耗之间的平衡;

- 注意硬件设计的复杂性和成本;

- 确保发送器和接收器之间的兼容性;

- 理解数据传输效率可能受到有效数据字节数与Lane数量关系的影响;

- 考虑不同MIPI版本的传输速率限制。

综上所述,MIPI传输时并非Lane越多越好,而是应根据具体的应用需求和设计考量来选择恰当的Lane数量。适当的Lane数量可以在满足性能要求的同时,避免不必要的功耗和成本增加。

3788

3788

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?