目录

一、IIC总线简介

IIC(Inter-Integrated Circuit)——内部整合电路。是飞利浦公司于1980年设计的一种多主从架构的串行通讯总线,主要用于低速设备的连接。读法为“I-squared-C”、“I方C”或者“I-two-C”。

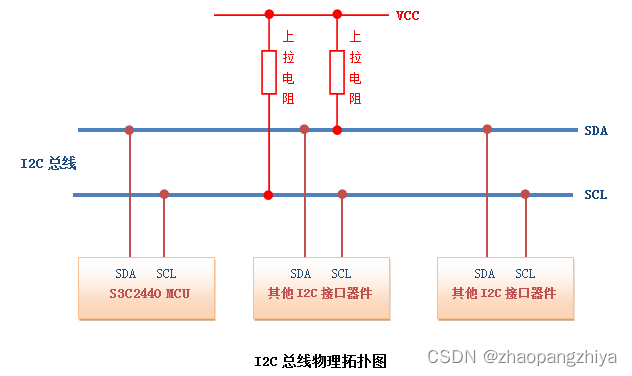

二、IIC总线的拓扑结构

IIC总线分别由SDA(串行数据线)和SCL(串行时钟线)及上拉电阻组成。通信原理是通过对SCL和SDA线高低电平时序控制,来产生IIC总线协议所需要的信号进行数据传递。在总线空闲时SCL和SDA由上拉电阻拉高保持高电平状态。连到总线上的任一器件输出低电平都将使总线的信号变低,即器件的SDA和SCL都是线“与”的关系。

图1

三、IIC总线特征

1.IIC为半双工通信。只有一根SDA线进行数据传输,即同一时间只可单向通信(485也为半双工,SPI和串口为全双工)。

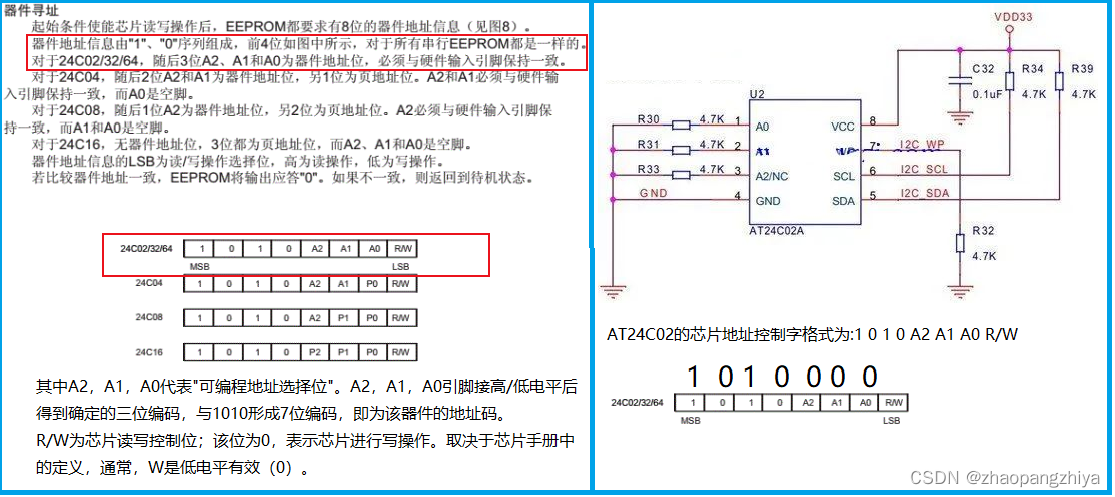

2.IIC总线上每一个设备都可以作为主设备或者从设备,每一个设备均有一个唯一的地址。主设备通过该地址来确定与哪个从设备进行通信。从设备的地址一般物理接地或拉高来确定。

图2

3.IIC总线上可以挂接的设备数量受总线的最大电容400pF限制,即总线电容不能超过400pF。管脚都是由输入电容的,PCB上也会有寄生电容,所以会有一个限制。实际设计中经验值大概不会超过8个器件。规定总线最大电容是因为IIC的OD(漏极开路)要求外部有上拉电阻,电阻和总线电容会产生RC演示效应,电容越大信号的边沿就越缓慢,有可能带来信号质量风险;传输速度越快,信号的窗口就越小,上升沿、下降沿时间要求就更短更陡峭,所以RC乘积必须更小。(我们知道IIC是靠上拉出来的高电平,信号上升所需的时间正比于上拉电阻值和该点对地电容的乘积。)

当总线挂接相同型号的IIC器件时,该型号器件的最大挂接数还会受器件地址位的限制。如上图中AT24C02的物理地址位有三位(A2、A1、A0),所以同一IIC总线最多可挂接8个AT24C02A。

4.IIC总线的传输速率在标准模式下可达100kbit/s;快速模式下可达400kbit/s;高速模式下可达3.4Mbit/s。可通过IIC总线接口可编程时钟来调整传输速率,传输速率也和所接的上拉电阻的阻值有关。

5.IIC总线为多主从结构,可以连接多个主机。如果两个或者更多主机同时初始化,数据传输需要通过冲突检测和仲裁的方法放置数据被破坏,具体下文会详细说明。

6.IIC总线的从地址有3种类型,分别为7位、8位和10位。产生多种类型的原因是厂商采用的不同地址约定。不同的寻址方式在下文会详细说明。

7.IIC总线的实现方式有两种,分别是硬件IIC和软件IIC。

软件IIC是程序员使用程序控制SCL和SDA的IO输出控制高低电平,模拟实现IIC协议的时序,该方式较硬件IIC稳定,但程序较为繁琐。

硬件IIC是程序员调用IIC相关的控制函数,不用直接取控制SCL和SDA的高低电平的输出。但是有限单片机的硬件IIC不太稳定,调试问题较多。

| 实现方式 | 模拟IIC | 硬件IIC |

| 用法 | 通过程序实现对IO口的控制模拟IIC协议时许 | 调用IIC相关的控制函数(库函数),不用直接控制SCL和SDA连接的IO口 |

| 速度 | 速度快,效率高,可以使用DMA | |

| 使用引脚 | 任意引脚 | 固定管脚 |

| 稳定性 | 稳定 | 有些单片机的不太稳定 |

四、IIC总线协议

(1)IIC总线信号类型

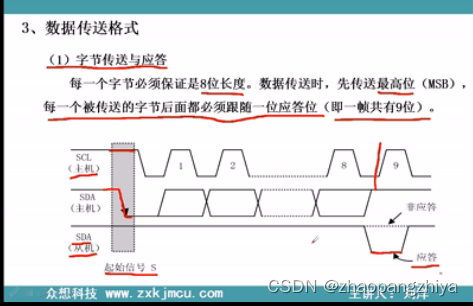

IIC总线在数据传输过程中共有三种信号类型,分别是起始信号、应答信号、和结束信号;总线数据开始传输时必须以起始信号作为开始条件,以结束信号作为停止条件;从机在接收到8bit数据后应向发送数据的IC发送应答信号。其中,起始信号是必须的,应答信号和结束信号不是必须的。

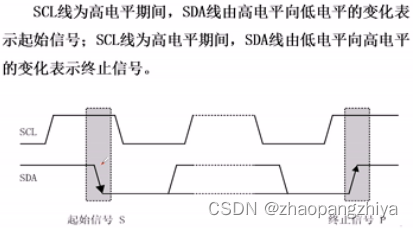

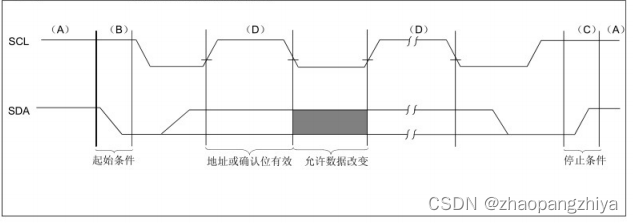

起始信号的产生:IIC总线在空闲状态时(SCL和SDA由于被上拉都保持高电平),当SCL为高电平而SDA由高到低电平跳变,表示产生一个起始条件。此时总线进入忙状态。

停止信号的产生:IIC总线在忙状态的时候(SCL为高电平,SDA为低电平),当SCL为高电平而SDA由低到高电平跳变,表示产生了一个停止条件。

图3

应答信号的产生:每当发送数据IC器件(主机)传输完一个字节的数据之后,该器件会等待一定时间,等待接收方的应答信号。接收数据的IC器件(从机)会通过拉低SDA数据线给发送端发送一个应答信号,以提醒接收数据完成。若由于某种原因从机不对主机寻址信号做应答时,从机必须将SDA线拉高(非应答信号),之后由主机产生一个终止信号以结束总线数据传送。若从机对主机进行了应答,但在数据传输一段时间后无法继续接收更多的数据时,从机可通过对无法接受的第一个数据字节做非应答通知主机,主机则在之后发出终止信号来结束数据的传送。当主机接收数据时,他收到最后一个数据字节后,必须项从机发出一个结束传送的信号,这个信号是由主机对从机的非应答来实现的,在这之后,从机释放SDA线以允许主机产生终止信号。

图4

(2)IIC总线数据传输

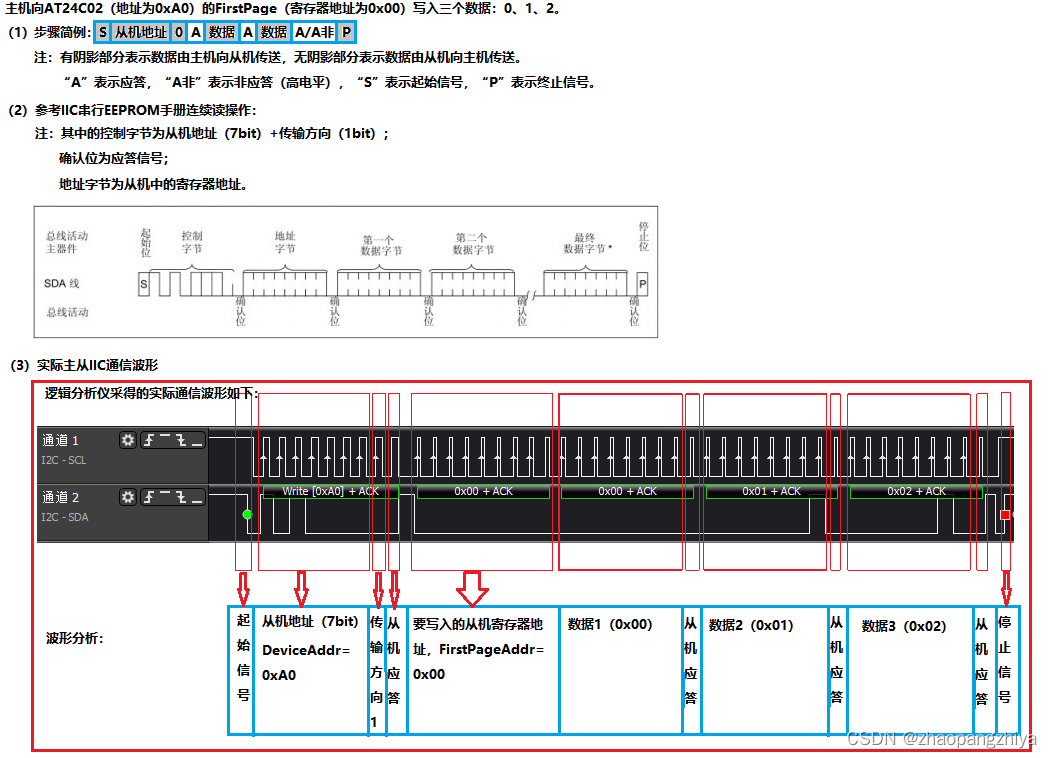

上文提及总线上的每一个器件都有唯一的地址,而主机和从机之间的通信也是建立在总线寻址的基础上。即主机在传输数据之前须先指定要访问的从机的地址(大部分器件都是7位寻址——地址为7bit),再确定数据传输方向(1bit——为“0”表示主机向从机写数据,为“1”表示主机由从机读数据),最后才能进行数据传输。

主机向从机发送数据:

图5

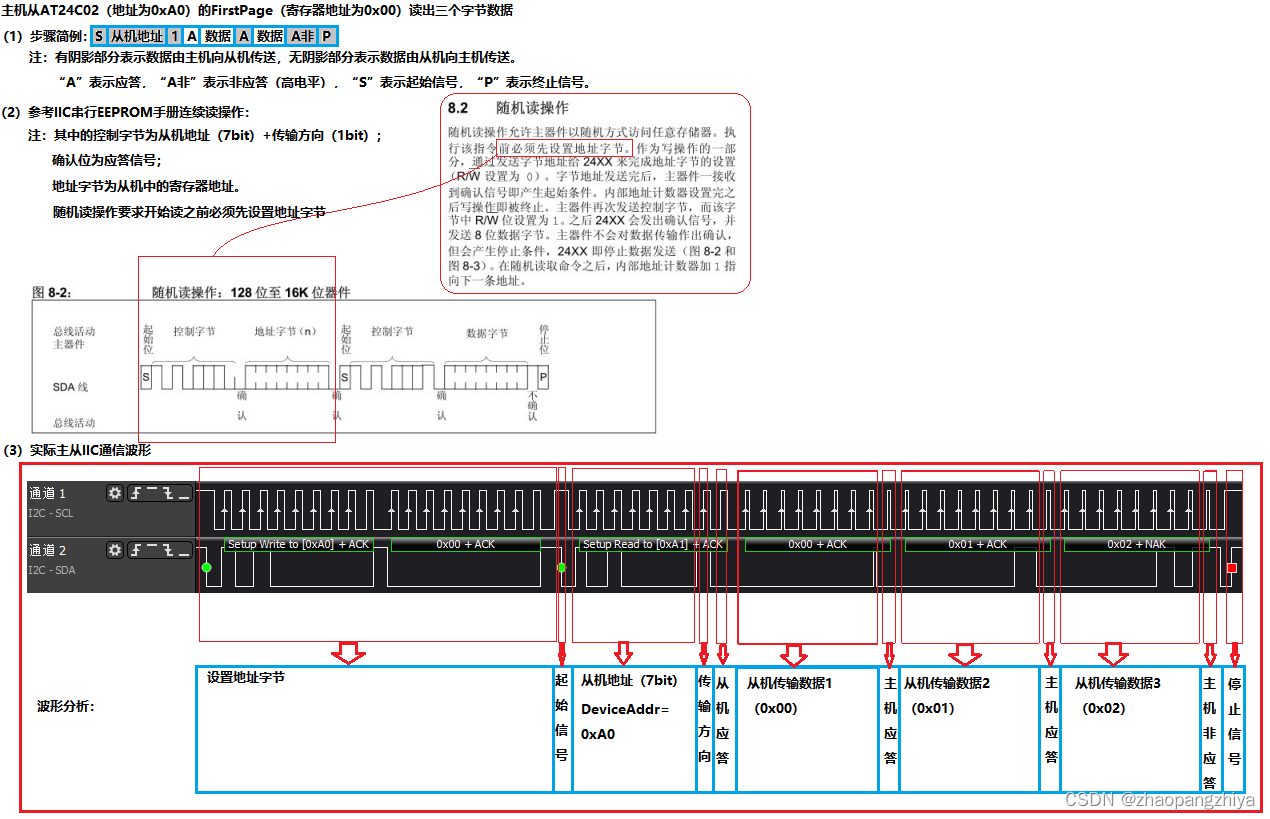

主机从从机读数据:

图6

IIC总线进行数据传送时,时钟信号为高电平期间,数据线上的数据必须保持稳定,只有在时钟线上的信号为低电平期间,数据线上的高电平或低电平状态才允许变化。

图7

五、总线仲裁

在多主的通信系统中。总线上有多个节点,它们都有自己的寻址地址,可以作为从节点被别的节点访问,同时它们都可以作为主节点向其它的节点发送控制字节和传送数据。但是如果有两个或两个以上的节点都向总线上发送启动信号并开始传送数据,这样就形成了冲突。要解决这种冲突,就要进行仲裁的判决,这就是I2C总线上的仲裁。

I2C总线上的仲裁分两部分:SCL线的同步和SDA线的仲裁。

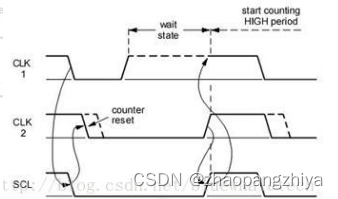

(1) SCL线的同步(时钟同步)

SCL同步是由于总线具有线“与”的逻辑功能,即只要有一个节点发送低电平时,总线上就表现为低电平。

当所有的节点都发送高电平时,总线才能表现为高电平。

图8

由于线“与”逻辑功能的原理,当多个节点同时发送时钟信号时,在总线上表现的是统一的时钟信号。这就是SCL的同步原理。

(2) SDA仲裁

SDA线的仲裁也是建立在总线具有线“与”逻辑功能的原理上的。

节点在发送1位数据后,比较总线上所呈现的数据与自己发送的是否一致。是,继续发送;否则,退出竞争。

SDA线的仲裁可以保证I2C总线系统在多个主节点同时企图控制总线时通信正常进行并且数据不丢失。总线系统通过仲裁只允许一个主节点可以继续占据总线。

(3) 仲裁过程

图9

DATA1和DATA2分别是主节点向总线所发送的数据信号;

SDA为总线上所呈现的数据信号,SCL是总线上所呈现的时钟信号。

当主节点1、2同时发送起始信号时,两个主节点都发送了高电平信号。这时总线上呈现的信号为高电平,两个主节点都检测到总线上的信号与自己发送的信号相同,继续发送数据。

第2个时钟周期,2个主节点都发送低电平信号,在总线上呈现的信号为低电平,仍继续发送数据。

在第3个时钟周期,主节点1发送高电平信号,而主节点2发送低电平信号。根据总线的线“与”的逻辑功能,总线上的信号为低电平,这时主节点1检测到总线上的数据和自己所发送的数据不一样,就断开数据的输出级,转为从机接收状态。

这样主节点2就赢得了总线,而且数据没有丢失,即总线的数据与主节点2所发送的数据一样,而主节点1在转为从节点后继续接收数据,同样也没有丢掉SDA线上的数据。因此在仲裁过程中数据没有丢失。

六、从机地址

IIC从地址有3种类型:分别是7位,8位和10位。产生这么多类型的原因是厂商采用的不同的地址约定。

(1)7位寻址

在7位寻址过程中,从机地址在启动信号后的第一个字节开始传输,该字节的前7位为从机地址,第8位为读写位,其中0表示写,1表示读。

图10:7位寻址。

I2C总线规范规定,标准模式I2C,从机地址为7位长,其次是读/写位。

第一个字节的头7 位组成了从机地址, 最低位(LSB) 是第8 位, 它决定了传输的方向。

第一个字节的第8位是“0” , 表示主机会写信息到被选中的从机;“1” 表示主机会向从机读信息, 当发送了一个地址后, 系统中的每个器件都在起始条件后将头7 位与它自己的地址比较, 如果一样, 器件会判定它被主机寻址, 至于是从机接收器还是从机发送器, 都由R/W 位决定。

任何I2C设备都必须遵循这个标准,USB2XXX传输的从机地址即为这7bit地址,不包含读写位,读写位会根据不同的函数自动添加进去。

(2)8位地址

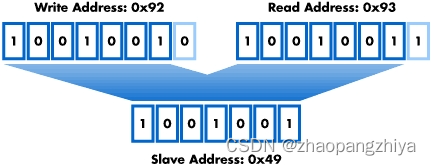

一些厂商在提供从机地址的时候说的是包含了读写位的8bit地址,比如他说写地址为0x92,读地址为0x93,如下图所示

图11: 8位寻址

如果是8位寻址的情况,需要将这个地址的前7bit提取出来,然后传入USB2XXX的接口函数即可,比如为0x49。

判断厂商提供的地址是7bit模式地址还是8bit地址模式的地址的方式:7bit地址模式下,地址的取值范围在0x07到0x78之间,若超过了这个范围,那么这个地址可能就是8bit地址。

图12:有效的7bit地址范围

(3)10位寻址

I2C总线的10bit寻址和7bit寻址是兼容的,这样就可以在同一个总线上同时使用7bit地址和10bit地址模式的设备,在进行10bit地址传输时,第一字节是一个特殊的保留地址来指示当前传输的是10bit地址。

图13:10bit地址寻址

在使用USB2XXX传输10bit地址模式的时候,只需要在初始化的时候配置为10bit地址模式(由第一个字节设置),然后再调用读写数据函数的时候传入正确的10bit地址即可。

七、IIC总线注意点

1. 进行数据传送时,在SCL为高电平期间,SDA线上电平必须保持稳定,只有SCL为低时,才允许SDA线上电平改变状态。并且每个字节传送时都是高位在前。

2. 对于应答信号,ACK=0时为有效应答位,说明从机已经成功接收到该字节,若为1则说明接受不成功。

3. 如果从机需要延迟下一个数据字节开始传送的时间,可以通过把SCL电平拉低并保持来强制主机进入等待状态。

4. 主机完成一次通信后还想继续占用总线在进行一次通信,而又不释放总线,就要利用重启动信号。它既作为前一次数据传输的结束,又作为后一次传输的开始。

5. 总线冲突时,按“低电平优先”的仲裁原则,把总线判给在数据线上先发送低电平的主器件。

6. 在特殊情况下,若需禁止所有发生在I2C总线上的通信,可采用封锁或关闭总线,具体操作为在总线上的任一器件将SCL锁定在低电平即可。

7. SDA仲裁和SCL时钟同步处理过程没有先后关系,而是同时进行的。

参考文章:

1.彻底搞懂IIC总线(5)I2C总线传输速度:彻底搞懂IIC总线(5)I2C总线传输速度

2.IIC常用速率:https://www.csdn.net/tags/NtTaggwsMTc3MzAtYmxvZwO0O0OO0O0O.html

678

678

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?