目录

1、ARMv7-A 协处理器

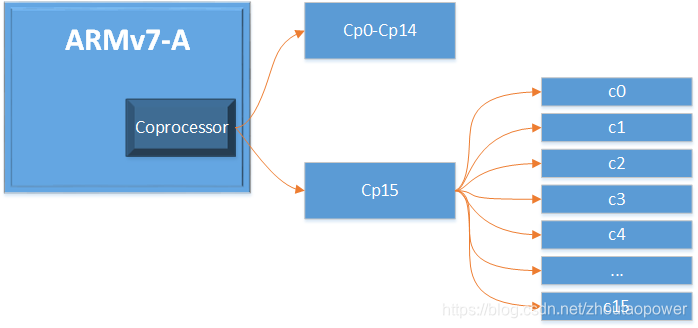

ARMv7-A 处理器除了标准的 R0~R15,CPSR,SPSR 以外,由于引入了 MMU、TLB、Cache 等内容,ARMv7-A 使用协处理器来对这些扩展来进行管理,ARMv7-A 支持 16 个协处理器,编号从 CP0~CP15,其中的 CP15 协处理器称之为系统控制协处理器,CP15 协处理器下的寄存器包含了 MMU、TLB、Cache等关键组件,其余的 CP0~CP14 有的控制Debug功能,有的控制 SIMD,有的控制浮点,咱们暂时只关注关键的 CP15;

2、CP15 协处理器

2.1、组成

CP15 协处理器由16个子寄存器组成,分别为 c0~c15,所以 CP15 的层次关系为:

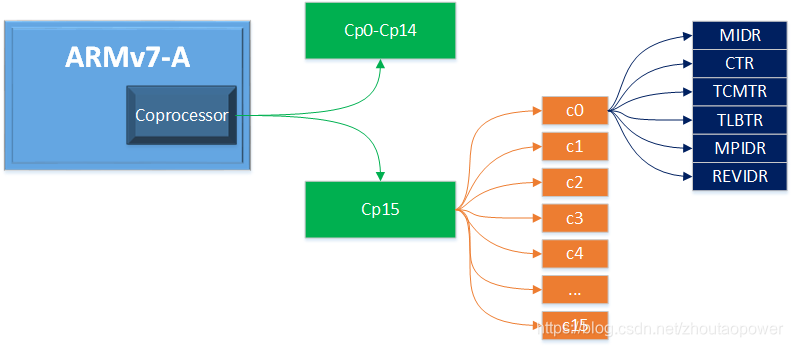

这里的 c0~c15 不是寄存器的含义,而是主(Primary Register)寄存器的意思,也就是每个 c0~c15 中,包含很多寄存器组:

比较常用的 c0~c15 的寄存器组织如下

| register | physical register | 描述 |

|---|---|---|

| c0 | MIDR | 主ID寄存器,用于记录厂商版本信息 |

| MPIDR | 多核处理器情况下,配置 Affinity | |

| c1 | SCTLR | 系统控制寄存器 |

| ACTLR | 辅助控制寄存器 | |

| CPACR | 协处理器访问控制寄存器,控制访问除了CP14和CP15的协处理器 | |

| SCR | 安全配置寄存器 | |

| c2 c3 | TTBR0 | 一级转换页表基址寄存器0 |

| TTBR1 | 一级转换页表基址寄存器1 | |

| TTBCR | 页表转换控制寄存器 | |

| c5 c6 | DFSR | 数据异常(Data Fault)状态寄存器 |

| IFSR | 指令异常(Instruction Fault)状态寄存器 | |

| DFAR | 数据异常(Data Fault)地址寄存器 | |

| IFAR | 指令异常(Instruction Fault)地址寄存器 | |

| c7 | predictor | cache及分支预测 |

| barrier | 数据及指令屏障 | |

| c8 | TLB | TLB操作 |

| c9 | performance monitors | 性能监视器 |

| c12 | VBAR | 非安全模式异常基址寄存器 |

| MVBAR | 安全模式异常基址寄存器 | |

| c13 | ASID | 上下文ID寄存器,软件线程ID寄存器 |

| c15 | CBAR | 配置基址寄存器,用于GIC(Generic Interrupt Controller)和定时器类型外设 |

所以,针对 CP15 协处理器相关的层次结构总结下来为(这里以c0为例,c1~c15同样有很多寄存器,每个寄存器都是 32bits 的):

2.2、访问指令

与 CPSR 类似,协处理器的访问是通过指定的汇编指令进行访问;常用的有 MCR/MRC 两条:

MRC: 将 CP15 协处理器中的寄存器数据读到 ARM 寄存器中。

MCR: 将 ARM 寄存器的数据写入到 CP15 协处理器寄存器中。

使用这两条指令,外加一些标准的指令,就可以实现读改写;

2.2.1、MCR

MCR 指令的格式如下:

MCR<c> <coproc>, <opc1>, <Rt>, <CRn>, <CRm>{, <opc2>}

其中:

coproc:访问协处理器的名字,取值范围从 p0~p15;

opc1:协处理器要执行的操作码,取值范围从 0~7;

Rt:ARM 的寄存器(比如 R0),要写入到指定协处理器寄存器的数据就保存在此寄存器中;

CRn:指定协处理器的目标寄存器;

CRm:协处理器中附加的目标寄存器或者源操作数寄存器,如果不需要附加信息就将 CRm 设置为 C0,否则结果不可预测;

opc2:可选的协处理器特定操作码,取值范围从 0~7,当不需要的时候要设置为 0;

2.2.2、MRC

MRC 指令的格式如下:

MRC<c> <coproc>, <opc1>, <Rt>, <CRn>, <CRm>{, <opc2>}

其中:

coproc:访问协处理器的名字,取值范围从 p0~p15;

opc1:协处理器要执行的操作码,取值范围从 0~7;

Rt:ARM 的寄存器(比如 R0),将指定协处理器寄存器的数据读在此 ARM Core 寄存器中;

CRn:指定协处理器的目标寄存器;

CRm:协处理器中附加的目标寄存器或者源操作数寄存器,如果不需要附加信息就将 CRm 设置为 C0,否则结果不可预测;

opc2:可选的协处理器特定操作码,取值范围从 0~7,当不需要的时候要设置为 0;

访问协处理器寄存器的指令已经写得很清楚,接下来就是如何来填这指令中的变量,这涉及到具体的协处理器的寄存器组织,我们使用最常用的 CP15 为例进行讲述;

2.3、Cp15 协处理器寄存器组成

不管是 MCR/MRC 指令,如果针对到具体的 Cp15 协处理器,coproc 字段填 p15,Rt 字段可以随便指定,暂时不管,那么就剩下 4 个变量:

{opc1、CRn、CRm、opc2};

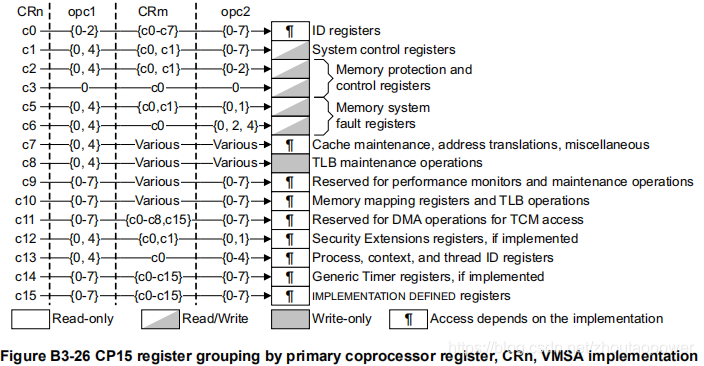

Cp15 协处理器的所有寄存器访问,都要依赖这几个值的组合达到访问的目的,前面说过整个 Cp15 的寄存器,分为 c0~c15,一个 16 个 Primary Regiser,再在每个 Primary Regiser 下面,又细分了很多具体的每个长度为 32bits 的寄存器,他们的整体组织结构为:

可以看到,Cp15 协处理器的 CRn 编号从 c0~c15,每个 Primary Regiser 都标记得有访问权限;后面的 opc1、CRm、opc2 的取值访问也都标记得清清楚楚;

那么下面将 c0~c16 每个展开看一下便可以清清楚楚看到他们怎么组织起来的,这样就可以知道如何使用汇编进行编码配置;

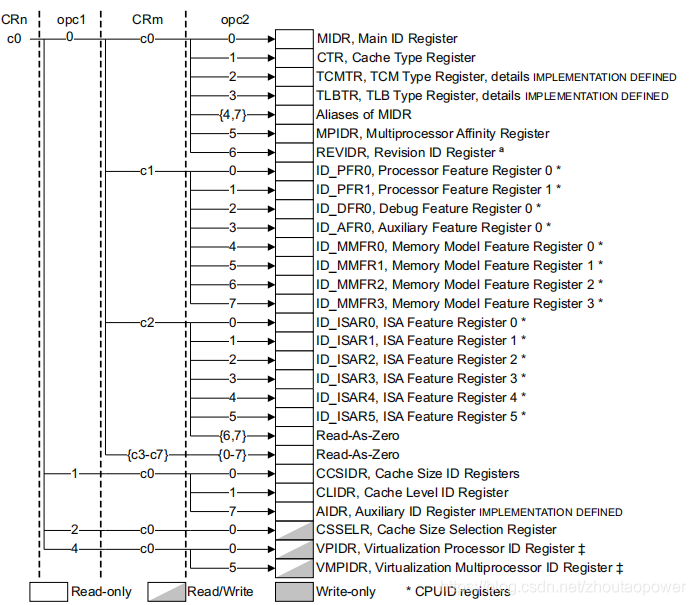

2.3.0、Cp15-c0 寄存器组成

c0 的寄存器组成如下:

访问每个寄存器的 {opc1、CRn、CRm、opc2} 写的清清楚楚;

主要是和 ID 相关的内容;

2.3.1、Cp15-c1 寄存器组成

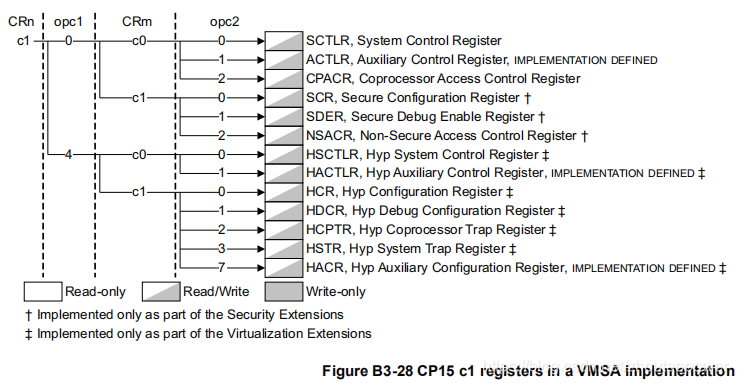

c1 的寄存器组成如下:

主要是和系统控制相关的配置;

2.3.2、Cp15-c2&c3 寄存器组成

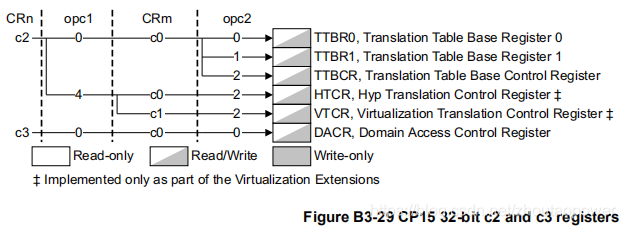

c2&c3 的寄存器组成如下:

主要是内存保护和控制相关的(MMU);

2.3.3、Cp15-c4 寄存器组成

Cp15 协处理器的 c4 寄存器为 Not used;

2.3.4、Cp15-c5&c6 寄存器组成

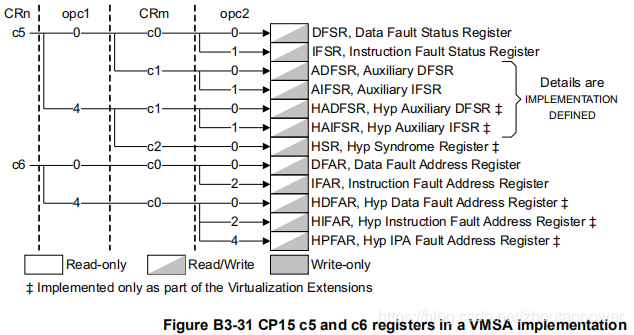

c5&c6 的寄存器组成如下:

主要是和 memory fault 相关的;

2.3.5、Cp15-c7 寄存器组成

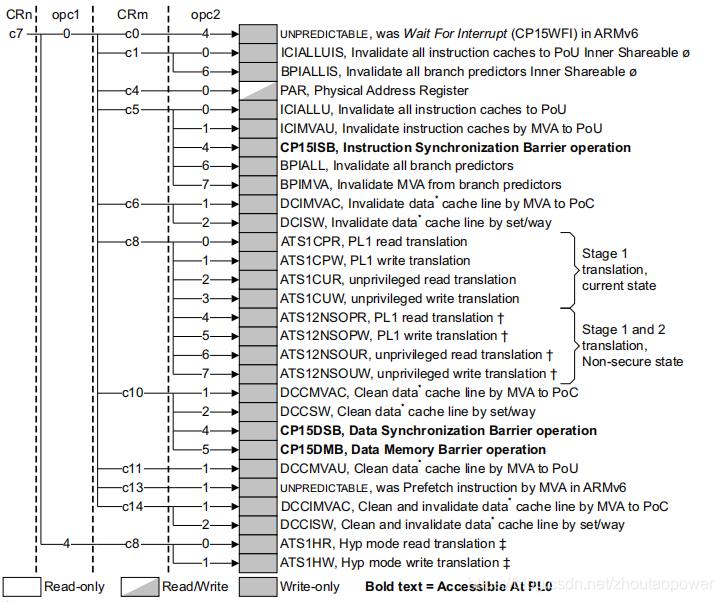

c7 的寄存器组成如下:

主要是和 Cache 相关的部分;

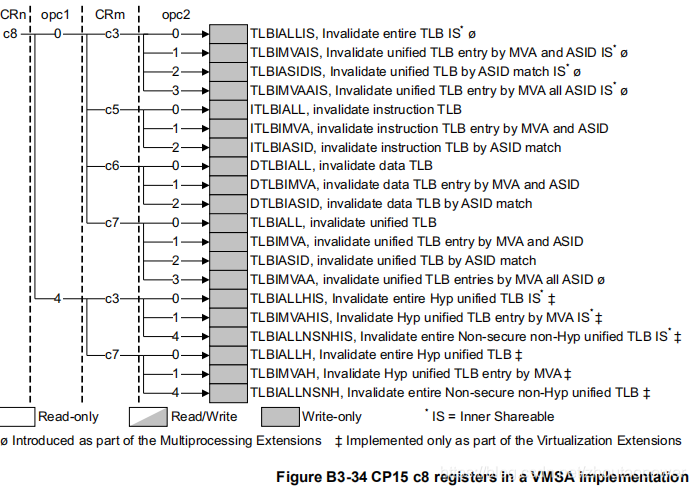

2.3.6、Cp15-c8 寄存器组成

c8 的寄存器组成如下:

主要是和 TLB 相关的;

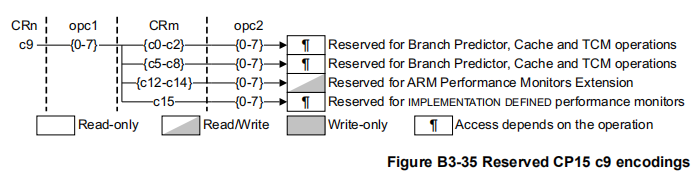

2.3.7、Cp15-c9 寄存器组成

c9 的寄存器是为 cache 和 TCM 预留的;

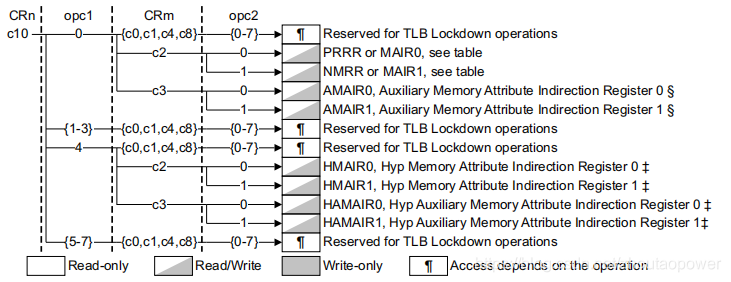

2.3.8、Cp15-c10 寄存器组成

c10 的寄存器是为内存重映射和 TLB 控制:

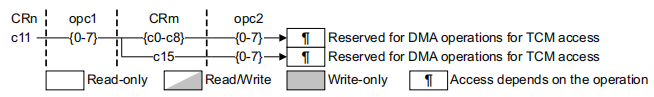

2.3.9、Cp15-c11 寄存器组成

c11 的寄存器是为 TCM DMA 预留:

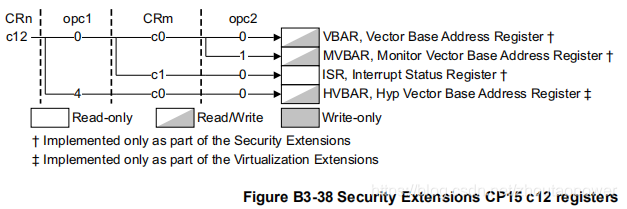

2.3.10、Cp15-c12 寄存器组成

c12 的寄存器是为安全扩展的:

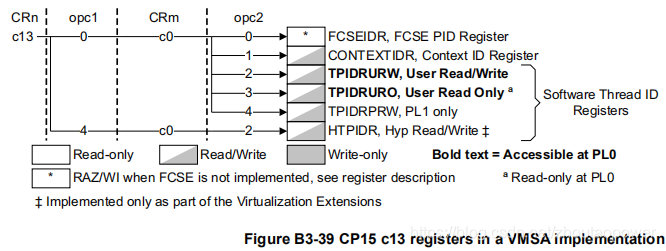

2.3.11、Cp15-c13 寄存器组成

c13 的寄存器是为进程,上下文和线程 ID 的:

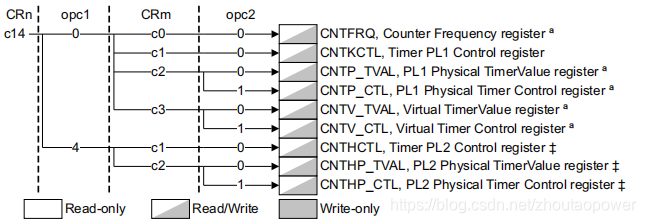

2.3.12、Cp15-c14 寄存器组成

c14 的寄存器是为通用 Timer 预留的:

2.3.13、Cp15-c15 寄存器组成

c15 的寄存器是 IMPLEMENTATION DEFINED 的,不管他:

参考文献:

ARM体系架构—ARMv7-A协处理器_liyuewuwunaile的博客-CSDN博客

5685

5685

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?