一、SoundWire 概述:

SoundWire是MIPI提出的一个接口协议,与I2S,HDA一样,是音频接口协议。其特点是:

1. 通过一个 two-pin接口来传输音频data,控制命令等。

2. 其clock scaling 和可选的多条data lane给予data频率更高的灵活度以匹配系统要求。

3. 因为用了DDR(double data rate)数据传输方式,因此可以使用更低的时钟频率和功耗。

4. 单个master可以连接最多11个slave。

5. 支持slave to slave的数据传输方式。

6. 支持多负载传输机制(multiple payload transport mechanisms),包括同步或者异步的音频流。

7. 帧大小可以灵活配置,payload具有复杂性,支持PCM和PDM音频流。

8. 低延时,高采样率。

二、SoundWire 物理层接口(PHY):

SoundWire接口使用两根信号做设备之间的连接:

• Clock – 从master发送到全部slave的时钟信号。

• Data – 可以被所有设备驱动的data信号,并且可以配置没有设备驱动它的时候的空载值。

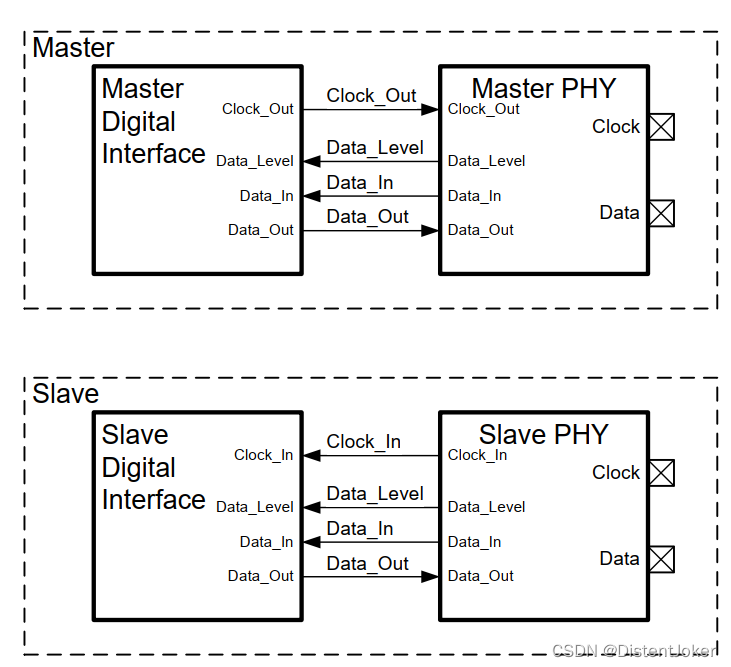

SoundWire 设备(device)与PHY:

上图为SoundWire的master interface和slave interface,内部的digital interface负责传送payload,command等,而PHY负责提供本设备与其他SoundWire设备的物理连接(两线接口)。

Data Signaling and Bitslots

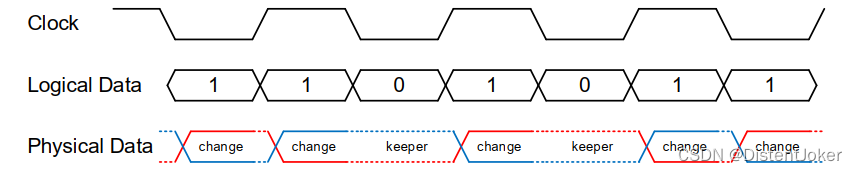

1. SoundWire采用DDR(double data rate)进行数据传输。1个bit在上升沿的时候被驱动,并且在下降沿被采样,下一个bit在下降沿被驱动,在上升沿被采样。数据可以在上升沿和下降沿被采样,所以数据传输频率时时钟的两倍。

2. SoundWire帧内每一个bit叫做bitslot,帧内第一个bitslot叫bitslot[0],后面以此类推,bitslot[n]紧接着bitslot[n-1],所以bitslot[0]时紧跟着上一帧的最后一个bitslot。

3. Bitslot里面的的值,都是由0个,1个,甚至是多个SoundWire设备提供的。如果一个设备提供了这个bitslot的值,我们称为这个设备own了这个bitslot(这个设备就叫the owner of the Bitslot)。

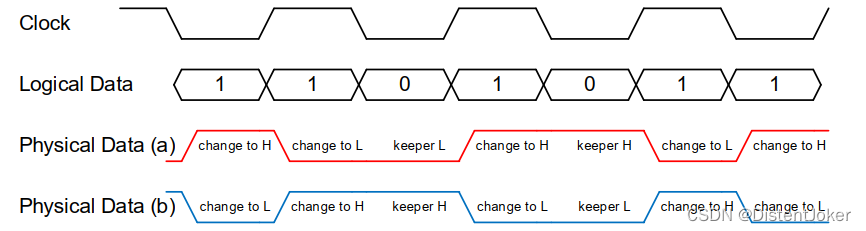

SoundWire采用改进的NRZI进行数据编码(这段不是很懂)

NRZI编码:

下图为NRZI编码方式,当data值发生变化时,表示为1,当data值不变时,表示为0,如果要传输“1101011”,则最终data的值为“HLLHHLH”或者“LHHLLHL”,前者还是后者,取决于传输信号前,data的状态。

改进的NRZI编码:

SoundWire采用改进的NRZI编码,意味着如果设备想从SoundWire总线上抓取数据作为自己的input data(例如Bitslot[n]),则要根据时钟,采样两个点(例如Bitslot[n-1]和Bitslot[n])进行对比。同样,如果设备想从SoundWire总线上输出data(例如Bitslot[n]),则需要采样当前data的值(例如Bitslot[n-1])来确认输出的data应该是什么值。

这个改进的NRZI的不同点在于,只有在逻辑“1”的时候,data output信号被主动驱动起来,逻辑“0”的时候,data信号可以被被动驱动起来。

这样做有两个好处:

1. 如果当前的bitslot没有owner,或者是由于某些data原因没有被驱动,这个master的bus-keeper会让data保持逻辑0状态,这有利于检查出丢失的设备和某些错误配置;

2. 允许同一个bitslot拥有两个甚至多个owner,多个owner之间的关系是“线或”(wire-ORed),意味着一个owner要输出逻辑1,对于其他逻辑0拥有更高的优先级。

三、帧结构与Control Word:

帧结构

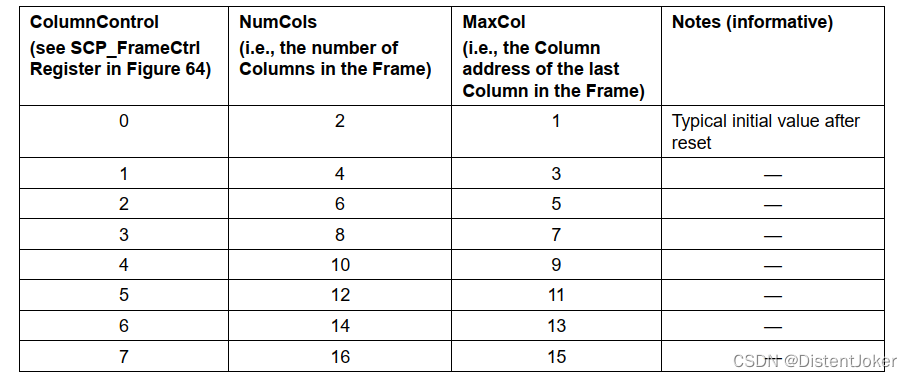

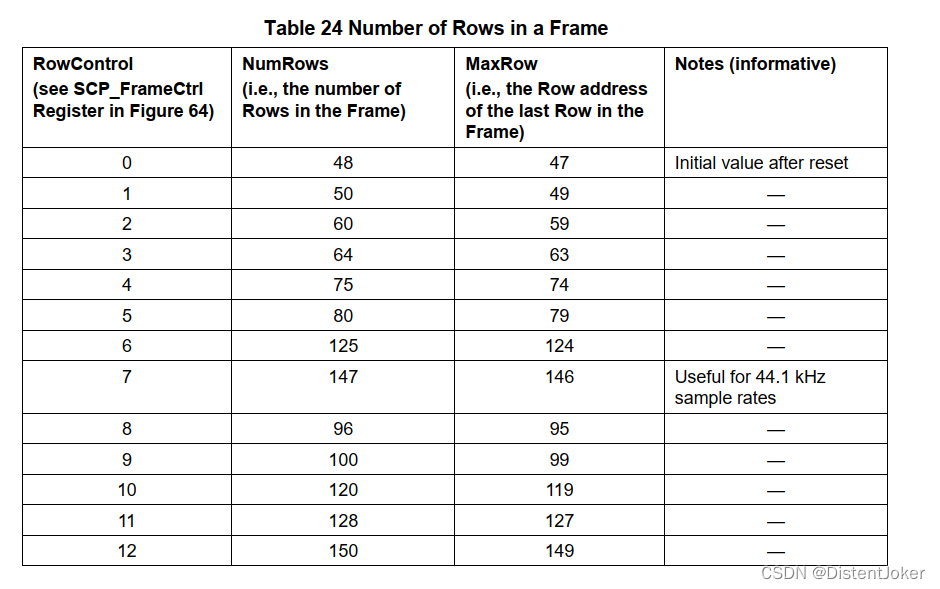

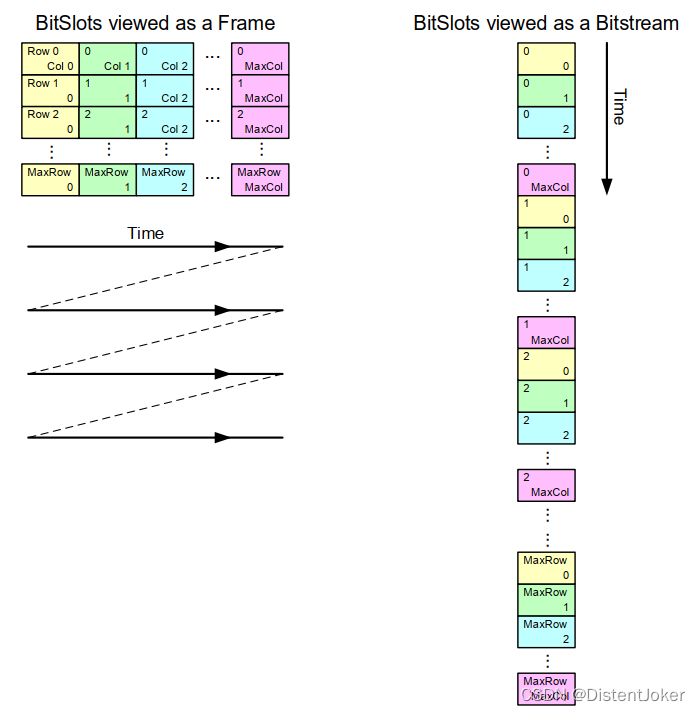

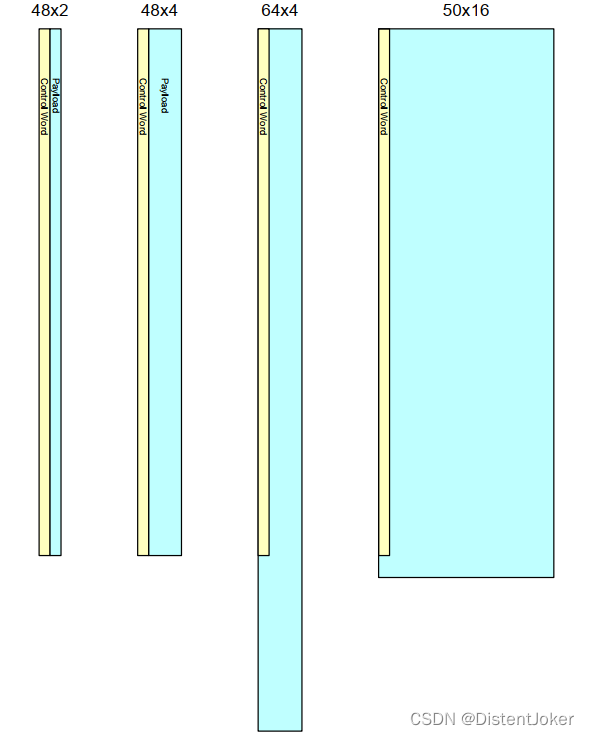

SoundWire的帧可以看作成一个二维数组,由比特流(bitstream)的行和列组成。其中,行的值是48~256里面的几个值,同样,列是2~16。这些master设备可以通过配置寄存器来决定的,同时这些帧的属性变量是动态可配的。初始的帧大小就是96个bitslot(48行,2列)。

配置列数:

配置行数:

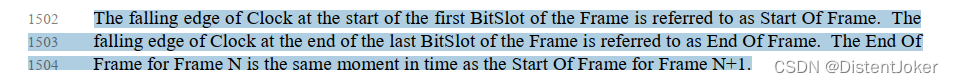

每一帧的第一个bitslot开始于时钟的下降沿(第一个output data生成),并且结束于时钟的上升沿(最后一个bitslot被采样)。因为列数永远是偶数,所以下一帧的第一个bitslot也总是在时钟下降沿开始。

但是SPEC说的一帧的最后一个bitslot结束和下一帧的开始bitlost是同一个moment,这个不太理解,我的理解是第N帧的结束和第N+1帧的开始,应该是相差一个周期的。

下图为帧结构的图:

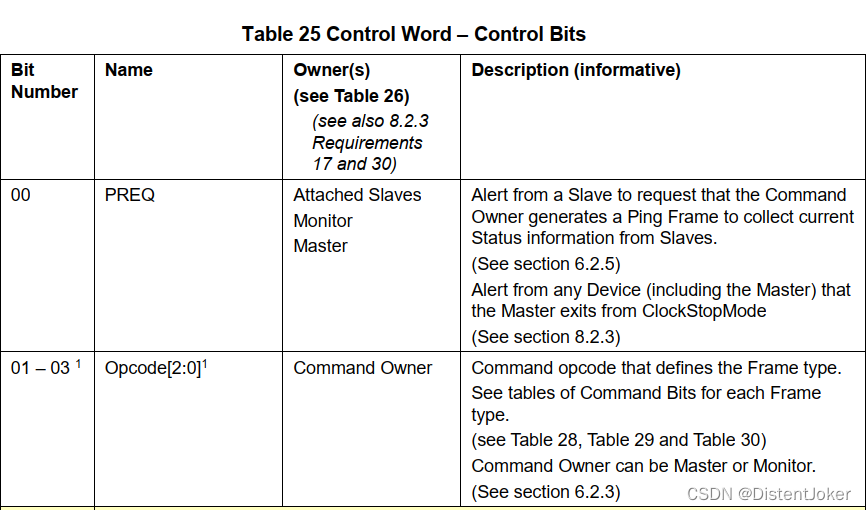

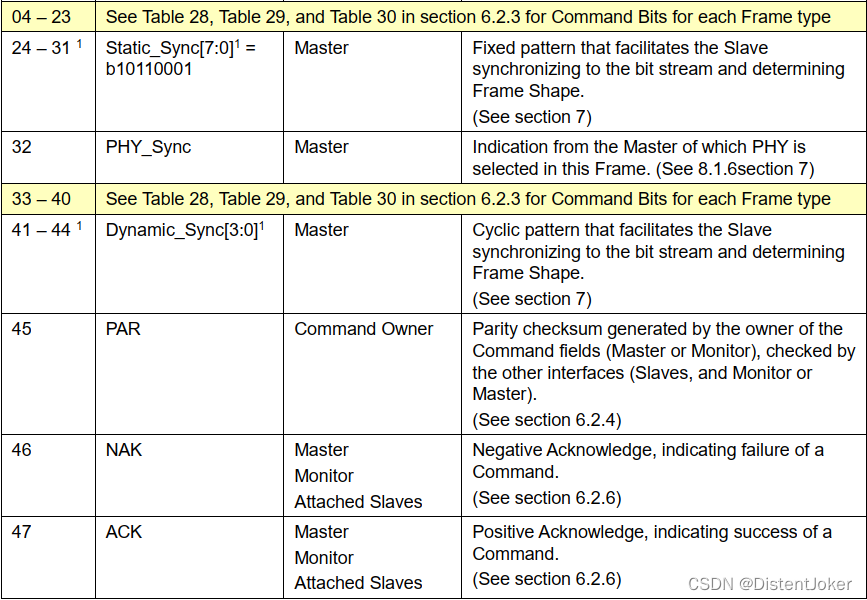

Control Word

在帧结构中,第一列的前48个bitslot为control word({row[0],col[0]},{row[0],col[1]}......{row[0],col[48]}),由于bitstream传输是一行一行(row)传输的,因此control word在bitstream上是不连续的。前48行中,每行第一个为control word的一部分,该行剩下的bitslot都是data payload。下图为control word在帧结构中的位置。

在control word里面的bitslot被分配成以下两种功能:

• Control BitSlot(20):负责一些低层级的功能,例如帧同步等。

• Command BitSlot(28):负责帮助当前的command owner传输command给其他设备,也负责接收respond给command owner。

Control Word Fields

1. PREQ(Ping Request):

一个或者多个Slave用于通知Owner,其需要在Ping command 中上报一些状态。因为多个slave的data pin是"线与"关系,所以只要有一个slava拉起了PREQ,Owner收到的这一帧的PREQ都会被拉起来。当owner收到这个PREQ时,会在接下来的32帧内发送ping command去读取slave的状态。在第N帧内发生类似中断等信息需要发送PREQ时,已经晚于当前帧发送PREQ的时机了,因此会在N+1帧甚至N+2帧的时候才能发出PREQ,一旦拉起了PREQ,slave会一直拉起来直到其能成功收到来自Owner的ping command。

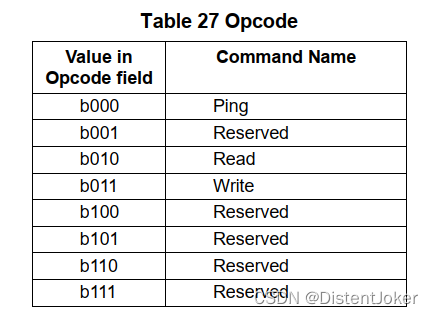

2. Opcode:

Opcode由3个bit组成,command field的组成由Opcode来决定。Opcode由Master或者Monitor接口(command owner), slave接口接收到不同的Opcode和对应的command field之后会做相应的动作。Opcode有3种:

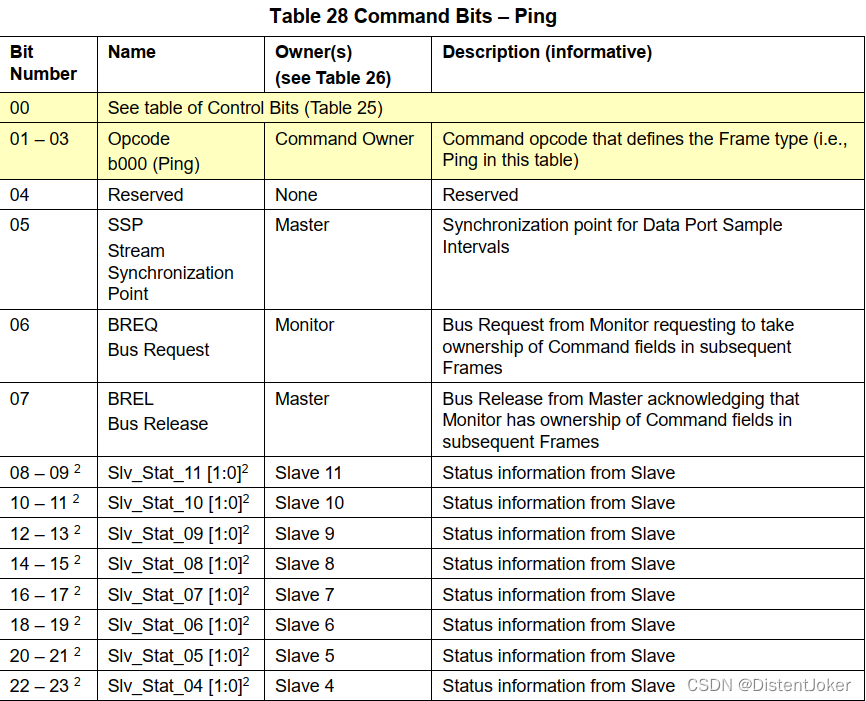

• Ping:让总线上的所有slave返回状态。

• Write:Command Owner给一个或者多个设备中一个或者多个寄存器写一个8 bit 的值。

• Read:Command Owner从一个或者多个设备中一个或者多个寄存器读一个8 bit 的值。

当Opcode为Ping的时候,command field如下:

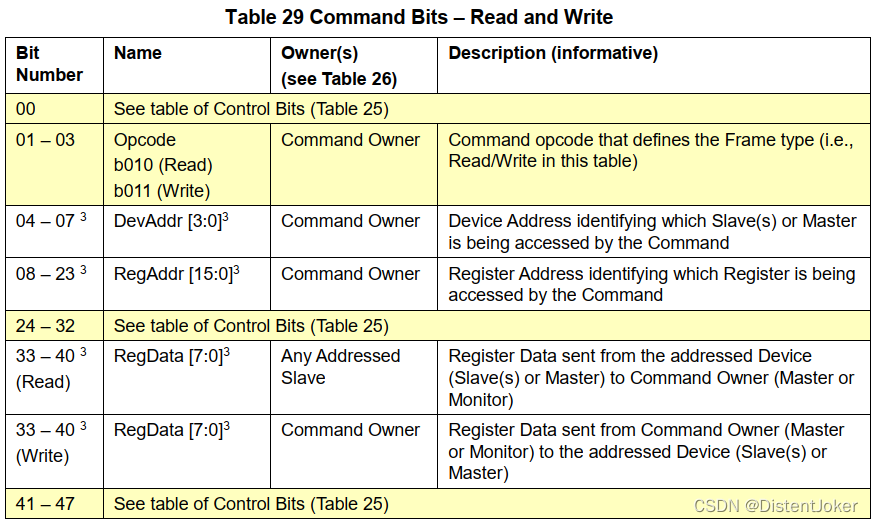

当Opcode为Write或者Read的时候,command field如下:

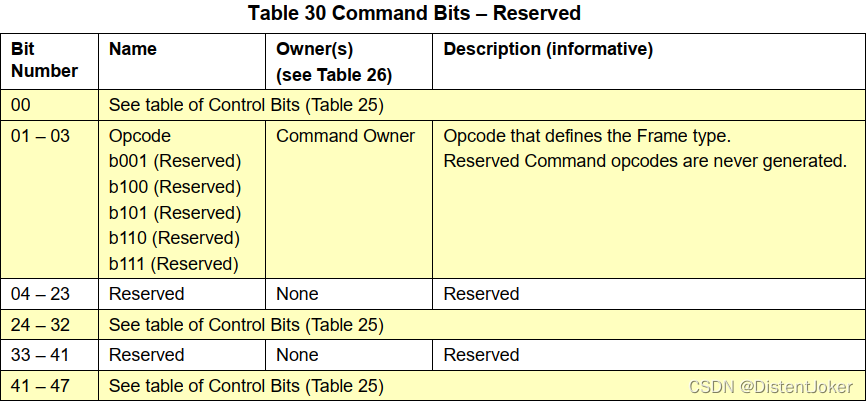

当Opcode为Reserved的时候,command field如下:

3. Static Synchronization

Static Synchronization是一个固定的8bit的值为 b'10110001,由master产生,slave接收,并以此来维持帧同步。

4. PHY Synchronization

PHY Synchronization为1bit,由master生成,通知slave当前的PHY属于什么状态:0代表普通的PHY,1代表High-PHY。当Slave收到这个值的时候,会把PHY_Sync值写到对应的寄存器中。

5. Dynamic Synchronization

Dynamic Synchronization为4个bit,为连续15个帧的一个动态码。由于只看Static Synchronization的话,比特流可能刚好与Static Synchronization一致,导致SoundWire总线进入假连接状态,加入Dynamic Synchronization后能更好的解决这个问题。Dynamic Synchronization的值来自于4-bit LFSR(linear feedback shift register)寄存器,其通过一个PRBS (pseudo-random binary sequence) 产生器生成出来。LFSR初始值为b’1111。

本文详细介绍了MIPI SoundWire接口协议,包括其特点、物理层接口、帧结构、控制字、帧同步、系统控制及命令。SoundWire提供两线接口传输音频数据,支持DDR数据传输,具有灵活的帧大小配置,适用于音频设备间通信,具有低延迟和高采样率。文章深入探讨了数据传输方式、帧结构中的Control Word以及如何进行设备同步和命令交互,适合硬件工程师和音频系统开发者阅读。

本文详细介绍了MIPI SoundWire接口协议,包括其特点、物理层接口、帧结构、控制字、帧同步、系统控制及命令。SoundWire提供两线接口传输音频数据,支持DDR数据传输,具有灵活的帧大小配置,适用于音频设备间通信,具有低延迟和高采样率。文章深入探讨了数据传输方式、帧结构中的Control Word以及如何进行设备同步和命令交互,适合硬件工程师和音频系统开发者阅读。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

504

504

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?