DAY17. 中断控制器

如果出现图片无法查看可能是网络问题,我用的GitHub+图床保存的图片,可以参考我另外一篇文章GitHub的使用方法含网络问题解决

GitHub使用教程含网络问题_github加速器_肉丸子QAQ的博客-CSDN博客

相关作业和资料已上传,请在主页自行查看

1. 中断控制器

所有中断信号是要先经过中断控制器,通过中断控制器处理后再给cpu

-

多个中断同时产生时可对这些中断挂起排队,然后按照优先级依次发送给CPU处理

-

可以为每一个中断分配一个优先级 n

-

一个中断正在处理时若又产生其它中断,可将新的中断挂起,待CPU空闲时再发送

-

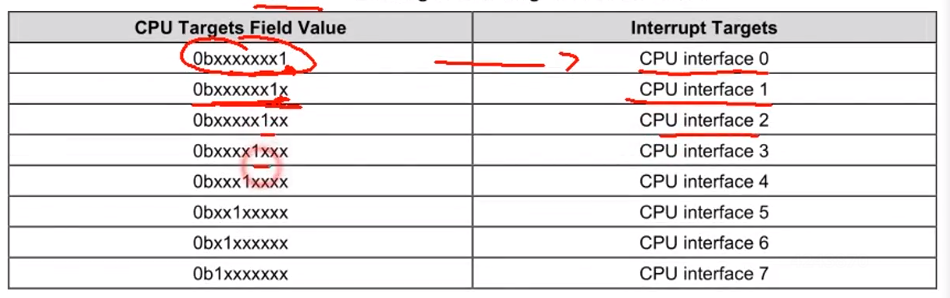

可以为每一个中断选择一个CPU处理

-

可以为每一个中断选择一个中断类型(FIQ或IRQ)

-

CPU接收到中断信号后并不能区分是哪个外设产生的,此时CPU可查询中断控制器 来获取当前的中断信号是由哪个硬件产生的,然后再进行对应的处理

-

可以打开或禁止每一个中断 … …

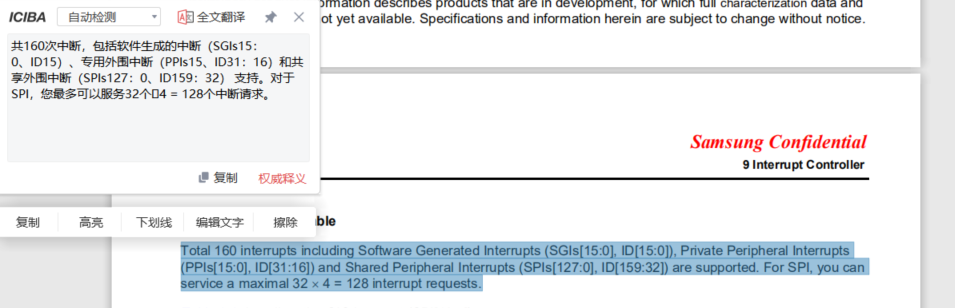

2. Exynos4412下的中断控制器

主要用到SPI中断

-

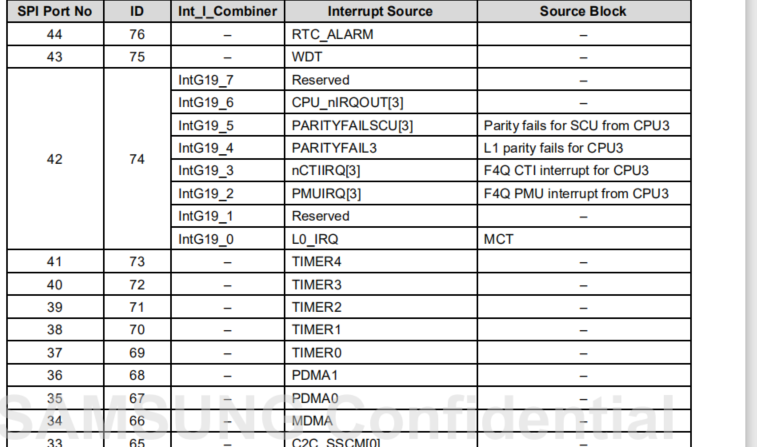

SPI:中断号范围

[159:32] -

通过查表可以知道不同的功能对应不同中断号

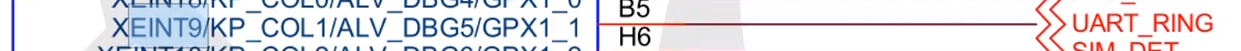

- XEINT表示外部中断,按键是在这个引脚口,外部中断9

- 中断相关的寄存器非常多,因为这块板子有160个中断口

3. 中断控制器寄存器详解

在拥有系统后,相关的中断代码和寄存器都会给,现在不涉及系统,只讲这次实验相关的寄存器

ICDDCR 寄存器

-

0 = GIC忽略所有外围中断信号,并且不将挂起的中断转发到CPU接口。

-

1 = GIC监控外围中断信号,并将等待的中断转发到 CPU接口。

中断控制器的总开关

ICDISER_CPU寄存器

对于SPI和PPI,对于每个位:

-

读取)0=禁用相应的中断。1.=启用相应的中断。

-

写)0=没有影响。1.=启用相应的中断。子序列 t读取的这个位返回的值为1。

设置160个中断的打开和关闭,每一位的0和1分别对应一个中断的关闭和开始

一共需要5个寄存器才够160个中断

ICDIPTR_CPU寄存器

设置160个中断信号处理的CPU

哪一位写1代表哪个CPU,这个板卡下只有4个CPU,高八位没用

这类寄存器需要40个才能控制160个中断

一个寄存器管理4个中断

例如:6号中断交给CPU2处理

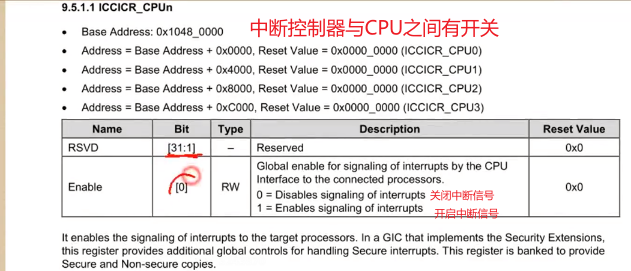

ICCICR_CPUn寄存器

中断控制器与CPU之间的开关

4. 中断控制器编程

设置GPIO和中断控制器,剩余内容在下节,本节内容都是外部产生中断送给CPU,我们还需要进行异常处理

#include "exynos_4412.h"

void Delay(unsigned int Time)

{

while(Time--);

}

int main()

{

//一、*外设层次 - 让外部的硬件控制器产生一个中断信号发送给中断控制器*/

//1. 将GPX1_1设置成中断功能

GPX1.CON = GPX1.CON | (0xF << 4) //置1或 置0与 多位先清零后置位

//2. 设置GPX1_1中断触发方式

EXT_INT41_CON = EXT_INT41_CON & (~(0x7 << 4)) | (0x2 << 4);

//3. 使能GPX1_1中断功能

EXT_INT41_MASK = EXT_INT41_MASK & (~(1 << 1));

//4.EXT_INT41_PEND寄存器初始化不用自己写会自动置一,但是在处理完中断后需要手动清零

/*二、中断控制器层次 -* 让中断控制器接收外设产生的中断信号并对其进行管理然后再转发给CPU处理*/

//1./*全局使能中断控制器使其能接收外设产生的中断信号并转发到CPU接口*/

ICDDCR = ICDDCR |1; //将第零位置1

/*2.在中断控制器中使能57号中断,使中断控制器接收到57号中断后能将其转发到CPU接口*/

ICDISER.ICDISER1 = ICDISER.ICDISER1 | (1 << 25);

/*3.选择由CPU0来处理57号中断*/

ICDIPTR.ICDIPTR14 = ICDIPTR.ICDIPTR14 & (~(0xff << 8)) | (0x01 << 8);

/*4.使能中断控制器和CPU0之间的接口,使中断控制器转发的中断信号能够到达CPU0*/

CPU0.ICCICR = CPU0.ICCICR | 1;

return 0;

}

5. 作业

1.简述中断控制器的主要作用

多个中断同时产生时可对这些中断挂起排队,然后按照优先级依次发送给CPU处理

可以为每一个中断分配一个优先级

一个中断正在处理时若又产生其它中断,可将新的中断挂起,待CPU空闲时再发送

可以为每一个中断选择一个CPU处理

可以为每一个中断选择一个中断类型(FIQ或IRQ)

CPU接收到中断信号后并不能区分是哪个外设产生的,此时CPU可查询中断控制器 来获取当前的中断信号是由哪个硬件产生的,然后再进行对应的处理

可以打开或禁止每一个中断 … …

1027

1027

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?