【计算机硬件系统设计(华科)——MIPS CPU(Logisim 实现)】

前言

前文已经介绍了运算器、存储器以及单周期CPU的设计,本章将继续对三级时序(包括定长指令周期与变长指令周期)CPU进行分析与展示。

定长指令周期三级时序CPU

三级时序是指时序部件信号由周期、节拍和工作脉冲三级时序组成,为指令执行产生时序信号,控制部件根据组合条件形成相应的控制逻辑,再与时序信号组合产生所需的控制信号。

控制器设计

时序部件设计

设计时序发生器以循环产生周期电位、节拍电位,控制时序信号的产生。

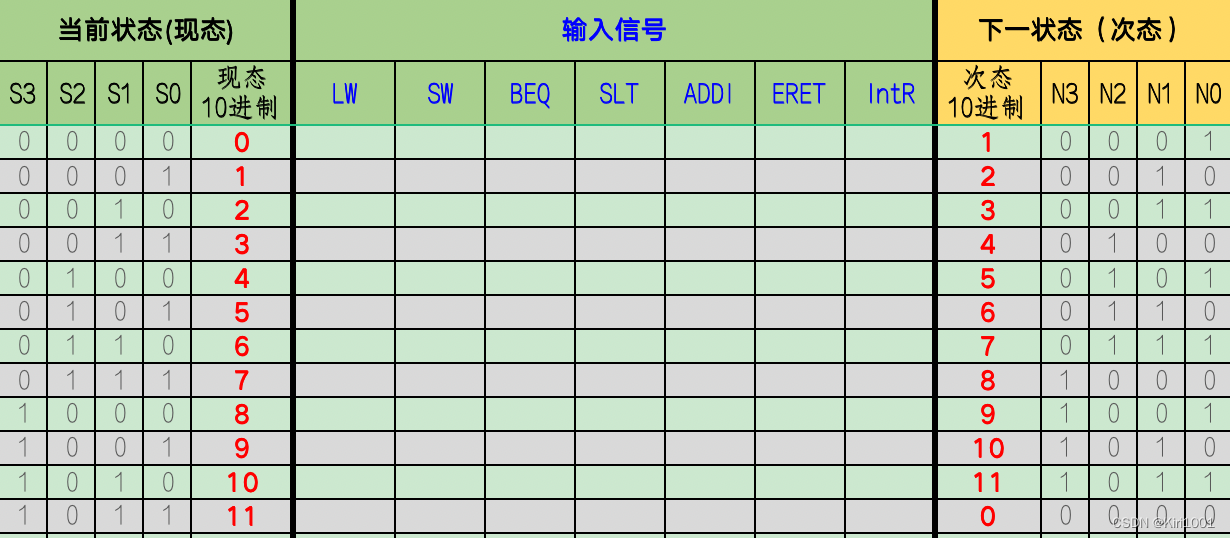

根据指令周期流程图可将一条指令执行的周期划分为取指周期、计算周期(计算数据在存储器中的地址)以及执行周期。以所需节拍最多的取指周期为准,共需要3(3个周期)*4(4个节拍)=12个状态。

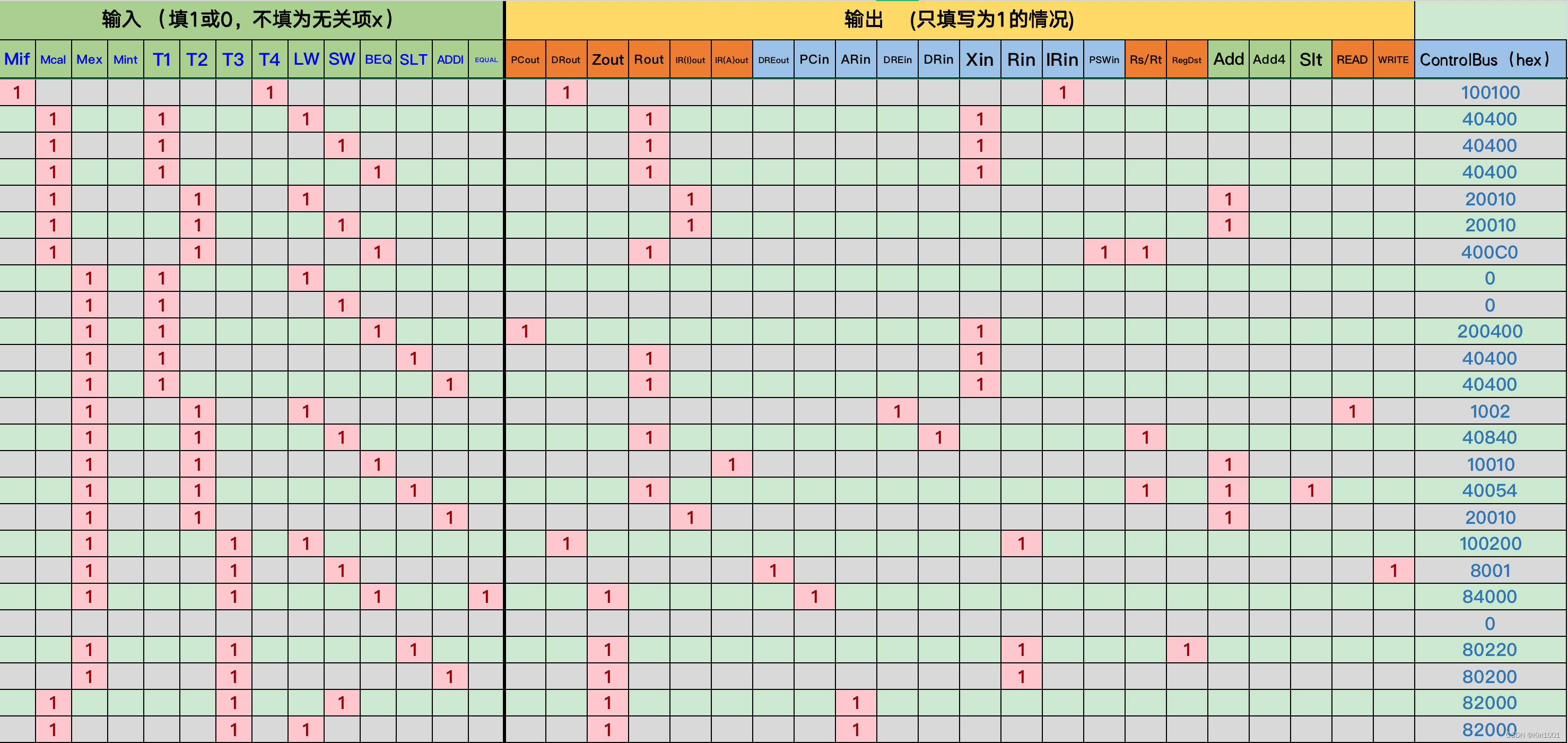

控制信号设计

使用硬布线设计方式设计控制器,通过时序发生器产生的时序信号,以及指令译码器根据具体指令形成的指令

本文详细介绍了三级时序CPU的设计,包括定长和变长指令周期的控制器和时序部件设计,以及中断处理机制。在定长指令周期中,控制器和译码器设计确保了指令执行的有序进行;变长指令周期减少了空操作,提升了性能。中断处理机制涉及中断请求、优先级仲裁、现场保护和恢复,确保了系统的响应能力。

本文详细介绍了三级时序CPU的设计,包括定长和变长指令周期的控制器和时序部件设计,以及中断处理机制。在定长指令周期中,控制器和译码器设计确保了指令执行的有序进行;变长指令周期减少了空操作,提升了性能。中断处理机制涉及中断请求、优先级仲裁、现场保护和恢复,确保了系统的响应能力。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

698

698

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?