Cadence绘制好原理图后,需生成网表给PCB工程师Layout。但在这个过程中也会遇到各种问题,如何排除这些问题就显得很有意思。

最近接手一个历史原理图修改,完成后编译和DRC,无错误报出,但在生成网表时出现问题

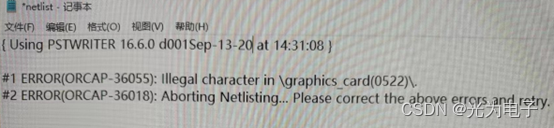

1、生成网表报错,打开网表文件提示出现非法字符错误。

出现上述问题,根据以往的经验判断应该是原理图封装出现了非法字符,或者是封装库路径中出现非法字符。如图所示提示,并不清楚是那一页原理图中的某一个器件,处理该问题思路:

1) 逐一排查每一页原理图,生成网表,判断问题出现在那一页;

2) 查看器件封装路径是否有非法字符;

3) 定位某一页原理图后,逐一删除可疑元器件,生成网表定位某一器件;

4) 找到某一器件后,更换或重新更改封装。

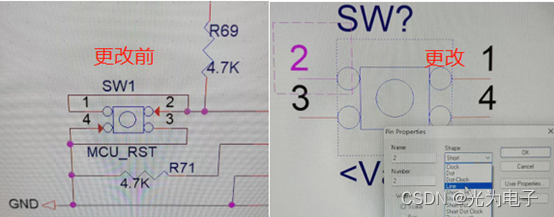

经过耐心查找,最终查询到是按键封装问题,再次更改封装,生成网表成功。

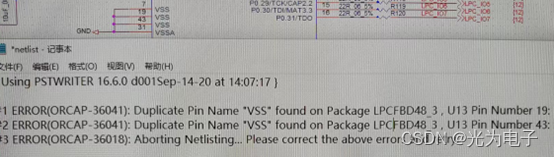

2、生成网表时,提示某一网络出现重名。

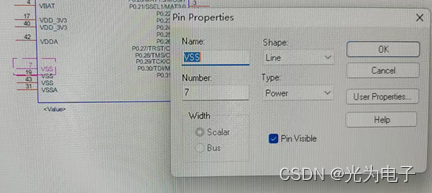

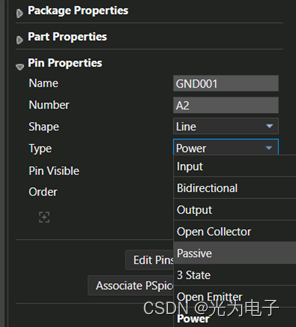

出现上图问题原因,封装建立时相同属性网络引脚没有设置,或是用符号区别。解决思路:

1) 进入封装编辑,将VSS引脚属性更改为Power;

2) 编辑封装,将重复引脚用顺序区别。

总结,绘制封装时按规则构建,避免后期排查问题的时间;排查问题勿急躁,有问题出现,必然有引起的原因,分析引起的原因,从大范围逐一排查,缩小排查区域,找到问题产生的原因并解决。

感悟,工程师的日常,不断在排查问题,分析问题,解决问题,这个过程充满辛酸,但也有满满成就感,有自我价值的体现。光为能力不是最强的,解决问题思路也不是最好的,条条道路通罗马,适合自己的是最便捷、最高效的。光为只为分享平时遇到问题时如何排查,解决方法。

工具软件使用中会遇到各种问题,记录分享排查过程,只为分享解决问题思路,提高解决问题效率,如若有意,点赞分享!

Cadence生成网表失败排查思路

【Cadence生成网表失败排查思路】

于 2022-09-19 07:48:49 首次发布

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?