对I2C总线的时钟同步和总线仲裁的深入理解

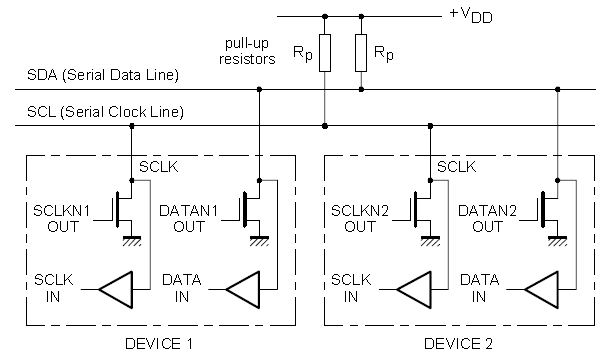

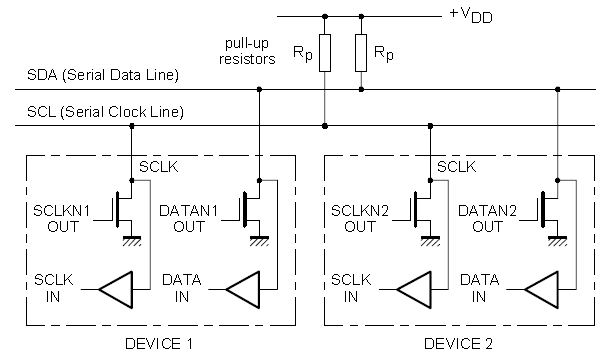

每一个IIC总线器件内部的SDA、SCL引脚电路结构都是一样的,引脚的输出驱动与输入缓冲连在一起。其中输出为漏极开路的场效应管、输入缓冲为一只高输入阻抗的同相器[1]。这种电路具有两个特点:

①由于SDA、SCL为漏极开路结构,借助于外部的上拉电阻实现了信号的“线与”逻辑;

②引脚在输出信号的同时还将引脚上的电平进行检测,检测是否与刚才输出一致。为 “时钟同步”和“总线仲裁”提供硬件基础。

I2C总线接口内部结构

本文深入探讨了I2C总线的时钟同步和总线仲裁机制。通过引脚的漏极开路设计,I2C设备实现了线与逻辑,确保了时钟同步和冲突的解决。在时钟同步中,最长低电平时间决定了总线速度;在总线仲裁中,遵循低电平优先原则,先发送0的设备控制总线。这种设计使得I2C总线能够在多个主设备间高效、稳定地工作。

本文深入探讨了I2C总线的时钟同步和总线仲裁机制。通过引脚的漏极开路设计,I2C设备实现了线与逻辑,确保了时钟同步和冲突的解决。在时钟同步中,最长低电平时间决定了总线速度;在总线仲裁中,遵循低电平优先原则,先发送0的设备控制总线。这种设计使得I2C总线能够在多个主设备间高效、稳定地工作。

每一个IIC总线器件内部的SDA、SCL引脚电路结构都是一样的,引脚的输出驱动与输入缓冲连在一起。其中输出为漏极开路的场效应管、输入缓冲为一只高输入阻抗的同相器[1]。这种电路具有两个特点:

①由于SDA、SCL为漏极开路结构,借助于外部的上拉电阻实现了信号的“线与”逻辑;

②引脚在输出信号的同时还将引脚上的电平进行检测,检测是否与刚才输出一致。为 “时钟同步”和“总线仲裁”提供硬件基础。

I2C总线接口内部结构

431

431

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?