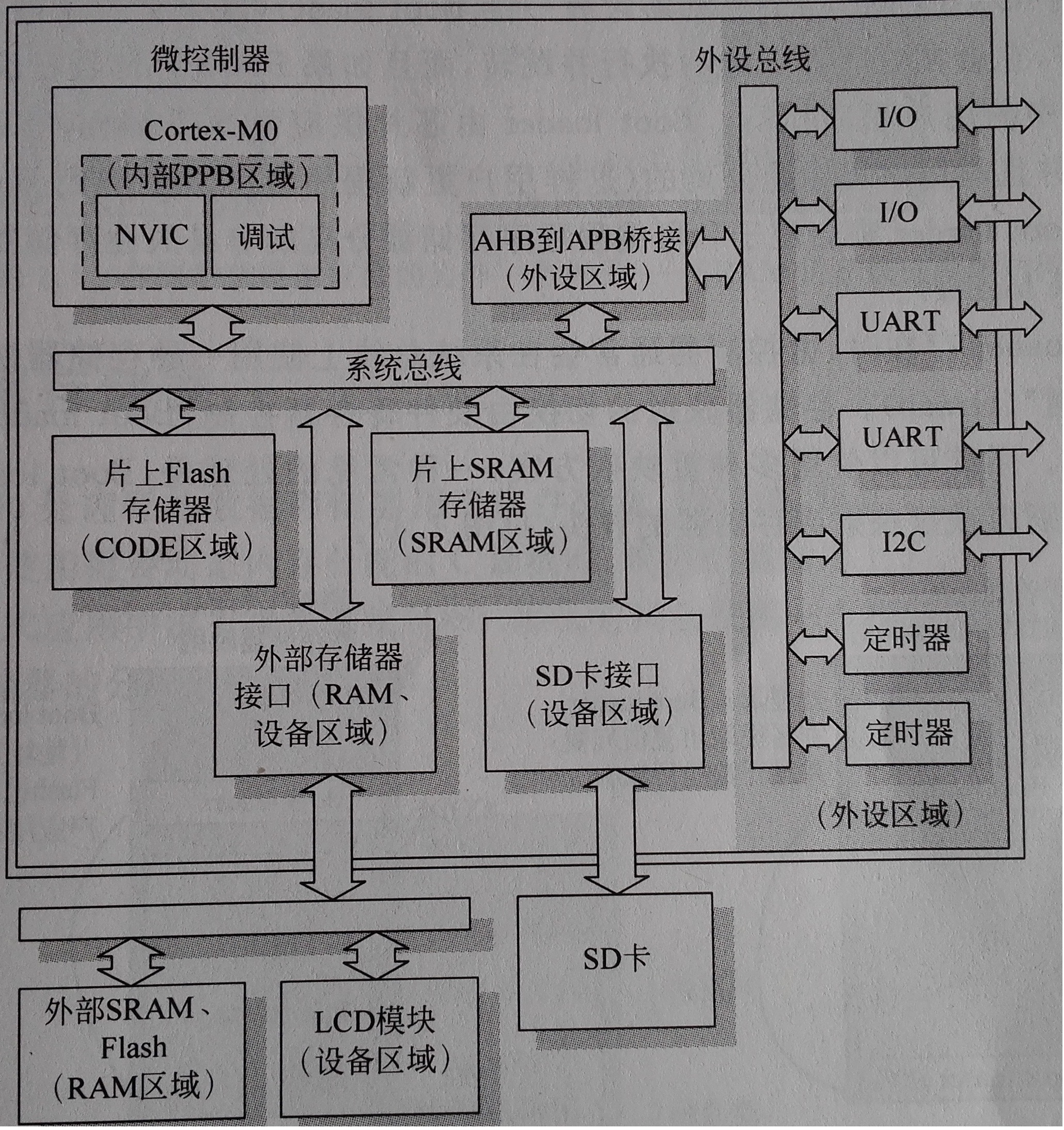

1. Cortex-M0 的两种总线协议:

1)AHB_Lite 系统总线协议:32位地址线,高速高性能访问(Flash, SRAM,总线桥,外部存储器接口)

2)APB 外设总线协议: 32位, 外设等较慢设备通讯(I/O,Timer, UART, Watch Dog。)

系统总线和外设总线是相互分离的,两种总线通过总线桥连接通讯,时钟频率控制不同,可能有多个外设总线段,并且每个段运行在不同的时钟频率下。有些高速外设是直接连接在AHB_Lite系统总线上的。

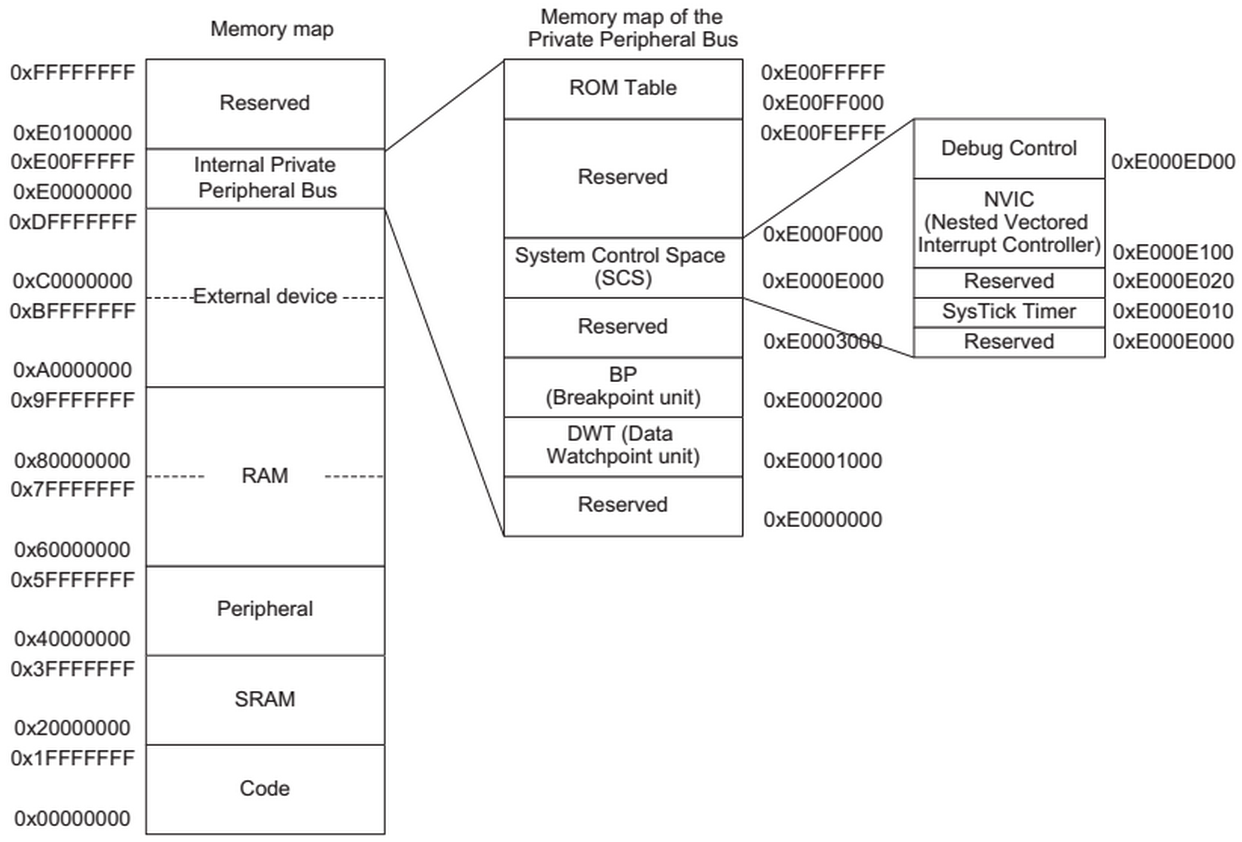

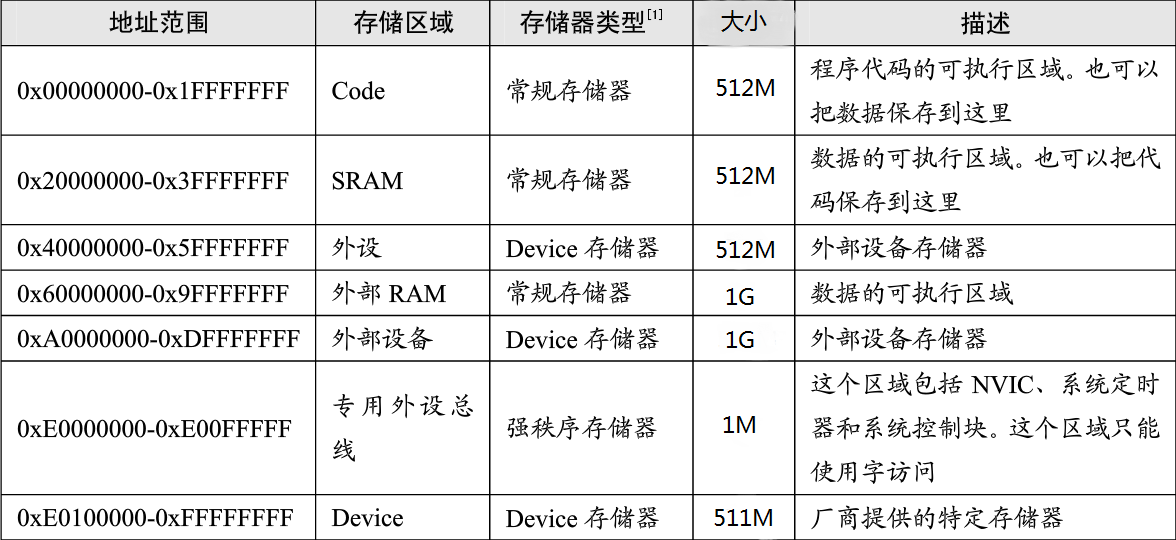

2. 存储器映射(4GB地址空间)

Cortex-M0(+)处理器的4G存储空间从架构上被分为多个区域。总的被分成8个大部分,每个部分512M。

Cortex-M0处理器架构定义的存储器映射

虽然映射已经被架构预先定义,但是实际分配却是很灵活的。

存储器设计的一个例子:

3. 程序存储器(Flash),B

本文详细介绍了ARM Cortex-M0的存储器系统,包括AHB_Lite和APB总线协议,存储器映射的4GB地址空间划分,程序存储器(Flash)与Bootloader的功能,数据存储器(SRAM)的使用,以及小端和大端模式的处理。同时,讨论了存储器属性如可执行、可缓冲、可缓存和可共享的特性。

本文详细介绍了ARM Cortex-M0的存储器系统,包括AHB_Lite和APB总线协议,存储器映射的4GB地址空间划分,程序存储器(Flash)与Bootloader的功能,数据存储器(SRAM)的使用,以及小端和大端模式的处理。同时,讨论了存储器属性如可执行、可缓冲、可缓存和可共享的特性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6144

6144

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?