文章目录

-

- ARM处理器类型

-

- Cortex-A系列

- Cortex-R系列

- Cortex-M系列

- SecurCore系列

- Classic系列

- Cortex-M系列处理器的特点

- ARM架构之间的关系

- Cortex-M0处理器的性能

- Cortex-M0处理器结构

-

- 处理器内核

- 嵌套向量中断控制器

- 总线系统

- 调试子系统

- 唤醒中断控制器

- Cortex-M0处理器寄存器组

-

- 通用寄存器组

- 特殊寄存器

-

- 组合程序状态寄存器(xPSR)

-

- APSR

- IPSR

- EPSR

- 中断屏蔽特殊寄存器

- 特殊寄存器(CONTROL)

- Cortex-M0存储器空间映射

- Cortex-M0程序镜像原理及生成方法

- Cortex-M0的端及分配

- Cortex-M0处理器异常及处理

-

- 异常原理

- 异常优先级

- 向量表

- 异常类型

-

- 复位

- 不可屏蔽中断NMI

- 硬件故障(HardFault)

- 请求管理调用(SVCall,SuperVisor Call)

- 可挂起的系统调用(PendSV)

- 系统滴答(SysTick)

- 外部中断

ARM处理器类型

ARM 处理器采用的是精简指令集 (Reduced Instruction Set Computing,RISC)处理器架构。RISC 架构的特点包括:

- 在功耗,尤其是低功耗方面优势明显。

- 这种架构已经被广泛的应用在移动设备中,比如: 智能电话和平板电脑中。

- 这种架构具有良好的生态系统支持,生态系统包括:技术文档、设计参考、驱动程序代码,以及不同的操作系统。对于设计用户来说,很容易找到相关的设计资源。

目前,ARM 处理器主要分为 Cortex-A、Cortex-R、Cortex-M、SecurCore 和 Classic 几大类

Cortex-A系列

该系列处理器也称为应用处理器,该系列属于高性能处理器,可使用各种开放的操作系统,比如 Linux。Cortex-A 系列处理器主要应用于智能电话、数字电视、智能书、家用网关等。

Cortex-R系列

该系列处理器也称为实时处理器,基于该处理器在异常事件处理方面的性能,它主要用于实时方面的应用,包括:汽车刹车系统、动力装置等。.

Cortex-M系列

该系列处理器主要应用于对价格比较敏感,也就是低成本的场合,比如:微控制器、混合信号设备、智能传感器、汽车电子和安全气囊。

SecurCore系列

该系列处理器主要应用于对安全性要求较高的场合。

Classic系列

该系列是以前传统的处理器架构,包括ARM7、ARM9 和ARM11等。

Cortex-M系列处理器的特点

Cortex-M 系列处理器包括: Cortex-M0、Cortex-M0+、Cortex-M1、Cortex-M3、Cortex-M4、

Cortex-M7,该系列处理器的特点主要包括:

- 该系列处理器主要应用于低功耗,以及对电池续航能力要求较高的场合。

- 该系列处理器结构相对简单,所消耗的晶圆面积较少,因此该系列处理器封装体积较小。

- 通过 Keil uVision 集成开发环境,可以迅速完成软件应用程序的开发,以及实现设计代码的重用。·

Cortex-M0的ARM架构为ARMv6-M,内核架构为冯诺依曼架构,包含大部分的Thumb和Thumb-2子集,硬件乘法为1或者32个周期,无硬件除法,无饱和数运算,无DSP扩展,无浮点

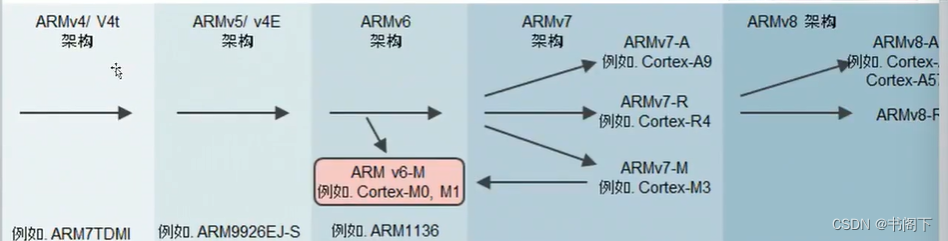

ARM架构之间的关系

Cortex-M0处理器的性能

Cortex-M0处理器是Cortex-M 系列处理器中结构和功能最简单的一个处理器,其性能和特点主要包括:

- 采用32位RISC架构的处理器。

- 采用冯诺依曼架构,即:指令和数据共享一个总线接口。

- 当使用 Cortex-M0处理器的最小配置时,构成该处理器大约只消耗 12,000 个逻辑门资源。

- 该处理器支持绝大部分的16位Thumb-1 指令和某些32位Thumb-2 指令。

- 采用了90nm低功耗制造工艺。当使用Cortex-M0的最小配置时,功耗仅为16uw/MHz。

- 该处理器指令集包含 56 条指令,提供对C语言的友好设计框架 CMSIS。

- 该处理器采用ARMv6-M 架构。

- 该处理器支持一个不可屏蔽中断(NMI)和1~32个物理中断。

- 提供休眠模式。

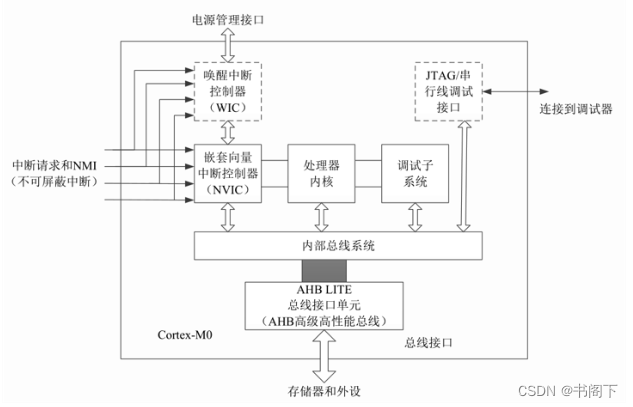

Cortex-M0处理器结构

Cortex-M0微处理器内部结构,ARM Cortex-M0微处理器包括:处理器核、嵌套向量中断控制器 (Nested VectorInterrupt Controller,NVIC)、调试子系统、唤醒中断控制器 (WakeupInterrupt Controller,WIC)、AHB LITE 总线接口以及连接这些单元的内部总线系统。下面对这些单元进行详细说明:

处理器内核

处理器核是 Cortex-M0最核心的功能部件,它负责对数据进行处理。

- 该处理器包含内部寄存器、算术逻辑单元(ALU)、数据通路和控制逻辑

- 该处理器核内部用于取指、译码和执行指令的指令通道采用三级流水结构

嵌套向量中断控制器

专用的 NVIC用于对中断进行管理,并且向处理器核发出中断请求信号。

- 包含最多32个中断请求信号,以及1个不可屏蔽中断。

- 自动处理嵌套中断,包括: 比较中断请求之问的优先级、以及当前中断的优先级。

总线系统

总线系统用于将 Cortex-M0内部的各个功能部件连接在一起。总线系统包含:

- 内部总线系统

- 处理器核内部的数据通道

- AHB Lite 接口单元

Cortex-M0总线系统的所有总线均为 32位宽度。

AHB-Lite

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4349

4349

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?