在《ZYNQ-7000使用总结(3)——PS和PL部分配合使用》中我们介绍了一个PS和PL配合使用的例子,在那个例子中我们有加入两个用于调试的IP核:ChipScope AXI Monitor和Chipscope Integrated Controller,这两个IP核用于ChipScope的调试。ChipScope是Xilinx提供的一种硬件调试工具,类似于我们在硬件调试中经常会用到一些逻辑分析仪,这里前一个IP核就相当于逻辑分析仪的探头,可以捕捉AXI总线上的信号;后一个IP和是ChipScope和JTAG的接口,控制AXI Monitor采集信号和给上位机传输数据。关于这两个IP核的配置与连线,前面已经讲过,这里我们以那篇文章里面的例子为例直接开始讲如何使用ChipScope进行硬件调试。

调试步骤

连接开发板,打开SDK,使用先前从PlanAhead里面导出的.bit文件配置FPGA(配置方法前面已经介绍过),然后运行helloworld程序,关闭SDK。接下来打开ChipScope Pro Analyzer,如图:

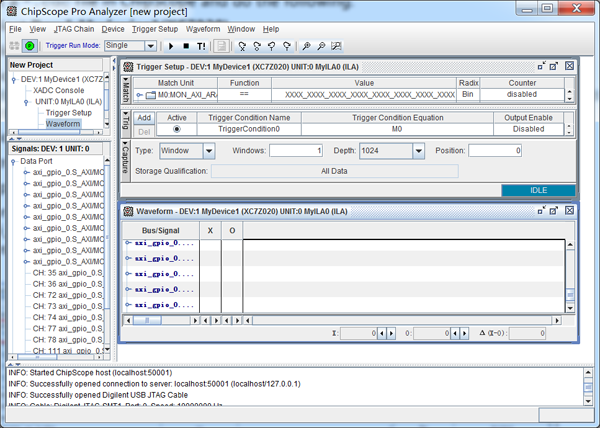

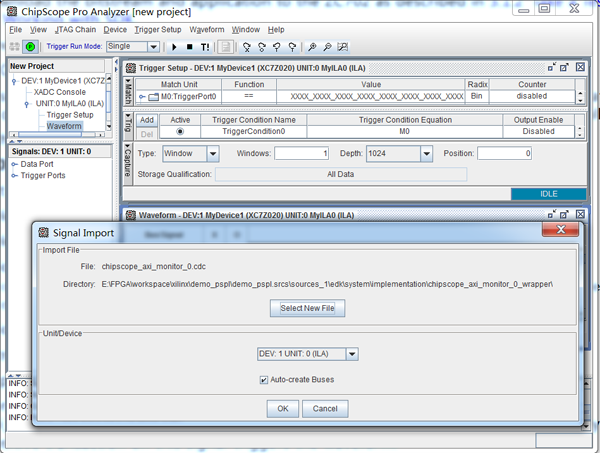

然后点击左上角的黑色按钮,如果JTAG线连接正确,就会自动找到设备,选择下面的Mydevice1(XC7020),点击OK。然后在窗口中选择File——Import,然后去目录

\

.srcs\sources_1\edk\system\implementat

ion\chipscope_axi_monitor_0_wrapper中选择chipscope_axi_monitor_0.cdc文件,点击OK如下图所示:

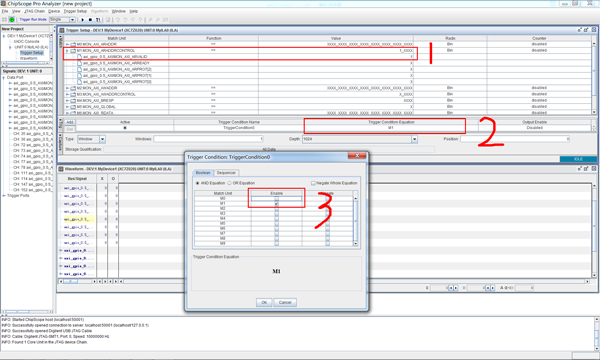

导入cdc文件以后,我们就需要设置触发条件。从上面最后一幅图中我们可以看出设置窗口分为三个部分:第一个是“Math”——该窗口是设置信号匹配窗口,在这里我们可以设置触发的信号要求;第二个是“Trigger Condition”——该窗口是触发条件设置,这里我们可以将匹配信号进行逻辑组合,进而配置成触发条件;第三个是“Capture Settings”——该窗口用于捕捉设置,用于设置捕捉数据的数量等信息。这里,我们在第一个窗口中设置成只要往GPIO写数据就开始捕捉数据,设置方法是在AXI的读控制信号里面找到AWVALID信号,将其设置为1。然后在“Trigger Condition”中选择“Trigger Condition Equation”列中的M0,会弹出一个窗口,勾掉M0,选择M1,点OK。最后再在“Capture Settings”中将Position的值从0改为512。整个设置过程如下图所示:

设置完以后,点击Run按钮运行。然后我们在串口终端里面进行操作,这里就可以看到波形图了。

总结

在ZYNQ开发过程中,软件部分的调试我们直接在SDK中就可以进行,和Eclipse的使用一样,这里就不介绍了。硬件部分的调试使用ChipScope,非常的方便。

5万+

5万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?