1. Altera官网有关PCIe的培训

2. 采用Stratix IV GX FPGA设计PCI Express

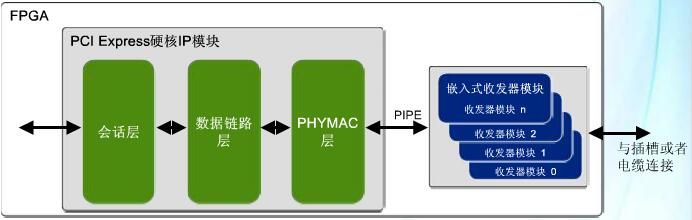

↑ ,PCIe硬核实现了物理层、链路层、传输层,但是,这并不说明这是一个完整的PCIe实现方案。还需要“收发器模块”实现PHY芯片的功能,其通过PIPE接口与PCIe硬核连接,通过插槽与PCIe 背板连接。

↑ , 每个PCIe硬核需要消耗两个收发器模块,可见,收发器模块的Channel和PCIe接口的Lane是一一对应的。

1. Altera官网有关PCIe的培训

2. 采用Stratix IV GX FPGA设计PCI Express

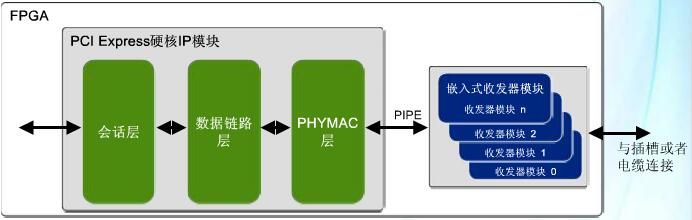

↑ ,PCIe硬核实现了物理层、链路层、传输层,但是,这并不说明这是一个完整的PCIe实现方案。还需要“收发器模块”实现PHY芯片的功能,其通过PIPE接口与PCIe硬核连接,通过插槽与PCIe 背板连接。

↑ , 每个PCIe硬核需要消耗两个收发器模块,可见,收发器模块的Channel和PCIe接口的Lane是一一对应的。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?